Werbung

Wir haben die im Sommer veröffentlichten Daten auch noch einmal zusammengetragen und führen diese an dieser Stelle auf.

[h3]Höhere Single-Threaded-Leistung und verbesserte Cache-Strukturen[/h3]

Vorweg kann bereits festgehalten werden, dass sich AMD beim Konzept der Zen-Architektur sehr dicht an den Vorgaben bewegt, die Intel für die Broadwell-Architektur gemacht hat. Dies wird anhand einiger Punkte deutlich, auf die wir noch genauer eingehen werden. Eine ähnliche Pipeline- und Cache-Anordnungen wie Broadwell, dabei in 14 nm FinFET gerfertigt wie die aktuelle Skylake-Generation bei Intel sind so die grundsätzlichen Züge, an denen wir uns nun abarbeiten werden.

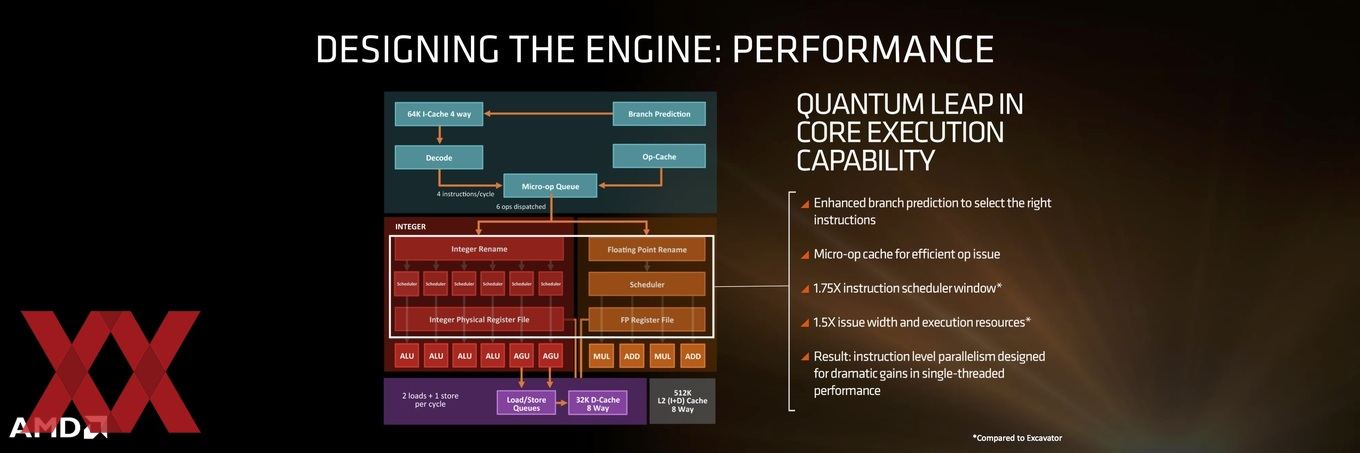

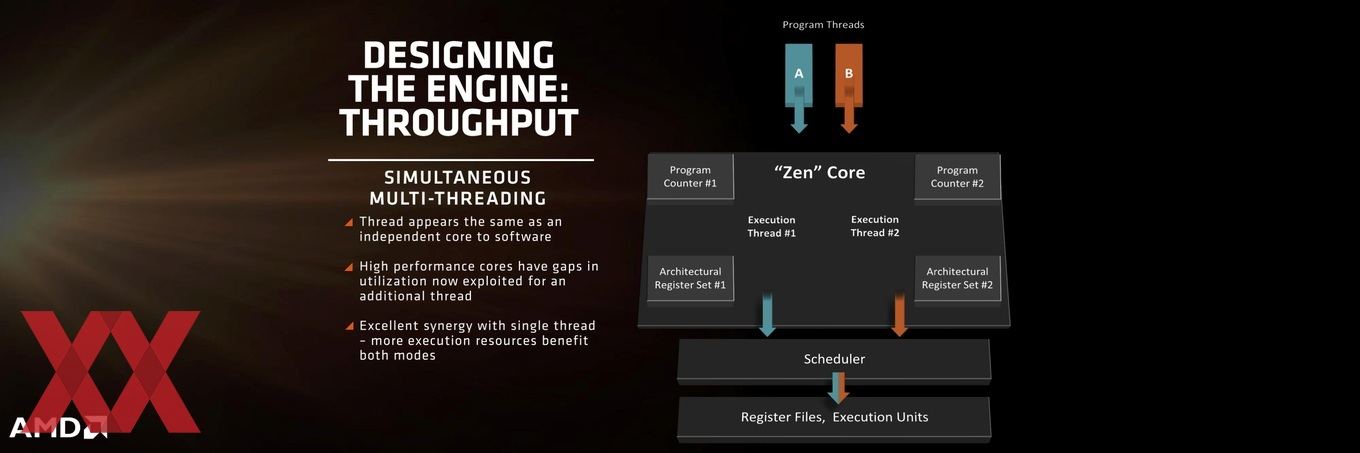

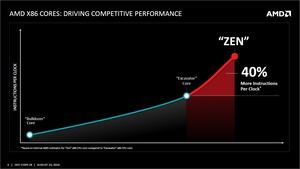

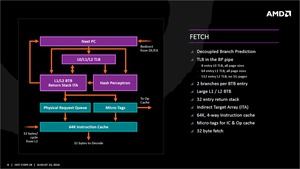

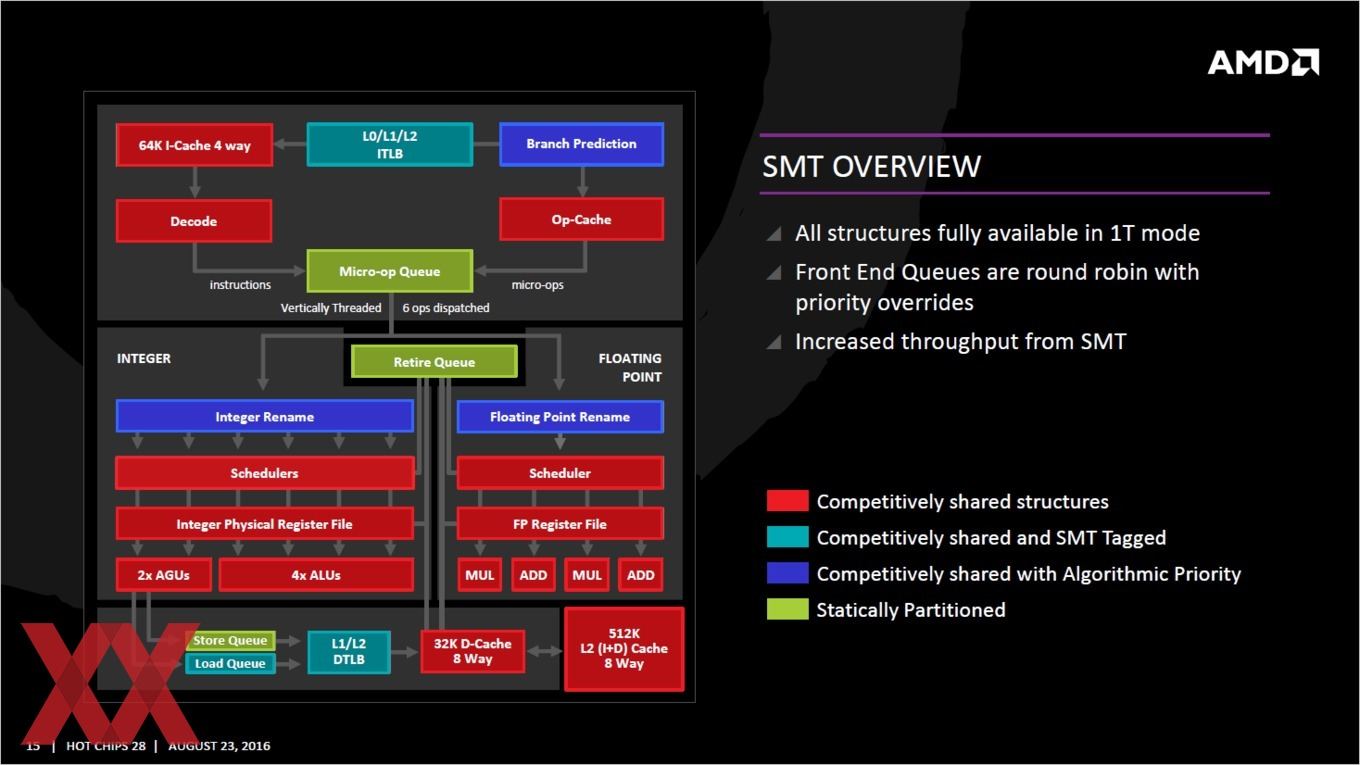

Um eine höhere Single-Thread-Leistung zu erreichen verwendet AMD bei den Zen-Prozessoren nun auch SMT (Simultaneous Multithreading) wie Intel dies tut. Hinzu kommen Optimierungen bei der Branche Prediction, sodass die richtigen Instruktionen zum richtigen Zeitpunkt verwendet werden können. Außerdem verwendet AMD nun einen Micro-Op-Cache im Zusammenspiel mit den drei Cache-Ebenen, die untereinander und miteinander Daten austauschen können, ihre Ressourcen aber auch dediziert bestimmten Rechenaufgaben zur Verfügung stellen. Die Steigerung von 40 % bei der IPC-Leistung setzen sich aus diesen Maßnahmen, aber auch aus einem verbesserten Scheduler sowie einer größeren Bandbreite an Ressourcen für die ausführenden Einheiten zusammen.

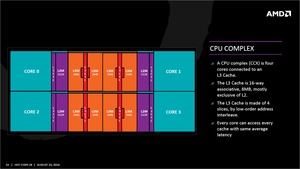

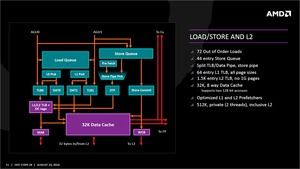

Daten in einem Kern schnell berechnen zu können ist ein wichtiger Punkt, es hilft aber nicht, wenn der Datenaustausch untereinander durch eine zu geringe Interconnect-Architektur beschränkt wird. AMD verwendet daher einen verbesserten Pre-Fetcher und 8 MB an L3-Cache. Ein großer L2-Cache (512 kByte) für Instruktionen und Daten unterstützt diesen Vorgang (AMD nennt aber noch keine Größe für den L2-Cache). Der L1-Cache mit seinem Instruktions- (64 kByte) und Datenanteil (32 kByte) wurde ebenfalls hinsichtlich der Latenz beschleunigt. Letztendlich will AMD die Cache-Bandbreite um den Faktor fünf im Vergleich zu Bulldozer verbessert haben.

Diese interne Cache-Struktur tauscht Daten innerhalb eines Kernes zwischen dem L1- und L2-Cache mit 32 Byte pro Taktzyklus aus. Im Falle von Instruktionen verlaufen diese nur vom L2- in den L1-Cache. Daten müssen natürlich auch zwischen diesen beiden Caches hin und her ausgetauscht werden. Die 32 Byte pro Taktzyklus sind hier als bidirektional angelegt. Zwischen dem L2- und dem L3-Cache erfolgt der Austausch ebenfalls mit 32 Byte pro Taktzyklus und auch hier bidirektional.

Neben der internen Struktur spielt die Verwendung von SMT eine wichtige Rolle bei der Steigerung der IPC-Leistung – wie bereits erwähnt. SMT funktioniert wie bei den Intel-Prozessoren in der Form, dass die Software einen physikalischen Kern in Form zweier logischer Kerne sieht, auf denen zwei Threads ausgeführt werden können. AMD hat sich die Funktionsweise weitestgehend bei Intel abgeschaut, was ja auch kein Fehler oder falsch sein muss.

[h3]Gesteigerte Effizienz durch Fertigung und Architektur[/h3]

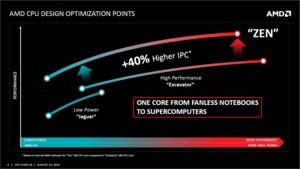

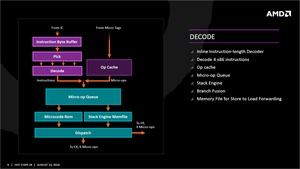

So viel zur Leistung, doch die höhere Effizienz erreicht AMD auch durch Einsparungen beim Verbrauch und dies durch Verbesserungen in der Architektur und nicht nur in der Fertigung. Hier spielt ein Clock Gating eine wichtige Rolle, denn verschiedene Bereiche des Prozessors können mit unterschiedlichen Taktraten und damit Spannungen betrieben werden. Hinzu kommen ein Write Back L1-Cache, der Micro-Op-Cache und eine Stack Engine, die dann eingreifen, wenn Daten und Berechnungen möglichst energiesparend durchgeführt werden sollen. Insgesamt zielt die Organisation darauf ab, möglichst wenig Daten und Instruktionen (unnötig) schreiben und lesen zu müssen.

Die Steigerung der Effizienz erreicht AMD aber auch durch die Fertigung in 14 nm FinFET. Diese erfolgt bei GlobalFoundries. Für die Zukunft sieht AMD hier noch weiteres Verbesserungspotenzial. GlobalFoundries hatte zuletzt sogar angekündigt, den-10-nm Prozess komplett zu streichen und direkt auf 7 nm gehen zu wollen.

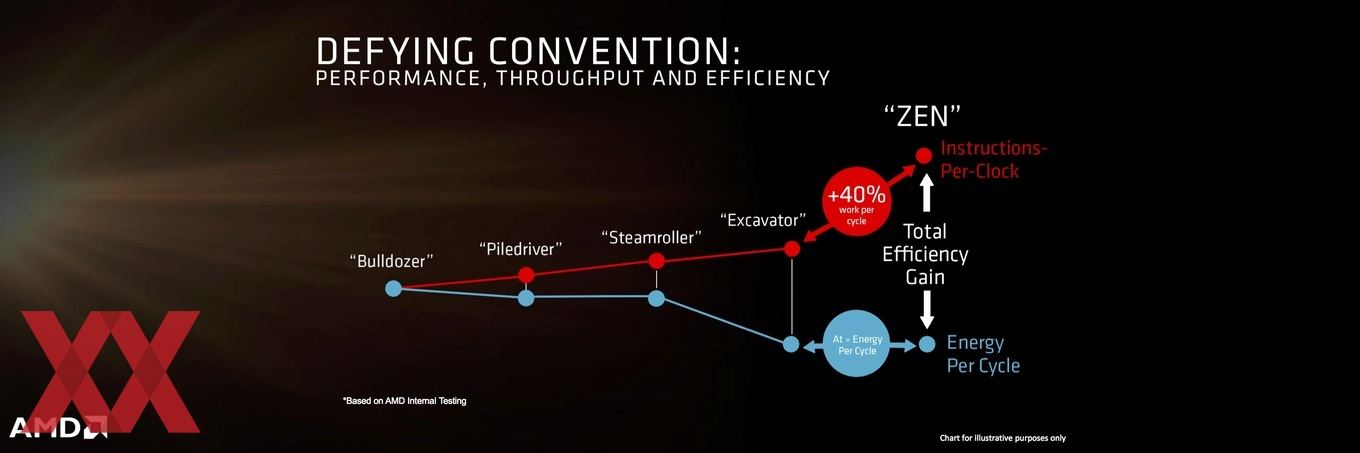

AMD vergleicht die für die Zen-Architektur gemachten Anstrengungen mit den eigenen Architekturen wie Bulldozer, Piledriver, Steamroller und Excavator und sieht sich gut aufgestellt. Doch die Zen-Architektur soll nur der erste Schritt sein und auch wenn die ersten Produkte erst in rund sechs Monaten verfügbar sein werden, spricht AMD bereits davon mit Zen+ weitere Fortschritte machen zu wollen.

Doch es gibt noch einige weitere Neuerungen. Da wäre zunächst einmal der Micro-Op-Cache, der in der Zen-Architektur eine der wichtigsten Neuerungen darstellt. Bereits dekodierte Code kann hier abgelegt werden und wird in der Folge in die Micro-Op-Queue überführt. Leider gibt AMD nicht an, wie groß der Micro-Op-Cache und die Queue sind. Um die Queue zu entlasten wird eine Erkennung von Schleifen versucht. Wird oder werden eine Schleife erkannt, wird diese ausgekoppelt und direkt an das Frontend gehängt.

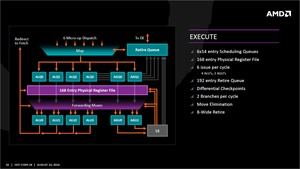

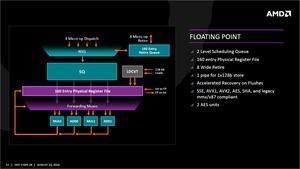

Nach diesem Teil unterscheidet sich die Pipeline nun wieder etwas deutlicher von der von Intel. Während Intel einen gemeinsamen Reorder Buffer für Integer- und Gleitkommaoperationen verwendet, trennt AMD diese nach dem Dispatcher auf. Aufgrund der unterschiedlichen Gewichtung können sechs Integer-Instruktionen am Dispatcher verarbeitet werden und vier Gleitkomma-Instruktionen. In den dazugehörigen Registern ist mit 168 Integer- und 160 Gleitkommarestigerplätzen ausreichend Platz vorhanden.

Die Gleitkommaberechnungen werden auf zwei 128 Bit FP-MUL- und zwei FP-ADD-Einheiten durchgeführt. Bei Bedarf können diese zu einem 256 Bit AVX2 zusammenschaltet werden. Derzeit ist noch unklar, ob bei AMD FMA (Fused Multiply Add) pro Takt ausgeführt werden kann. Intel verwendet bei Haswell sogar zwei dieser Einheiten. Sollte dies bei AMD nicht der Fall sein, dürfte Zen bei entsprechenden Anforderungen eher auf Sandy-Bridge-Niveau liegen anstatt so schnell wie Haswell zu sein.

Die Details zu den Caches hatte AMD schon teilweise verraten, führt diese nun aber noch einmal etwas genauer aus. Der L1-Cache ist insgesamt 96 kB groß, teilt sich aber zu 64 kB in Instruktionen und 32 kB in Daten auf. Damit ist zumindest der Instruktionen-Anteil doppelt so groß wie bei Skylake, während der Daten-Anteil die identische Größe hat. Wieder doppelt so groß ist der L2-Cache mit 512 kB. Wichtig ist aber nicht nur die Größe, sondern auch die Geschwindigkeit der Caches. L1- und L2-Cache sollen etwa doppelt so schnell sein, während der L3-Cache sogar um den Faktor fünf zulegen soll.

Um den Aufbau und dessen Beschreibung zu vereinfachen führt AMD eine neue Einheit ein: Den CPU Complex. Ein CPU Complex besteht dabei aus vier Kernen mit den L1- und L2-Caches sowie zwei Cache-Segmenten zu jeweils 1 MB pro Kern – also insgesamt 8 MB im CPU Complex. Eine CPU aus einem CPU Complex wird mit dem Codenamen Zeppelin bezeichnet und besitzt neben dem CPU-Anteil auch noch zwei DDR4-Speicherkanäle und 32 PCI-Express-Lanes. Allerdings stammen diese Informationen aus unbestätigten Quellen und Leaks. AMD hat sich bisher noch nicht zum Uncore-Part der Zen-Architektur geäußert.

Die Naples-CPU kommt mit 32 Kernen auf vier Zeppelin-Dies, die zusammengepackt und via weiterentwickeltem HyperTransport miteinander verknüpft sind. Entsprechend dürften hier 128 PCI-Express-Lanes und acht DDR4-Speicherkanäle zur Verfügung stehen. Über mehr als 5.000 Pins wird der Prozessor mit dem Sockel verbunden. Derartige Details sind aber noch nicht offiziell von AMD bestätigt worden. Zu einem späteren Zeitpunkt will man sich zu einzelnen Modellen, deren Takt und Anzahl der Kerne äußern.

Soweit zu dem, was AMD bereits im Sommer veröffentlicht hat. Eine genaue Einschätzung von Zen ist und bleibt schwierig. Zwar hat AMD nun schon recht viele Informationen verraten, bevor die erste unabhängigen Tests aber nicht das bestätigen können, was AMD auf der Bühne zeigt, sind wohl auch die wenigsten davon überzeigt, dass die Zen-Architektur der große Wurf für AMD wird, den man sich selbst wünscht.

Die beiden neuen Benchmarks zeigen allerdings, dass AMD zumindest aufgeschlossen hat. Mit einigen Optimierungen kann man die Broadwell-E-Generation von Intel vielleicht sogar schlagen. Vieles wird aber auch davon abhängen, wie Intel weitermacht und was Kaby Lake zu leisten im Stande ist.