Werbung

Im kalifornischen Cupertino findet in jedem Jahr die Hot Chips statt. Auch in diesem Jahr gaben zahlreiche Unternehmen wieder einen Einblick in die aktuellen Entwicklungen im jeweiligen Bereich. AMD sprach über die Vega-Architektur, Intel über die Weiterentwicklung bei den Xeon-Phi-Beschleunigern, Google über den Einsatz von GDDR5 oder HBM für die TPU und IBM über den z14 mit massiv viel Cache. Wir haben eine kleine Zusammenfassung zu einigen der Vorträgen mit den dazugehörigen Präsentationen. Auf einige weitere Punkte gehen wir noch in gesonderten Berichten ein.

AMD legt den Fokus auf Virtualisierung und Kryptowährungen

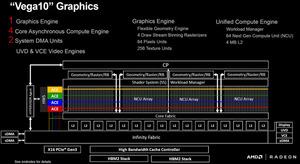

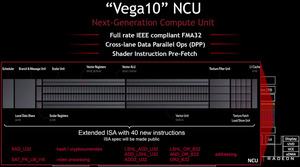

AMD stellte auf der Hot Chips die Vega-Architektur noch einmal ausführlich vor. Wir sind im Rahmen der Berichterstattung zur Radeon RX Vega 56 und Vega 64 bereits genauer darauf eingegangen. Den Fokus legte AMD dabei auf zwei Funktionen, die bisher zumindest im Falle der Virtualisierung noch recht wenig beachtet wurden.

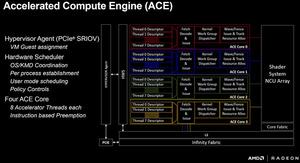

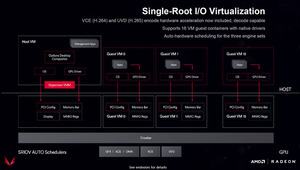

Die Vega-Architektur kann im Falle der Vega-10-GPU mit SR-IOV (Single Root I/O Virtualization) bis zu 16 virtuelle Umgebungen virtualisieren. Die Compute- und Speicher-Ressourcen der GPU werden dabei dynamisch zugeteilt. Neben der Anzahl der VMs spielt aber vor allem das Lizenzierungsmodell eine entscheidende Rolle. Anders als bei NVIDIA fallen keinerlei Gebühren an, so dass mit jeder professionellen Karte mit Vega-GPU die Virtualisierung auch ohne Zusatzkosten verwendet werden kann. Auf der Siggpraph zeigte AMD das Project 47. Dabei handelt es sich um ein komplettes Rack aus 20 Epyc 7601 und 80 Radeon Instinct MI25. Diese 80 Karten können jeweils 16 VMs erstellen, so dass theoretisch 1.280 virtuelle Nutzer darauf arbeiten können.

Neben der Virtualisierung spielten bei AMD und der Präsentation der Vega-Architektur aber auch die speziellen Instruktionen in der Vega-ISA eine wichtige Rolle. Dabei wies AMD noch einmal darauf hin, dass Vega dedizierte Instruktionen für das Hashing von Kryptowährungen besitzt. Viele Spieler sehen das durchaus kritisch, denn die Preise der Karten sind durch den Aufschwung in diesem Bereich stark gestiegen. Darüber hinaus gab es keinerlei Neuheiten zur Vega-Architektur.

Intel Xeon Phi Knights Mill marschiert in Richtung Machine Learning

Intel fährt im Compute-Bereich derzeit zweigleisig. Während die Xeon-Phi-Modelle für das General Computing vorgesehen sind, arbeitet Intel für den Deep-Learning- oder Machine-Learning-Bereich mit einigen Aufkäufen zusammen und entwickelt Chips mit dedizierten FPGAs.

Auf der Hot Chips zeigte Intel allerdings, dass auch die nächste Xeon-Phi-Generation in der Lage sein wird, Machine-Learning-Anwendungen zu beschleunigen. Dazu hat man einige Maßnahmen vorgenommen. Zunächst einmal wurde das Speicherlimit auf 384 GB verdoppelt. Unterstützt wird DDR4-2400 über sechs Speicherkanäle und weiterhin vorhanden sind 16 GB MCDRAM auf dem Chip selbst. Für die Anbindung stehen 36 PCI-Express-3.0-Lanes zur Verfügung.

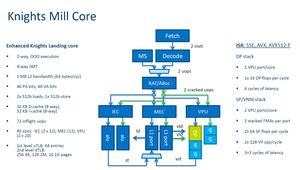

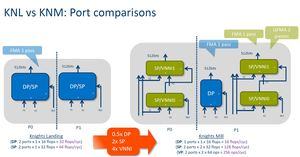

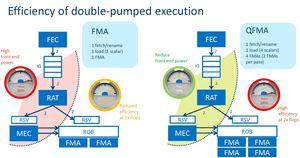

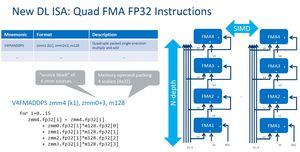

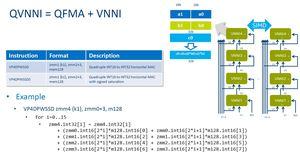

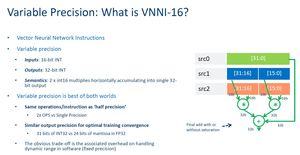

Knights Mill wird aus bis zu 36 Tiles bestehen, die über ein 2D-Mesh miteinander verbunden sind. Pro Tile stehen zwei Kerne zur Verfügung, die sich 1 MB an L2-Cache teilen. Pro Kern können vier Threads verarbeitet werden. Insgesamt stehen also 72 Kerne und 288 Threads zur Verfügung. Für Deep-Learning-Anwendungen hat Intel einige Instruktionen hinzugefügt, welche die dazugehörigen Berechnungen beschleunigen sollen. In der Präsentation spricht Intel von einer Beschleunigung um den Faktor vier.

Im vierten Quartal will Intel mit der Auslieferung der ersten Knights-Mill-Beschleuniger beginnen. Dann wird es wohl auch weitere technischen Daten zu den einzelnen Modellen geben.

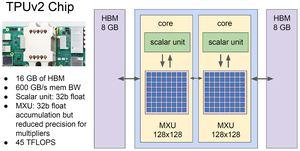

Google TPU mit HBM deutlich schneller

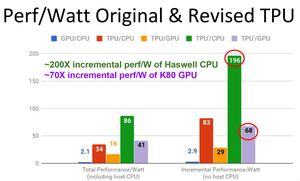

Wie jedes in diesem Bereich aktive Unternehmen hat auch Google in die Entwicklung eigener Hardware für Deep-Learning-Anwendungen investiert. Die erste Generation der TPU (Tensor Processing Unit) kann als ASIC bereits einen deutlichen Schub bei der Rechenleistung verbuchen. Die zweite Generation stellte Google in diesem Jahr vor und versprach noch einmal einen deutlichen Geschwindigkeitszuwachs.

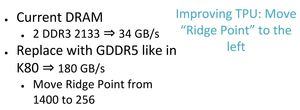

Während die erste Generation noch auf DDR3-Speicher zurückgreifen musste, galt es für Google bei der zweiten Generation zu entscheiden, ob GDDR5 als Speicher ausreichend ist oder HBM eingesetzt werden muss. Mit in Betracht gezogen werden muss dabei nicht nur die Rechenleistung, sondern auch die Leistung pro Watt. Letztendlich hat sich Google aber dazu entschieden, HBM zu verwenden. Durch den Einsatz von HBM hat man eine Leistungssteigerung und eine Verbesserung der Effizienz erreicht.

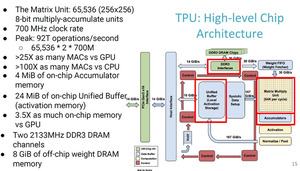

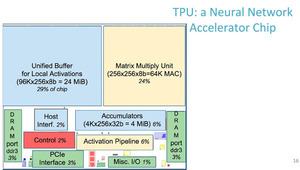

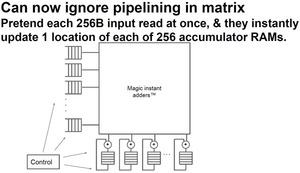

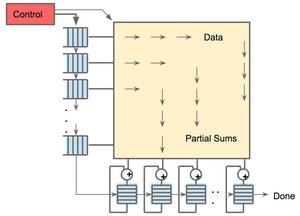

Die neue TPU kann auch Floating-Point-Operationen ausführen. In 16-Bit-Berechnungen kommt die TPU 2 damit auf 180 TFLOPS. Die erste Generation erreicht mit Hilfe einer Matrix aus 256 × 256 Multiplizier/Aufaddier-Einheiten (Multiplier/Accumulator, MAC) und einem Takt von 700 MHz eine Rechenleistung von 91,75 TOPS (Tera Operations per Second). Damit gemeint sind 8-Bit-Operationen für das Inferencing. Die zweite Generation soll auch das Training von Deep-Learning-Netzwerken ermöglichen.

IBM z14: Zehn Kerne und sehr viel Cache

Bereits im Juli stellte IBM den z14 vor. Dabei handelt es sich um einen Prozessor mit zehn Kernen und 30 MB Cache pro Kern. Auf der Hot Chips hat man nun weitere Details öffentlich gemacht. So besteht ein Rack nicht aus mehreren gleichen Prozessoren, sondern IBM passt den z14 entsprechend an. In einem solchen Rack kommen sechs CP- (Central Processor) und ein SC-Chip (System Controller) zum Einsatz. Vier Racks werden zu einem Mainframe.

Jeder Prozessor arbeitet mit einem Takt von bis zu 5,2 GHz. Wie bereits in der Überschrift erwähnt, verbaut IBM massiv viel Cache. Dazu gehören jeweils 128 kB an Instruction und Date L1-Cache sowie 2 bzw. 4 MB an Instruction und Data L2-Cache. Weiterhin vorhanden sind 128 MB an L3-Cache. Je nach Last kann ein solcher Prozessor eine TDP von 500 W aufweisen. Daher kommt auch ausschließlich eine Wasserkühlung in Frage. Jedem Prozessor können bis zu 32 TB an Speicher zur Seite gestellt werden. Hinzu kommen 1,5 bis 6 TB an IBM Virtual Flash Memory. Für solche Systeme extrem wichtig sind natürlich auch die Interconnects und hier stehen mehrere Optionen zur Verfügung. Unterstützt wird zum einen die aktuelle InfiniBand-Generation. Hinzu kommen zum anderen Netzwerkverbindungen bis hin zum Standard 1000-BaseT mit 1.000 GBit/s.

Ein paar Anmerkungen zur Fertigung. IBM lässt in 14 nm (14HP-SOI) bei Global Foundries fertigen. Ein z14 kommt auf 696 mm² und besteht aus 6,1 bzw. 9,7 Milliarden Transistoren – je nachdem, um welches Modell es sich handelt.

Als Betriebssystem kommt beim IBM z14 ein z/OS V2.3 zum Einsatz. Angaben zum Preis gibt es nicht, da solche Systeme sehr individuell für den Kunden zugeschnitten werden