Werbung

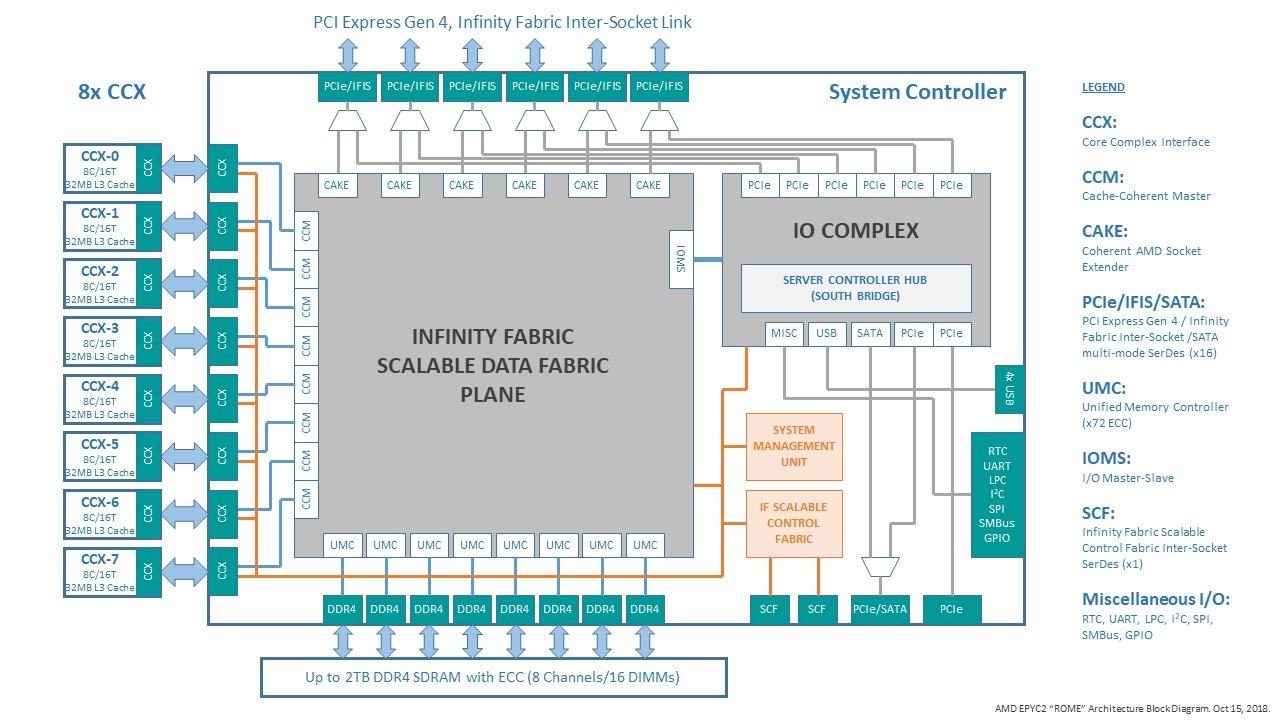

Auf dem New-Horizon-Event stellt AMD seine EPYC-Prozessoren der zweiten Generation vor. Diese werden bis zu 64 CPU-Kerne bieten – verteilt auf acht Chiplets mit jeweils acht Kernen – gefertigt in 7 nm sowie einem zentralen I/O-Chip, der weiterhin in 14 nm gefertigt wird.

Die wichtigsten technischen Daten kennen wir aber noch nicht. So ist nicht bekannt, wie AMD das Speicherinterface mit acht Kanälen an die einzelnen Chiplets anbinden wird. Unbekannt ist außerdem die genaue Konfiguration der Infinity-Fabric-Interconnects. Auch zu den einzelnen Modellen und deren Taktraten gibt es noch keine offiziellen Informationen, auch wenn ein Supercomputer in Deutschland mit den Rome-Prozessoren ausgestattet werden soll und diese bei 64 Kernen mit bis zu 2,35 GHz arbeiten – so zumindest hat es eine Präsentation auf der Supercomputing 2018 verraten.

Die Datenbank von SiSoft Sandra verrät nun Details zum L3-Cache eines Rome-Prozessors mit 64 Kernen. Dieser wird mit "16x 16 MB L3" ausgelesen, was bei acht Chiplets zwei Quad-Core-CCX-Cluster pro Chiplet vermuten lässt. Auf einem Chiplet sind demnach 32 MB L3-Cache vorhanden, insgesamt also 256 MB für einen Prozessor mit acht Chiplets. Bei 16 MB für vier Kerne würde dies im Vergleich zur ersten Generation der EPYC-Prozessoren einer Verdopplung des L3-Caches entsprechen. Ein aktueller AMD Epyc 7601 mit 32 Kernen bietet 64 MB L3-Cache – 8 MB pro CCX bzw. 16 MB pro Zeppelin-Die.

Die Verdopplung des L3-Caches dürfte AMD vor allem dabei helfen, die Daten so lange wie möglich beim jeweiligen Chiplet zu belassen und nicht über den I/O-Die und den angebundenen DDR4 ständig lesen und schreiben zu müssen. Die Kommunikation zwischen den Chiplets, dem I/O-Die und über die Speicherkanäle dürfte kritisch für die Leistung und Effizienz der Rome-Prozessoren sein. Bisher hat sich AMD zu diesem Thema aber noch nicht offiziell geäußert.

Hartnäckig halten sich die Gerüchte, AMD könnte auf dem I/O-Die einen L4-Cache verbauen, um die Relevanz der externe Anbindung weiter zu reduzieren. Ein doppelt so großer L3-Cache würde die Notwendig eines weiteren L4-Caches als Zwischenebene zum Arbeitsspeicher aber weiter reduzieren.