Werbung

Vor wenigen Tagen hat Intel seine Zukunftspläne für die verschiedenen Produktsegmente präzisiert. Und auch wenn das Schiff derzeit ohne CEO fährt, offenbar hat Intel wieder den richtigen Kurs gefunden – zumindest dann, wenn ambitionierte Pläne aufgehen sollten. Wir wollten versuchen, die Ankündigungen einmal etwas einzuordnen.

Über alle Präsentationen und Vorstellungen hinweg wird deutlich, dass der Chipgigant zukünftig flexibler werden will. Dies beginnt mit der Fertigungstechnologie, die bislang an konkrete Produkte gebunden war. Kommt es aber zu Problemen in der Entwicklung einer neuen Fertigung, wie aktuell beim 10-nm-Prozess, ist eine eng an die Fertigung gebundene IP quasi wertlos bzw. kann ihr Potenzial nicht ausspielen. Dies ist einer der Punkte den Intel angehen möchte und dies zeigt sich in den einzelnen Produktsparten auch deutlich.

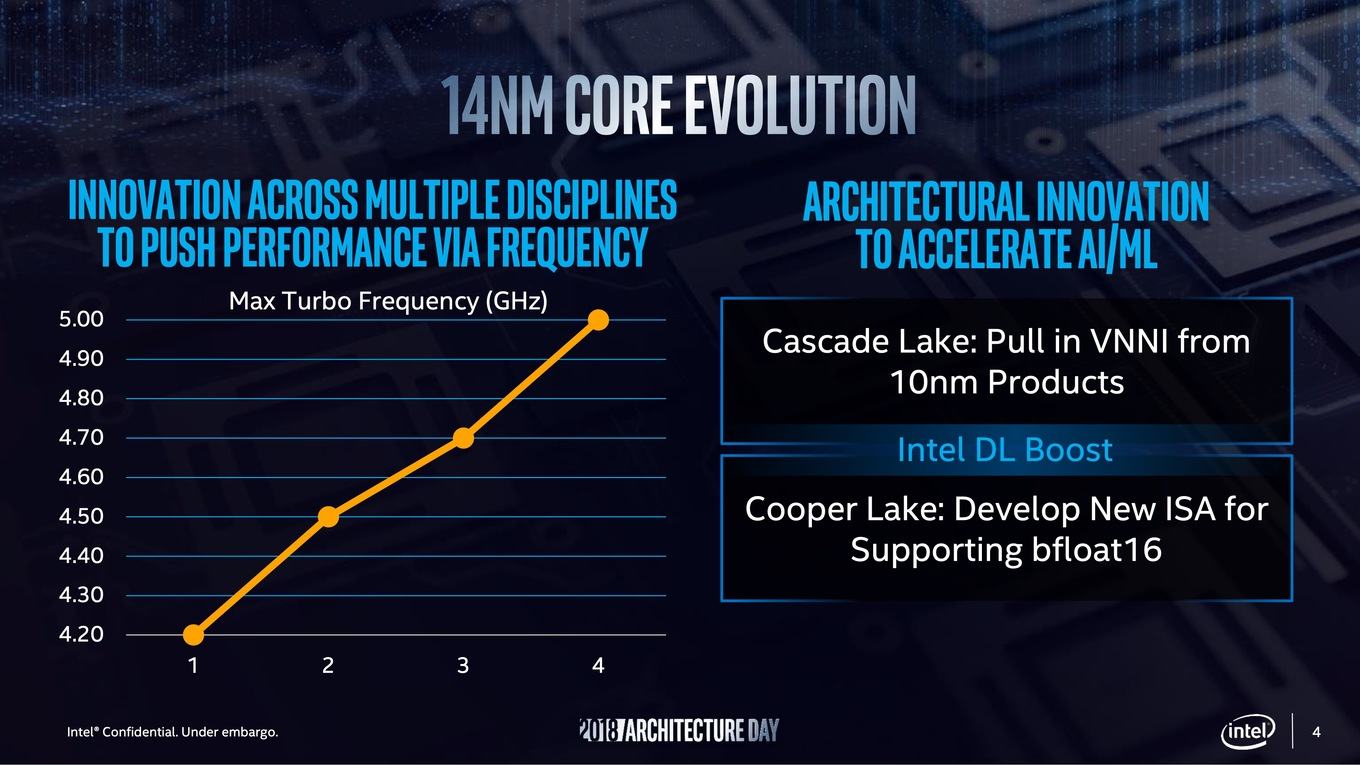

Die ersten Auswirkungen der neuen Strategie werden wir bei den bereits angekündigten Server-Prozessoren Cascade Lake und Cooper Lake sehen. Beide werden noch in einer Strukturbreite von 14 nm vom Band laufen. Um einige der geplanten Weiterentwicklungen nicht zu verlieren, baut Intel in Cascade Lake die neuen VNN-Instruktionen (Vector Neural Net Instructions) ein, die für die ersten 10-nm-Produkte geplant waren. Dies soll der Serverplattform im AI-Segment zu mehr Durchsetzungsvermögen gegenüber den GPU-Beschleunigern verhelfen. Cooper Lake, ebenfalls noch aus der 14-nm-Fertigung, wird mit bloat16 ebenfalls eine ISA-Erweiterung erhalten, die auf die Anforderungen im AI-Compute-Bereich gerichtet ist.

Zugleich wird es neue AVX512-Instuktionen geben, die bei der Inferencing-Leistung, also der Auswertung von Deep-Learning-Netzwerken, hilfreich sind. VPDPBUSD und VPDPBUSDS beschleunigen vor allem INT8- und INT16-Berechnungen und sollen die Inferencing-Leistung gegenüber der Skylake-Architektur ohne diese Instruktionen um den Faktor zwei bis drei erhöhen. Während Cascade Lake auf eine Beschleunigung im Inferencing ausgelegt ist, soll Cooper Lake auch das Training mit Anforderungen an eine höhere Genauigkeit auf ein ähnliches Leistungslevel hieven.

Sunny Cove

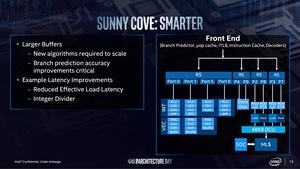

Sunny Cove wird die erste neue Architektur nach der Skylake-Architektur sein. Diese wird zwar noch immer auf den gleichen Grundprinzipien basieren, durch viele kleine Verbesserungen in der Architektur aber einen großen Paradigmenwechsel darstellen.

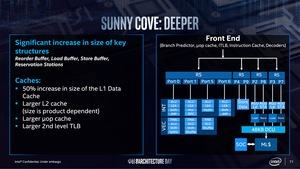

Wie bereits in den Ice-Lake-Gerüchten vermutet, wird Intel den L1-Data-Cache von 32 auf 48 kB vergrößern. Veränderungen soll es außerdem beim L2-Cache geben, der bei Skylake noch 256 kB groß ist. Für Skylake-SP hatte Intel diesen bereits vergrößert und so ist davon auszugehen, dass Intel für Sunny Cove ebenso vorgehen wird. Wie groß der L2-Cache bei Sunny Cove nun sein wird, wird wohl vom jeweiligen Einsatzzweck der Architektur – ob nun Core-Desktop-Prozessor oder Xeon-Server-Prozessor – abhängig sein.

Ebenfalls vergrößert wird der µOp-Cache, der bei Skylake 2.048 Einträge beinhalten kann. Wie groß er bei Sunny Cove sein wird, wollte Intel nicht vertraten. Der 2nd Level TLB (Translation Lookaside Buffer) fällt darüber hinaus auch größer aus.

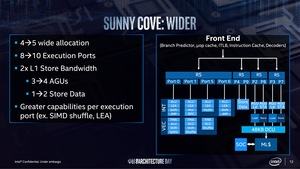

Die geplanten Leistungssteigerungen sind ein Zusammenspiel aus einer veränderten Cache-Hierarchie und einem verbesserten Frontend. Die Anzahl an Execution Ports wird von acht auf zehn erhöht. Diese Maßnahme soll dazu beitragen, dass dem Prozessor mehr Instruktionen durch den Scheduler geliefert werden können, was die Rechenpipeline besser füllen soll. Auf der anderen Seite werden die Flaschenhälse der Skylake-Architektur etwas geöffnet.

Auf dem Weg zum Backend gibt es ebenfalls große Änderungen, die auf den ersten Blick recht unscheinbar sind. Intel führt mit Sunny Cove eine 5-Wide-Out-of-Order-Architektur-Pipeline ein. Hier gibt es nun vier Unified Reservation Station (RS), was es Intel ermöglicht, die Instruktionen paralleler einfließen zu lassen, als bei Skylake. Womöglich auch im den Spectre-Mitigierungen entgegen zu wirken, hat Intel der AGU (Address Generation Unit) vier feste Ports zugewiesen. Jeweils zwei AGUs wird eine Load/Store-Unit zugewiesen. Für VEC- und INT-Berechnungen gibt es nun weitere Recheneinheiten in den jeweiligen Ports. All diese Maßnahmen sollen zur Beschleunigung der Architektur beitragen.

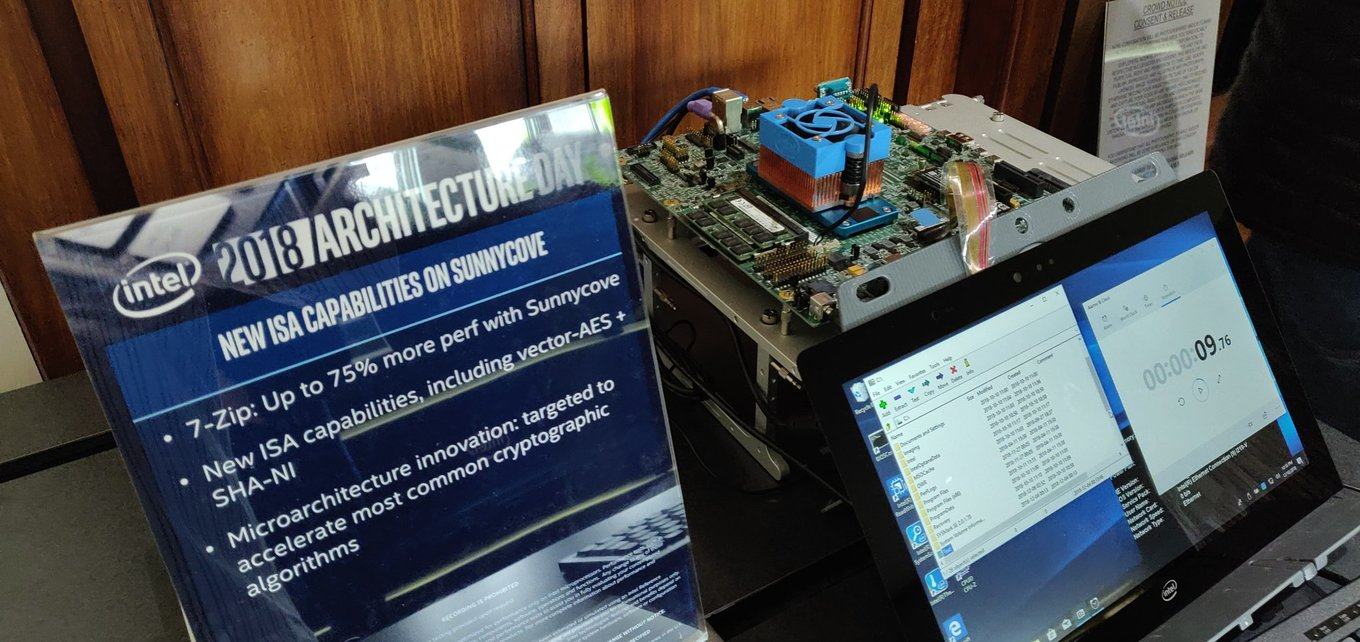

Sunny Cove wird auch neue ISA-Befehlssätze unterstützen. Dazu gehören Vector-AES und SHA-NI, aber auch AVX512. Bei den beiden erstgenannten handelt es sich um Algorithmen zur Hardwarebeschleunigung von Ver- und Entschlüsselungen. Generell soll der Fokus auf der Beschleunigung von Krypthografie-Algorithmen liegen, was wiederum die von Intel angesprochenen Optimierungen bei den speziellen Anwendungen betrifft.

Aufgrund der Erweiterung des Linear Adress Space auf 57 Bit bzw. des Physical Adress Space auf 52 Bit wird ein Prozessor auf Basis der Sunny-Cove-Architektur bis zu 4 TB an Arbeitsspeicher pro Sockel ansprechen können. Bei Skylake-SP und Cascade Lake-AP/SP ist von 3,75 TB im Zusammenspiel aus normalem DDR-Arbeitsspeicher und Optane DC Persistent Memory die Rede. Ice Lake-SP dürfte demnach auch hier eine Verbesserung mit sich bringen.

Der Fokus für Sunny Cove liegt auf einer deutlichen Steigerung der Single-Threaded-Leistung. Die Pipeline der Kerne soll tiefer werden, aber auch mehr Operationen gleichzeitig ausführen können. Die Scheduler sollen aber auch intelligenter werden und Instruktionen besser zusammenfassen und zuordnen können. Der größere L2- und L1-Cache hilft dabei.

Ice Lake als erste Sunny-Cove-Prozessorn

Die ersten Prozessoren auf Basis der Sunny-Cove-Architektur werden die Ice-Lake-Prozessoren sen. Allesamt werden diese im 10-nm-Prozess gefertigt werden und auf dem Architecture Day zeigte Intel auch einen Ice-Lake-SP-Prozessor – man hat also bereits erste Chips aus der 10-nm-Fertigung, die größer als die 100 mm² der Cannon-Lake-Serie sind.

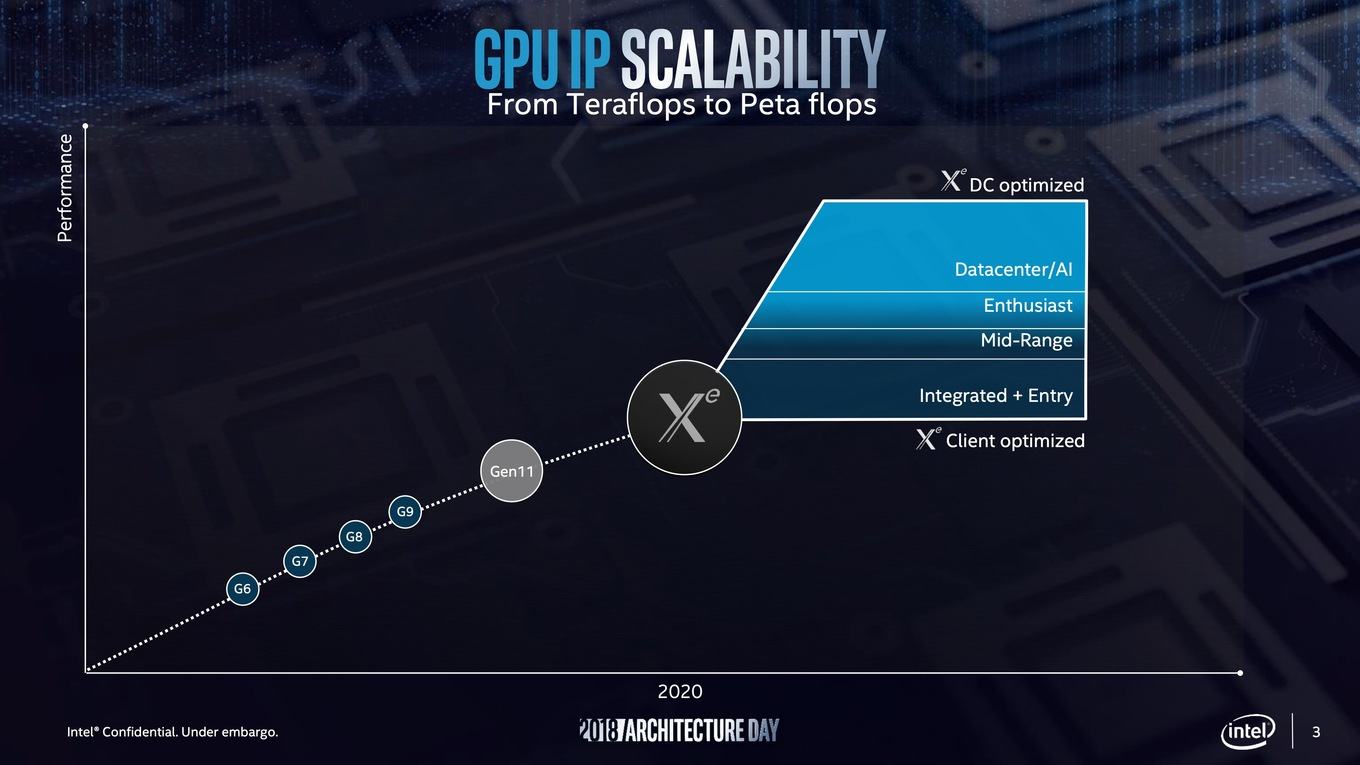

Gen11 nur ein Zwischenschritt zu nächsten GPU-Generation Xe

Der zweite Baustein nach den Prozessoren sind Intels Pläne für zukünftige Grafiklösungen. Hier muss man derzeit zwischen zwei Entwicklungen unterscheiden. Die Gen11-Grafik wird eine kurzfristige Neuerung sein, die bereits im kommenden Jahr ihren konkreten Einsatz in den Ice-Lake-Prozessoren finden wird. Langfristig plant Intel mit der Xe getauften Architektur, die dann im Endkundenbereich, aber auch im Datacenter jeweils über alle Kategorien hinweg skalieren soll.

Gen11-Grafik macht den Anfang

Zunächst einmal aber zielt Intel mit der Gen11-Grafik auf die integrierten Grafikeinheiten. Die als Gen9 und Gen9.5 in den Skylake-, Kaby-Lake- und Coffee-Lake-Prozessoren eingesetzten Grafikeinheiten reichen für einfachste 2D-Anwendungen und sind daher für den Officebereich ausreichend. Auch das ein oder andere Spiel lässt sich damit ausführen, aber es fehlt hier grundsätzlich an Leistung und Komponenten wie einer potenten Video-Engine.

Dies sollte sich bereits mit der Gen10-Grafik und Cannon Lake ändern. Aufgrund der Probleme in der 10-nm-Fertigung ist derzeit bei allen Prozessoren aus der 10-nm-Fertigung die Grafikeinheit deaktiviert. Die Gen10-Grafik wird demnach auf dem Markt keinerlei Rolle mehr spielen und Intel macht direkt den nächsten Schritt zu Gen11.

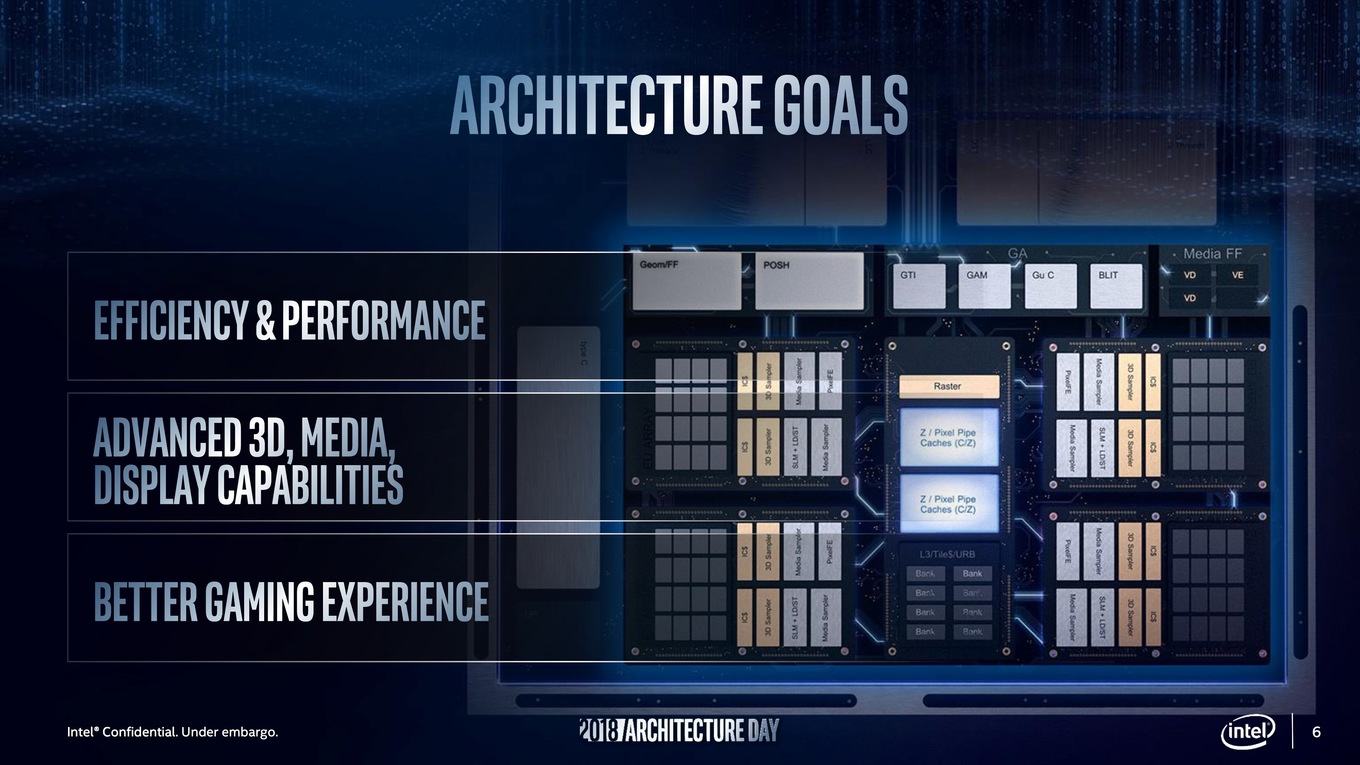

Für die Gen11-Grafik hat sich Intel bereits ambitionierte Ziele gesteckt. Effizienz und Leistung sollen gesteigert werden und auch die angesprochene bessere Unterstützung von hochauflösenden Displays sowie das En- und Decoding von Video spielt hier eine wichtige Rolle.

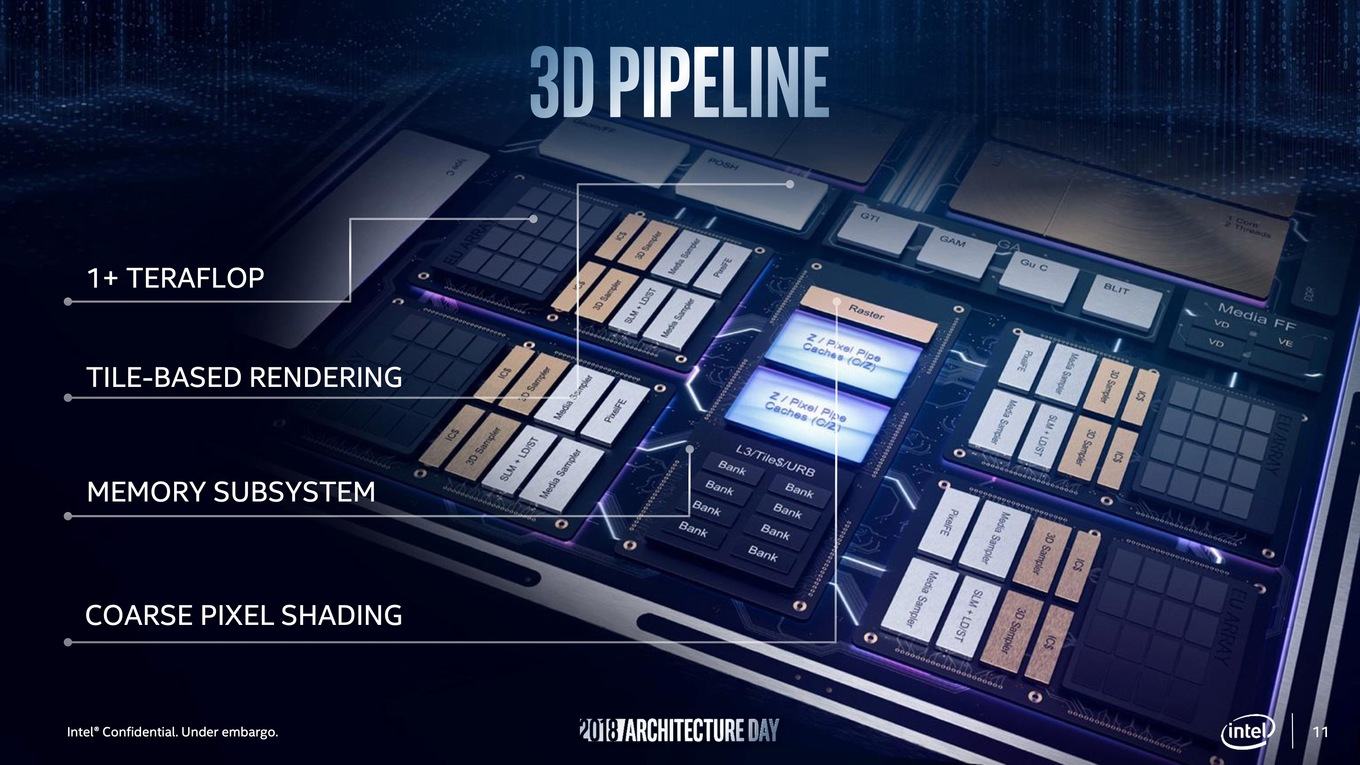

Mit der Gen11-Grafik wird und kann Intel noch nicht am grundsätzlichen Aufbau der aktuellen iGPU-Architektur rütteln. Die bekannten Execution Units (EU) werden aber mit einem neuen Front- und Backend versehen. Es wird ein neues Memory Subsystem geben und die Cache-Hierarchie wird deutlich verändert. Dies wird auch notwendig, schließlich will Intel die GPU von derzeit 28 EUs auf bis zu 64 EUs aufblähen. Diese teilen sich zu vier Slices und jeweils zwei Subslices mit wiederum jeweils 8 EUs auf.

Die Gen11-Grafik von Intel wird ein Tiled Base Rendering unterstützen. Das Tile Based Rendering ist dabei keine neue Erfindung oder eine solche, die sich zuletzt NVIDIA exklusiv zu Eigen machen wollte. Imagination Technology oder ARM wenden das Tile Based Rendering bei den PowerVR- und Mali-Designs schon seit geraumer Zeit an. Das Gegenkonzept zu Tile Based Rendering ist das Immediate Mode Rendering. Dabei wird der Rasterization-Prozess über den kompletten Frame angewendet, während beim Tile Based Rendering der Frame in viele kleine Tiles, also rechteckige Blöcke aufgeteilt und der Rasterization-Prozess durchgeführt werden kann. Typischerweise sind diese Tiles 16x16 oder 32x32 Pixel groß. Diese Parallelisierung kommt den aktuellen GPUs mit mehreren Tausend Shadern natürlich positiv entgegen. Das Immediate Mode Rendering hingegen ist besonders hinsichtlich des Speicherbedarfs recht aufwendig.

Zudem wird man analog zu NVIDIAs Variable Rate Shading (VRS) eine Technik namens Coarse Pixel Shading (COS) einführen, die ähnlich funktioniert und ebenfalls die direkte Unterstützung des jeweiligen Spiels erfordert. Gerade bei eher leistungsschwacher Hardware funktionieren Techniken wie das VRS und COS gut bzw. bieten mit einem Leistungsplus im zweistelligen Prozentbereich einen deutlichen Vorteil.

Auch die Compute-Leistung hat Intel bei der Gen11-Grafik im Hinterkopf und verbessert die Effizienz der Grafikpipeline durch einen optimierten Scheduler. Dies geht mit einem neu entwickelten FPU-Interface (Floating Point Unit – eigentliche Recheneinheiten in jeder EU) einher. Von diesen verbesserten FPUs besitzt jede EU acht. Bei 64 EUs kommen wir hier also auf 512 FPUs insgesamt. Die FPUs sollen zudem in der Lage sein, zwei Float16-Berechnungen pro Takt auszuführen. Float16-Berechnungen sind noch relativ neu und können komplexere Datentypen und höherer Genauigkeit ersetzen, die in vielen Anwendungsbereichen aber nicht notwendig sind.

In etwa vergleichen lässt sich dies mit der Anzahl der Shadereinheiten bei AMD und NVIDIA. Intel spricht von einer Rechenleistung von mehr als einem Teraflop. Wir dürften hier also in etwa in der Leistungsklasse einer Vega-8-GPU landen. Damit will sich Intel auch von Entwicklungen wie den Core-Prozessoren mit angebundener Vega-GPU unabhängig machen. Anhand der gezeigten Pläne und Details dürfte nun eigentlich klar sein, dass die Core-Prozessoren mit Vega-Grafik ein einmaliges Projekt waren und so in dieser Form keine zweite Generation sehen werden.

Neben der 3D-Rechenleistung wird die Gen11-Grafik auch im Bereich der Display-Technologien einige Neuerungen bringen. Dazu gehört die Unterstützung von parallelem De- und Encoding von Videos bis zu einer Auflösung von 8K, aber auch die Display-Ausgabe bei bis zu 8K und die Unterstützung der Display-Synchronisation Adaptive Sync auf Basis des VESA-Standards.

Die erste Nutzung der Gen11-Grafik wird wir bei den Ice-Lake-Prozessoren sehen. Diese wird es als Desktop-Prozessoren mit Gen11-Grafik geben, aber auch in Notebooks bis herunter zu ultramobilen und sparsamen Ultrabooks.

Xe soll die eierlegende Wollmilchsau der GPUs werden

Das, was nach der Gen11-Grafik kommt, ist aber sicherlich der spannendere Schritt. Hierzu hat Intel allerdings noch nicht allzu viel verraten. Xe soll aber die besagte eierlegende Wollmilchsau werden, denn Intel plant vom Einsteigerbereich und den integrierten Grafiklösungen bis hin zum Enthusiasten-Bereich am Desktop - und auch das Datacenter wird mit dem, was sich hinter dem Namen Xe verbirgt, versorgt werden.

Wir kennen also noch keinerlei technische Details und ebenso unklar ist auch, wie Intel starten möchte. Wird es erst Produkte für den Einsteigerbereich geben oder wird das Datacenter zunächst mit GPU-Beschleunigern versorgt? Die Erwähnung vom Enthusiasten-Segment lässt aber zumindest hoffen, dass man bei Intel mit Xe vom Start weg mit den "großen Zwei" konkurrieren möchte. Ob dies am Ende gelingen kann, wird sich noch zeigen müssen.

Foveros ist ein Ausblick auf Intels Zukunft

Die CPU- und GPU-Strategien sind nur ein Ausschnitt dessen, wie Intel die eigene Zukunft für sich entwickeln will. Im Rahmen des Architecture Day 2018 sprach Intel auch über die grundsätzliche Neuausrichtung.

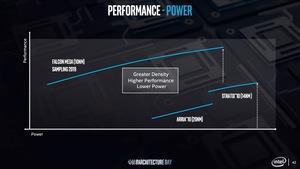

Bereits mehrfach erwähnte haben wir, dass Intel die Entwicklung von Techniken/IP nicht mehr an einen konkreten Prozess koppeln möchte. Je nach Produkt soll nun der Prozess verwendet werden, der hierfür ideal und zum jeweiligen Zeitpunkt vorhanden ist. Skalare Architekturen für CPUs, Vektor-Architekturen für GPUs, Matrix-Architekturen für AI-Beschleuniger und Spatiale-Architekturen für FPGAs stellen unterschiedliche Herausforderungen an die Fertigung. Die für 2019 geplanten Prozessoren und Chips entstammen noch der alten Auslegung, ab Ice Lake soll dann eine neue Strategie greifen.

Einen Ausblick auf die Zukunft, wie Intel sie sich vorstellt, ist eine Technik namens Foveros. Es handelt sich dabei um die Umsetzung eines 3D-gestapelten Prozessors, der noch etwas weiter geht, als bisher per Embedded Multi-die Interconnect Bridge (EMIB) angebundene Chips. EMIB ist der Oberbegriff für das, was als Foveros ab 2019 in breiteren Einsatzgebieten verfolgt werden soll. Es geht darum, für ein MCM-Design bestehend aus CPU, GPU, Speicher und anderen Bauteilen immer die dazu ideale Fertigung nutzen zu können. Auch dies macht AMD bei den EPYC-Prozessoren der zweiten Generation vor: Während die CPU-Chiplets aus der 7-nm-Fertigung stammen, wird der I/O-Die in 14 nm gefertigt.

Mögliche Komponenten eines MCM-SoC sind die CPU und GPU, aber auch Strom- und Spannungsversorgung, eventuelle Mobilfunkmodems, Speicher, Sensor-Tranceiver, Interconnects und FPGAs. Die für Foveros geplante EMIB-Technik dient nicht dazu, einen High-End-Prozessor oder großen SoC zu fertigen. In einem ersten Schritt plant Intel zunächst einmal die Einführung eines kleinen und sparsamen SoC. Ein erstes Produkt auf Basis von Foveros soll bereits 2019 auf den Markt kommen. Dabei handelt es sich um einen Hybrid-SoC, bestehend aus einem Basis-Package, auf dem wiederum ein I/O-SoC sitzt. Darauf wird ein Compute-Die gestapelt und darüber befindet sich ein sogenannter PoP-Speicher (Package on Package). Während der I/O-SoC in 22 nm gefertigt wird, stammt der Compute-Die aus der 10-nm-Fertigung. Das gesamte Package ist nur 12 x 12 x 1 mm groß und soll sich daher für den mobilen Einsatz eignen. Intel spricht von einer Standby-Leistung von gerade einmal 2 mW.

Bevor die Rufe nach großen MCM-Designs auf Basis von Foveros nun laut werden, noch eine kleine Einschätzung dazu: Jeder Chip gibt eine gewisse Abwärme ab. Stapelt man nun Chip übereinander, haben diese kaum noch eine Möglichkeit, ihre Abwärme über einen direkten Kontakt mit einem Kühler abzugeben. Im Falle des ersten Foveros-Chips will Intel dieses Problem durch eine thermische Kontaktierung der eingebetteten Chips gelöst haben. Allerdings sprechen wir hier von einem extrem sparsamen SoC, der nicht mehr als 1 W an Abwärme erzeugen dürfte. Für größere und leistungsstärkere Chips würde diese deutlich schwerer werden.

Grundsätzlich aber wird Intel in Zukunft deutlich modularer aufgebaute Chips präsentieren. Mit einen Xeon-AP-Modellen und direkt angebundenen FPGAs hat man dies bereits getan. Gleiches gilt für die FPGAs aus der Arria- und Stratix-Serie. Im kommenden Jahr wird man das Sampling der Falcon-Mesa-FPGAs starten. Hier werden bereits einzelne IPs wie CPUs, GPUs, ASICs, DAC und ADC sowie HBM direkt im Package miteinander verbunden. Wir sprechen hier also von mehr als zwei Komponenten. Die ersten Samples der Cascade-Lake-Prozessoren bestehend aus zwei 24-Kern-Dies sollen ebenfalls bereits ausgeliefert worden sein.

Allem Anschein nach werden die Ice-Lake-Prozessoren, sowohl im High-End-Desktop (Ice Lake-X) als auch die Servervarianten Ice Lake-SP noch große monolithische Chips sein. Die FPGAs und an Xeon-Prozessoren angebundenen FPGAs werden in nächster Zukunft die größeren modularen Designs bei Intel sein. Was danach kommt, wird man sehen müssen.

Intel hat den Wink verstanden und reagiert

Neben den erwähnten Neuerungen in den Bereichen CPU, GPU und Fertigungstechnologien sprach Intel auch noch über die Fortschritte in den weiteren Bereichen. Das Thema Sicherheit hat Intel im Rahmen der Spectre- und Meltdown-Lücken viel Vertrauen gekostet. Entsprechend hat man für zukünftige CPU-Architekturen Mitigationen vorgenommen – erst mit einer komplett neuen Basis-Architektur wird man versuchen Sidechannel-Attacken in dieser Form gänzlich zu verhindern.

Die Entwicklung am Optane DC Persistent Memory schreitet ebenfalls voran. Mit den Cascade-Lake-Prozessoren wird man den ersten Praxiseinsatz des neuen Arbeitsspeichers sehen. Ob dieser jemals auf Endkunden-Systemen zum Einsatz kommen wird, steht noch in den Sternen. Zunächst einmal will Intel die Speicherhierarchie im Datacenter etablieren.

In den vergangenen Wochen gab es viel Kritik an Intel – sowohl von Seiten der Endkunden, aber auch von der Presse. Die Probleme in der 10-nm-Fertigung sind sicherlich kein Paradebeispiel guter Unternehmenskommunikation. Gleiches gilt für die Spectre- und Meltdown-Sicherheitslücken, die Intel noch über Jahre begleiten werden.

Der Architecture Day 2018 ist sicherlich auch eine Reaktion auf die Kritik der vergangenen Monate. Raja Koduri (Leiter der Core and Visual Computing Group) und Jim Keller (Senior Vice President Silicon Engineering) hatten hier ihren ersten offiziellen Auftritt und auch wenn der Einflussbereich beider sich erst in 2-3 Jahren zeigen wird, ein Anfang ist gemacht. Mit den Ice-Lake-Prozessoren im kommenden Jahr und perspektivisch mit den diskreten GPUs ab 2020 stehen uns aber interessante Zeiten bevor!