Werbung

Auf der CES gab AMD einen Ausblick auf die Ryzen-Prozessoren der 3. Generation, die mit acht und mehr Kernen auf Basis der Zen-2-Architektur und der Unterstützung für PCI-Express 4.0 irgendwann ab Sommer 2019 erhältlich sein sollen.

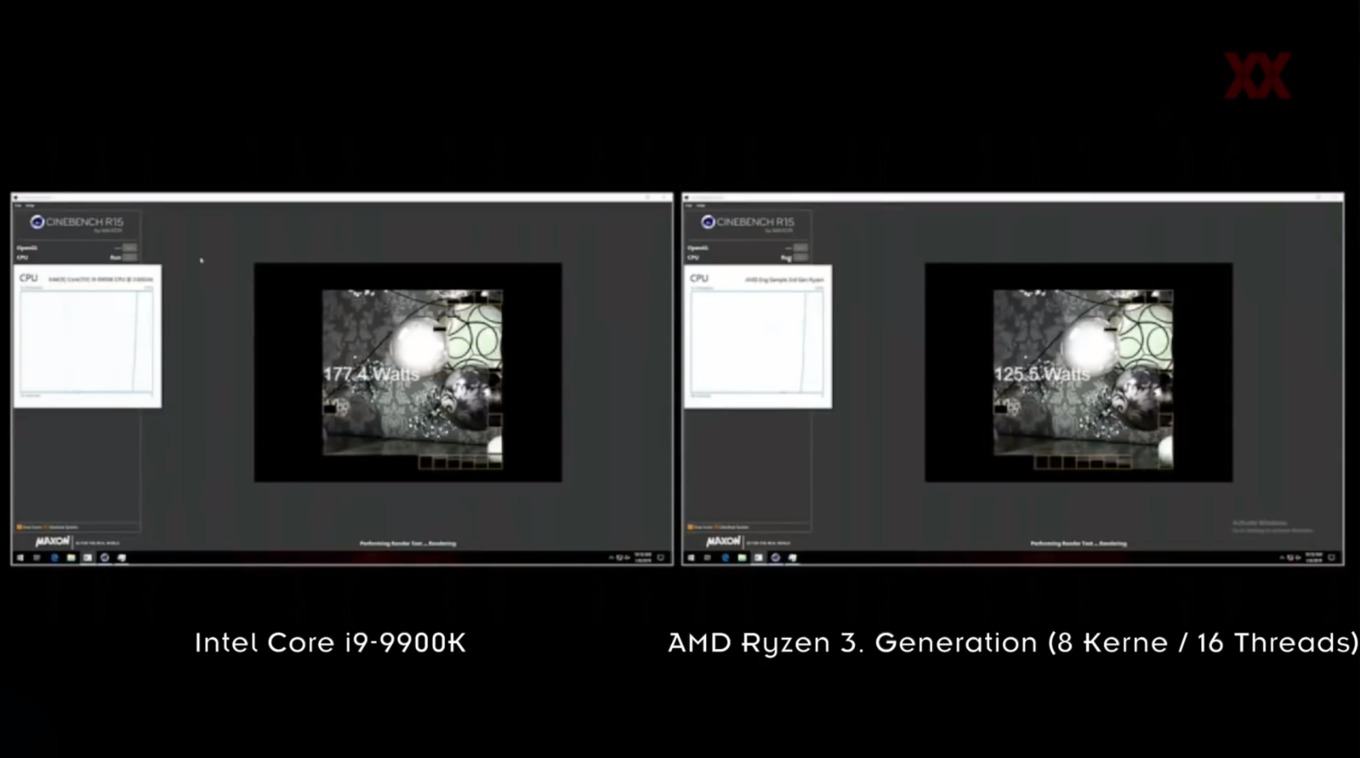

Auf der Bühne wagte AMD zudem einen Vergleich zur Konkurrenz und stellte einen Ryzen-Prozessor der 3. Generation mit noch nicht finalen Taktraten gegen einem Intel Core i9-9900K. Der Ryzen-Prozessor brachte es auf 2.023 Punkte im Cinebench R15, während es beim Core i9-9900K 2.042 Punkte waren. Der Ryzen-Prozessor verfügte über acht Kerne, während die Taktraten nicht genannt wurden. Wohl aber sprach AMD über die Effizienz. Während sich der Core i9-9900K 125 W Leistung genehmigte, sollen es für den kommenden Ryzen-Prozessor nur gewesen 75 W sein. Die Leistungsaufnahme des Gesamtsystems lag bei 180 bzw. 130 W. Mit diesem Vergleich wollte AMD sicherlich auch die Vorteile der Fertigung in 7 nm für die CPU-Chiplets herausstreichen.

Im Nachgang wurde der Vergleich natürlich fieberhaft diskutiert. Mit welchen Taktraten arbeitete der Ryzen-Prozessoren? Wie final war das BIOS und die sonstige Software der Plattform? Viele Fragen sind noch offen und damit ist eine reale Einschätzung der Hardware und auf der Bühne erbrachten Leistung schwierig.

YouTuber DannyzPlay will aus AMD-internen Quelle weitere Details zur Demo erfahren haben. Da sich diese Informationen nicht verifizieren lassen, ist die entsprechende Vorsicht geboten.

Der internen Quelle zufolge soll der Ryzen-Prozessoren der 3. Generation hinsichtlich der Leistungsaufnahme gedrosselt gewesen sein. Die genannten 75 W Leistungsaufnahme sollen nicht dem vollen Potenzial des Prozessors entsprochen haben. Stattdessen soll eine Drosselung um 30 bis 40 % stattgefunden haben. Damit würden wir bei einer Leistungsaufnahme von 95 bis 105 W landen, was typisch für einen High-End-Desktop-Prozessor wäre. Nun lassen sich diese 30 bis 40 % nicht einfach in eine entsprechend höhere Taktung (die noch immer unbekannt ist) umrechnen und auch die Leistung wird nicht gleich um diese Spanne ansteigen, aber dennoch wäre dies ein Indiz dafür, dass AMD sich bewusst noch etwas Luft gelassen hat, um gegen Intels Comet-Lake-Prozessoren, die über bis zu 10 Kerne verfügen sollen, antreten zu können.

Die Gründe für eine Beschränkung der Demo auf der Bühne sind vielfältig: So will AMD sicherlich nicht schon im Januar alle Karten auf den Tisch legen und Intel damit eine Gelegenheit bieten, eventuell gegensteuern zu können. Zudem dürfte sich die Hardware, vor allem aber die dazugehörige Software (BIOS etc.) im Januar noch nicht im finalen Stadium befunden haben.

Es dürfte also noch einmal spannend werden, wenn AMD die Ryzen-Prozessoren der 3. Generation final vorstellen und dann auch näher auf die Leistung eingehen wird. Zudem wird es sicherlich nicht mehr ausreichend sein, nur Cinebench-Ergebnisse anzuführen, um die eigene Leistung zu demonstrieren. Kunden ist in zwei Generationen der Ryzen-Prozessoren ersichtlich geworden, dass es hier noch weitere Aspekte, beispielsweise die IPC- und Single-Threaded-Leistung gibt und hier hat Intel noch immer einen klaren Vorsprung.

Datenschutzhinweis für Youtube

An dieser Stelle möchten wir Ihnen ein Youtube-Video zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Youtube setzt durch das Einbinden und Abspielen Cookies auf ihrem Rechner, mit welchen Sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf den Play-Button. Das Video wird anschließend geladen und danach abgespielt.

Ihr Hardwareluxx-Team

Youtube Videos ab jetzt direkt anzeigen

Die Speichercontroller im Fokus

Schlussendlich will DannyzPlay noch erfahren haben, dass AMD noch einmal einen Fokus auf die Unterstützung von schnellem DDR-Speicher gelegt hat. Hier hat sich zwar gezeigt, dass die bisherigen Ryzen-Prozessoren extrem von einem Feintuning des Arbeitsspeichers profitieren, es aber eine Hürde hinsichtlich des Taktes gibt, die von den Intel-Prozessoren problemlos genommen wird. Auch in diesem Bereich soll es für die Ryzen-Prozessoren der 3. Generation also Verbesserungen geben.

Der Entwickler des DRAM Calculator for Ryzen will zudem weitere für die Speicherunterstützung relevante Informationen erhalten haben. Laut diesen wird der Speichercontroller der Ryzen-Prozessoren der 3. Generation über eine Funktion verfügen, die Fehler in den Speicherdaten erkennt, auch wenn kein ECC-Speicher zum Einsatz kommt.

- New memory controller with partial error correction for nonECC memory

- Desktop processor with two (2 CCD) chiplets on board, 32 threads maximum

- New MBIST (Memory built-in self-test)

- Core watchdog - is a fail/safe function used to reset a system in case the microprocessor gets lost due to address or data errors

- XFR - at the moment I do not see anything special about it, the algorithm and limits have been updated. Scalar Controll come back with new processors.

- Updated core control has a symmetric configuration of the active cores . In 2CCD configurations, each chiplet has its own RAM channel in order to minimize latency to memory access. 1 channel on 8 cores will be a bottleneck if you use the system in the default state.

Hier ebenfalls interessant ist die Erwähnung von Prozessoren mit zwei Chiplets, also zwei CPU-Chiplets mit jeweils acht Kernen, was insgesamt 16 Kerne und 32 Threads zur Folge hätte. Aufgrund des Aufbaus der Ryzen-Prozessoren der 3. Generation wäre dies möglich und wurde von AMD in dieser Form auch schon mehr oder weniger bestätigt.

Spannend sind noch die Details dazu, wie AMD mit den Speicherzugriffen umgeht. Der I/O-Die stellt im Falle der Ryzen-Prozessoren die Speichercontroller. Bei den AM4-Prozessoren handelt es sich weiterhin um ein Dual-Channel-Speicherinterface. Modelle mit einem CPU-Chiplet und mit maximal acht Kernen binden beide Kanäle an diesen einen Chiplet an. Dazu sind im I/O-Chiplet zwei Unified Memory Controller vorhanden. Doch wie wird mit Zugriffen auf den Speicher durch die Chiplets verfahren und welche Auswirkungen werden wir hier sehen, wenn derart viele Kerne über nur zwei Speicherkanäle arbeiten? Die gleiche Frage stellt sich auch bei den EPYC-Prozessoren der 2. Generation, denn hier stehen für acht Chiplets mit jeweils acht Kernen auch nur acht Speicherkanäle zur Verfügung.

Es gibt also noch einige Fragen, die sicherlich bis zum Start der Prozessoren durch AMD beantwortet werden.