Werbung

Neben den neuen Xeon-Prozessoren (Xeon D-1600 und Xeon Scalable der 2. Generation) stellt Intel auch neue Hardware in anderen Bereichen vor. Seit einigen Jahren arbeitet Intel hier unter dem Codenamen Falcon Mesa ein einem FPGA-Design, welches die aktuelle Produktstrategie von Intel wohl sehr gut repräsentiert.

Über alle Präsentationen und Vorstellungen der jüngeren Vergangenheit hinweg wird deutlich, dass der Chipgigant zukünftig flexibler werden will. Dies beginnt mit der Fertigungstechnologie, die bislang an konkrete Produkte gebunden war. Kommt es aber zu Problemen in der Entwicklung einer neuen Fertigung, wie aktuell beim 10-nm-Prozess, ist eine eng an die Fertigung gebundene IP quasi wertlos bzw. kann ihr Potenzial nicht ausspielen. Dies ist einer der Punkte, den Intel angehen möchte, und dies zeigt sich in den einzelnen Produktsparten auch deutlich.

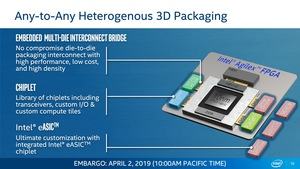

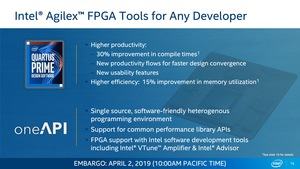

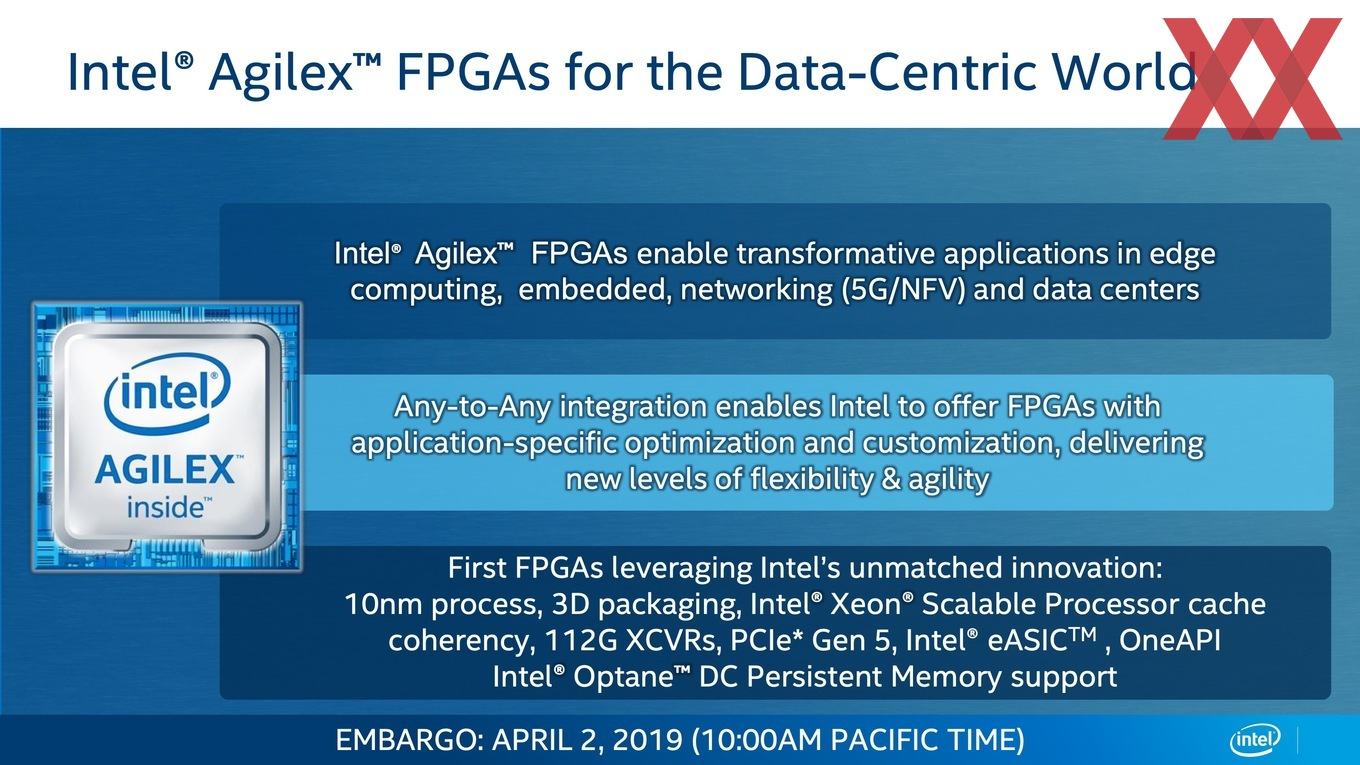

Eine dieser Produktsparten sind die FPGAs, die ab dem 3. Quartal in Form der Agilex-Chips auf den Markt kommen sollen. Sie sollen in 10 nm gefertigt werden, lassen aufgrund des Chiplet-Designs aber auch Module zu, die aus anderen Fertigungstechniken stammen. Für bestimmte Anwendungen wichtig und sinnvoll ist die Cache-kohärente Anbindung der Xeon-Prozessoren. Zusammenfassend kann man sagen, dass Intel über das Chiplet-Design unterschiedliche IP sowie Chiptypen zusammenbringen kann und damit flexible und auf den Anwendungsbereich spezialisierte Hardware anbieten möchte.

Eine wichtige Rolle in der Strategie spielt der Kauf des Unternehmens eASIC aus der Mitte der vergangenen Jahres. Seit 19 Jahren unterstützt das Unternehmen Kunden in der Entwicklung von ASICs und FPGAs. Dabei begleitete man die Kunden von den ersten Ideen bis zur letztendlichen Auslieferung. Diese Expertise soll in Zukunft unter dem Dach von Intel genutzt werden. Unter anderem soll die Intel-eigene EMIB-Technologie (Embedded Multi-die Interconnect Bridge) dazu verwendet werden, FPGAs und klassische Rechenbeschleuniger zusammenzubringen. Dies geschieht auch heute schon, wird in Zukunft aber eine immer größere Rolle spielen – wie eben für die Agilex-Chips.

Die nun als Agilex-Chips bekannten Designs kennen wir wie gesagt unter dem Namen Falcon Mesa und das Schaubild (oben) haben wir ebenfalls bereits gesehen. Einige der genannten Technologien sind eine Grundvoraussetzung für das Design eines solchen Chips, darunter die 2. Generation der Hyperflex-Technologie. Andere wiederum werden für die Chips, die für das 3. Quartal 2019 geplant sind, noch etwas verfrüht sein – wie beispielsweise DDR5 und PCI-Express 5.0.

Intel möchte damit aber die Flexibilität der Agilex-Chips unterstreichen und andeuten, dass diese je nach der gewünschten Anwendung entsprechend ausgelegt werden können – sei es durch zusätzlichen HBM2 oder die Notwendigkeit nach schnellen PCI-Express-Lanes und 112G Transceivern.

Embedded Multi-Die Interconnect Bridge (EMIB) ist die Technologie, die zur Verbindung der einzelnen Chips verwendet wird. Unter EMIB kann der Aufbau verschiedener Dies auf einem Interposer verstanden werden. Dieses sogenannte 2,5D-Design kann die verschiedensten Dies untereinander verbinden und stellt dank Through Silicon Vias (TSVs) einen schnellen Interconnect her. Im Unterschied zu anderen Technologien mit Interposer wird bei EMIB kein großer Extra-Die verwendet, der alle Kontaktpunkte als Interconnect untereinander verbindet. Die Schnittfläche, welche die eigentlichen Kontakte mittels TSVs herstellt, ist nur sehr gering.

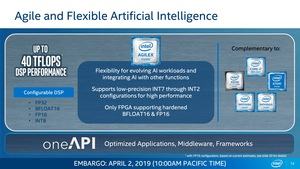

Eines der wichtigsten Anwendungsfelder für die Agilex-Chips ist das Inferencing – also die Auswertung von Deep-Learning-Netzwerken. Bereits trainierte Netzwerke werden über Sensoren und andere Methoden mit Eingabedaten gefüttert und liefern möglichst schnell eine Ausgabe. Hierzu bieten die FPGAs konfigurierbare DSPs für FP32, BFloat16, FP16 oder INT8. Außerdem können auch noch weniger genaue Datentypen berechnet werden, die in der Praxis aber noch keine weite Verbreitung finden. Hierzu müssen erst weitere Entwicklungen und Forschungsarbeiten folgen. Dennoch sind INT7 bis INT2 ebenso angedacht, aber keine Agilex-exklusive Funktion, sondern können so auch von NVIDIA mittels Tensor Cores umgesetzt werden.

Die Agilex-Chips sind aber vorerst die einzigen Chips, die FP16 und Bfloat16 in der Hardware unterstützen. Mit den Cooper-Lake-Xeons wird Bfloat16 auch einer der Standard-Befehlssätze in diesem Bereich.

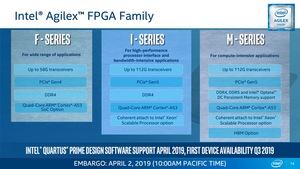

Drei Serien werden im 3. Quartal auf den Markt kommen:

- F-Series: 58G Transceiver, PCI-Expresss 4.0, DDR4-Controller, Quad-Core ARM (Cortex-A53) als Option

- I-Series: 112G Transceiver, PCI-Express 5.0, DDR4-Controller, Quad-Core ARM (Cortex-A53), koherente Verbindung zu Xeon-Prozessoren

- M-Series: 112G Transceiver, PCI-Express 5.0, DDR5-Controller, Optane DC Persistent Memory, Quad-Core ARM (Cortex-A53), koherente Verbindung zu Xeon-Prozessoren, HBM-Controller als Option

Mit den Agilex-Chips stellt sich Intel in einem Bereich auf, den man zwar teilweise bereits mit den Xeon-D-Prozessoren abdeckt, der aufgrund der Flexibilität der FPGAs aber weitaus breiter ausgebaut werden kann. Sogenannte Edge-Netzwerke und Edge-Hardware werden ebenso abgedeckt wie Netzwerkinfrastruktur und das Datacenter.

Je näher das 3. Quartal rückt, desto genauer werden vermutlich auch die Informationen zu den einzelnen FPGAs. Das Intel bereits heute über DDR5 und PCI-Express 5.0 spricht, ist etwas überraschend, denn beide Standards sind noch nicht in einer finalen Auslegung spezifiziert.