Werbung

Im Frühjahr 2018 machte ein Startup namens Tachyum das erste Mal auf sich aufmerksam. Statt auf spezielle Beschleunigerhardware zu setzen, setzte man von Anfang an auf einen Universalprozessor, der alle Anforderungen zugleich bedienen soll. Tachyum will damit das Datacenter revolutionieren. Rund ein Jahr später sprach man dann über erste technische Details.

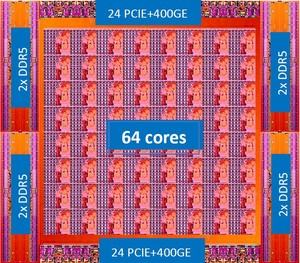

64 Kerne sollten in der vorerst größten Ausbaustufe des Chips arbeiten. Hinzu kommen acht DDR5/DDR4-Speichercontroller, 72 PCI-Express-5.0-Lanes, 2x 400/100/50/25/10 GbE, 2x HBM3 (optional), 32 MB an kohärentem L2/L3-Cache und dies alles verpackt in einen Thermal Design Power von 180 W bei 4 GHz.

The Next Platform sprach mit Radoslav Danilak, einem der Gründer und CEO von Tachyum. Statt in einzelnen CPUs, GPUs, TPUs, NNPs und FPGAs sieht man bei Tachyum die Zukunft in einem Hybrid-Design, welches die einzelnen Spezialanforderungen und damit einen größeren Markt abdecken kann. Radoslav Danilak und die beiden Mitgründern Igor Shevlyakov und Rod Mullendore haben allesamt Erfahrungen im Halbleitergeschäft – waren bei Toshiba, SandForce, Nishan Systems und NVIDIA angestellt. Doch hinter Tachyum stehen weitere Köpfe wie Fred Weber, Co-Founder von Encore Computer (Supercomputer-Hersteller), der auch am 64-Bit-Design der Opteron- und Athlon-Prozessoren von AMD beteiligt war.

Die harten Fakten

Doch kommen wir zu dem, über das Tachyum nun eigentlich sprechen will. In den vergangenen Monaten hat man den Prodigy-Chip in FPGA-Simumlatoren weiterentwickelt und will Ende 2020 den Type Out des Chips schaffen. Gefertigt wird dieser in 7 nm bei TSMC. Der Prozessor hat eine Größe von 290 mm². Über die Anzahl der Prozessoren spricht Tachyum nicht.

Die einzelnen Prozessorkerne des Chips sollen in der Lage sein, die unterschiedlichsten Rechenoperationen durchzuführen – seien es HPC-Operationen mit hoher Genauigkeit, ein Inferencing mit geringer Genauigkeit oder etwas zwischen diesen Anforderungen. Danilak stellt dabei eine kühne Behauptung auf:

"Every core is faster than a Xeon core or an Epyc core, and it is smaller than an Arm core, and overall, our chip is faster than a GPU on HPC and AI." – Jeder einzelne Kern soll demnach schneller als ein solcher von Intel, AMD und dabei kleiner als ein HPC-ARM-Designs sein. Der Chip soll schneller als ein HPC- oder AI-Chip sein.

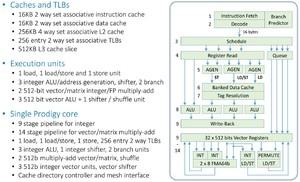

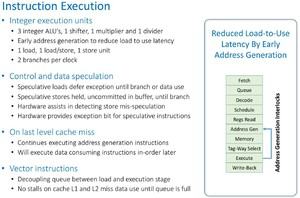

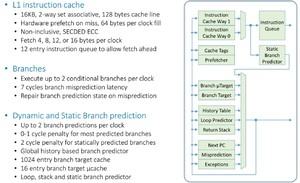

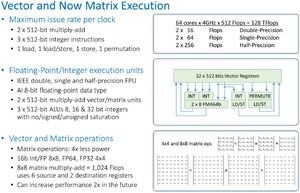

Die einzelnen Kerne sollen in der Prozessor-Pipeline einer Out-of-Order-Execution folgen – nicht in der Hardware selbst, wohl aber über den Compiler. Die Pipeline als solches kann im Grunde nicht auf eine In-Order- oder Out-of-Order-Execution festgelegt werden. Hinsichtlich der Instructions Sets (32 Integer Register mit 64 Bit und 32 Vector Register die 256 oder 512 Bit haben können) und deren Handling ist man an Intels Itanium-Design erinnert, aber auch NVIDIA nutzt sogenannte Poison Bits. Letztendlich kann die Pipeline eines Kerns zwei Multiply-Adds, einen Store, eine Adresserhöhung, einen Vergleich und einen Branch pro Taktzyklus ausführen. Man will sich hier hinsichtlich der IPC auf Niveau von Intels Skylake-Architektur bewegen.

Die 64 Kerne des Tachyum Prodigy T864 teilen sich in vier Blöcke zu je 16 Kernen. Sie sind über ein Mesh-Interconnect im L3-Cache miteinander verbunden – die Speichercontroller über ein eigenen Mesh-Interconnct. Jeder der Blöcke mit 16 Kernen ist mit zwei DDR4/DDR5-Speichercontrollern und 18 PCI-Express-5.0-Lanes verbunden. Per SerDes (Serialisierer/Deserialisierer) können pro Block 16 PCI-Express-Lanes und ein 400-GbE-Controller verwendet werden. Mischkonfigurationen sind ebenfalls möglich. Die Speichercontroller für den HBM3 bleiben optional und können bei Bedarf umgesetzt werden. Durch die hohen Kosten von HBM3 sieht Tachyum jedoch nur geringe Vorteile gegenüber der Nutzung von schnellem DDR4/DDR5-Speicher.

Ein Blick in die einzelnen Kerne offenbart, dass der L1-Cache vergleichsweise klein ist, die L2- und L3-Caches jedoch übliche Kapazitäten aufweisen. Die Integer-Pipeline besitzt neun Stages und die Vektor-Pipeline 14. Anhand der Blockdiagramme ist zu erkennen, dass der DDR4/DDR5-Speicher mit einer Datenrate von 410 GB/s angebunden ist, während der HBM3 bis zu 1 TB/s pro Speichercontroller anbieten kann.

Die Vektoreinheiten unterstützen FP64, FP32, FP16, FP8 und BFLOAT16. Hinzu kommen INT32, INT16 und INT8. In den Vektor-Einheiten können Matrix-Operationen ausgeführt werden. Ein 4×4 Matrix Multiply wird auf den FP32- und FP64-Einheiten ausgeführt. An Daten der Matrizen sind acht oder 16 Bit Integer- oder Fließkommadaten möglich. Die Fließkommaeinheiten derart doppelt zu belegen, ist interessant, kann aber auch eine Hürde werden, wenn beides gleichzeitig verwendet werden soll. Tachyum überlegt daher die FP-Einheiten in zukünftigen Designs weiter auszubauen. Die vier SIMD-Einheiten mit 512 Bit können als Vektor- oder Tensor Core arbeiten – gewisse Parallelen zu NVIDIA finden sich hier immer wieder. Im Grunde zeigt der Prodigy-Chip bei den Funktionseinheiten keine großen Unterschiede zu den bestehenden Designs von AMD, Intel, NVIDIA und Co.

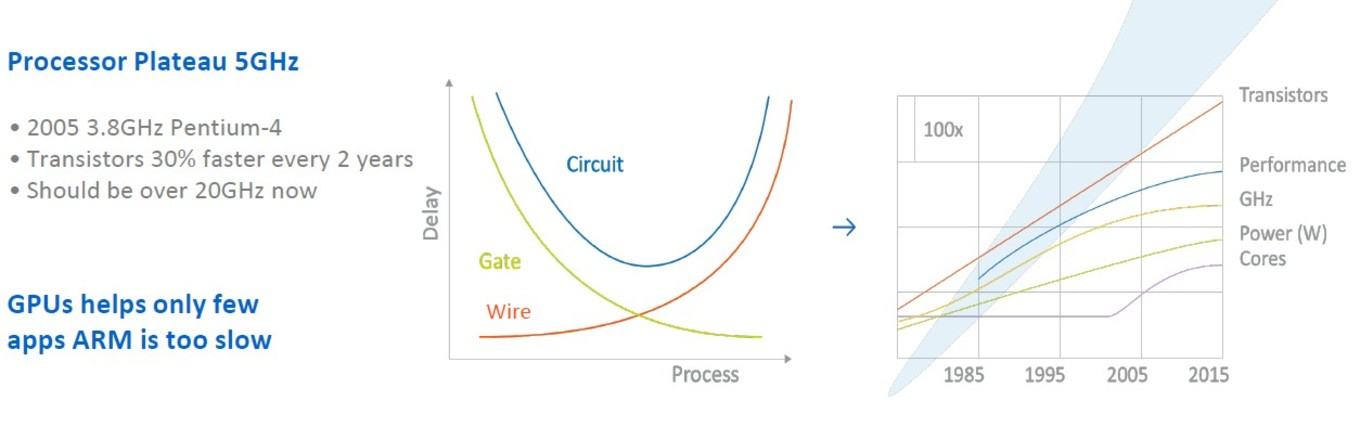

Wo Tachyum mit den Prodigy-Chips einen Vorteil gewinnen will, ist die Tatsache, dass man die breiten Funktionseinheiten mit voller Geschwindigkeit arbeiten lässt, während AVX-Einheiten in Prozessoren nicht mit dem vollen Takt arbeiten und GPUs (sowie andere Spezialbeschleuniger) für gewöhnlich nicht sonderlich hoch takten. Dies soll durch eine verbesserte Verdrahtung der Hardware, schnelle Interconnects und weitere Maßnahmen gelingen.

Wie anfangs erwähnt, will Tachyum den ersten Tape-Out 2020 schaffen. 2021 soll dann die Massenproduktion beginnen können. Verfügbar werden diese dann in der ersten Jahreshälfte 2021 sein. Über einen internen System-C-Simulator wird die Entwicklung weitergeführt und auch ein simuliertes Benchmarking ist damit bereits möglich. Ein FPGA-Hardware-Emulator wird gegen Ende des Jahres verfügbar sein.

Geplant waren ein 2S-System mit 2x 128 Kernen und vier Stacks an HBM in Q1 2020, ein 64-Kern-Chip mit acht DDR4/DDR5-Speichercontrollern in Q2 2020 und ein 32-Kern-Chip mit vier DDR4/DDR5-Speichercontrollern in Q3 2020. Doch diese Pläne sind inzwischen nach hinten verschoben worden.

Die Preise der Prozessoren sollen von ein paar hundert US-Dollar bis unter 10.000 US-Dollar für die High-End-Varianten reichen. Ob man dies mit 32 GB an HBM3 wird umsetzen können, ist jedoch mehr als fraglich.

Noch viele Fragezeichen hinter der Umsetzung

Noch ein viel größeres Fragezeichen muss hinter dem Software-Ökosystem gemacht werden. Der Prodigy-Chip bzw. das Design ist mit keiner bestehenden Architektur kompatibel. Dies wird eine Integration schwierig machen. Wir werden einfach schauen müssen, wie sich das Thema Tachyum Prodigy weiterentwicklen wird.

Zuletzt hat das Thema HPC-Beschleuniger (vor allem auf Basis eines ARM-Systems) deutlich an Fahrt aufgenommen. Marvell präsentierte mit dem ThunderX3 die nächste Generation seiner Serverchips mit bis zu 96 Kernen und SMT4 für 384 Threads. Zuvor stellte Ampere den Altra mit 80 Kernen ausführlich vor. Amazon setzt den Graviton2 mit 64 Kernen bereits erfolgreich in seinen eigenen Cloud-Instanzen ein. Mit Nuvia wurde im vergangenen Jahr ein Startup gegründet, welches den Markt der Datacenter-Prozessoren revolutionieren soll. Hier setzt man allerdings auf eine breite Unterstützung bestehender ARM-Server-Standards durch Server Base System Architecture (SBSA) und Server Base Boot Requirements (SBBR).