Werbung

Mit dem Chip Design with Deep Reinforcement Learning haben einige Forscher bei Google AI, genauer gesagt dem Brain Team, eine selbstlernende Methode für das Floorplaning von Chips vorgestellt. Moderne Chip-Architekturen befinden sich über Jahre in der Entwicklung. Je nach Größe des Projekts und der Auslegung vergehen zwischen zwei und fünf Jahren.

Heute bereits zu wissen, welche Anforderungen in zwei bis fünf Jahren an das Design gestellt werden, ist allerdings alles andere als einfach. Den Chip Design Cycle zu verkürzen, ist also eine entscheidende Maßnahme in der Chipentwicklung, um schnell auf neue Anforderungen reagieren zu können.

Das Floorplaning ist ein zeitraubender Prozess in der Chipentwicklung. Ein Chip, sei es ein Prozessor, eine GPU oder ein Spezialchip zur Beschleunigung bestimmter Rechenaufgaben, besteht aus dutzenden Blöcken unterschiedlichster Komponenten. In einem einfachen Beispiel haben wir die Rechenkerne eines Prozessors, die verschiedenen Caches, Speichercontroller und ein halbes Dutzend Interfaces. Alles muss untereinander verbunden werden und auch die Interconnects selbst können nicht beliebig durch den Chip geführt werden.

Trotz jahrzehntelanger Forschung und einem gewissen Automatismus im Design ist es noch immer notwendig, dass Ingenieure teilweise wochen- und monatelang am Floorplaning sitzen, um bestimmte Probleme zu lösen, die den vielfältigen Design-Kriterien entsprechen. Die Komplexität dieses Problems ergibt sich aus der Größe des sogenannten Netlist Graphen und kann Millionen bis Milliarden von Knoten beinhalten. Selbst nach einer manuellen Positionierung benötigt die Analyse von Power, Performance und Area (PPA) dann noch Stunden oder Tage mit den Design Automation Tools.

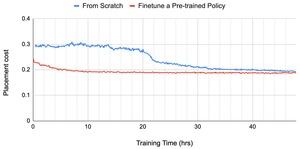

Das Chip Design with Deep Reinforcement Learning soll darauf trainiert werden die Blöcke und das Routing selbständig zu verbessern. Dazu wird ein Graph Neural Network verwendet. Es handelt sich dabei um eine bestimmte Form eines Deep-Learning-Netzwerks. Details dazu führt Google in seinem Blog aus.

Das neuronale Netzwerk wird mit verschiedenen Vorgaben gefüttert, so dass beispielsweise Interface-Komponenten am Rand des Chips platziert werden. Außerdem gibt es natürlich logische Vorgaben wie die Länge der einzelnen Verbindungen so kurz wie möglich zu halten und Kreuzungen weitestgehend zu vermeiden.

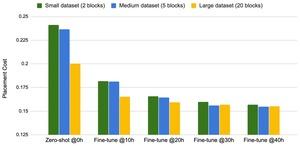

Interessanterweise zeigte sich während der ersten Simulationen folgendes: Je komplexer der Aufbau des simulierten Netlist Graphen, desto besser wurden die Ergebnisse im Hinblick auf die Kosten, die für das Placement aufgewendet werden mussten.

Google AI trainiert das System derzeit an verschiedenen Varianten von Chips. Zu erkennen sei aber bereits, dass das Chip Design with Deep Reinforcement Learning auf eine breite Masse an unterschiedlichsten Anforderungen angepasst werden kann. Natürlich zielt Google zunächst auf die Nutzung für die eigenen Beschleuniger-Chips. Man sehe aber durchaus auch die Möglichkeit das System für alle Chipdesign-Prozesse anzuwenden. Für den ersten eigenen Smartphone-SoC kommt die neue Methode aber wohl zu spät. Auch die bisherigen Tensor Processing Units (TPU) hat man noch klassisch entwickelt.

Google sieht im Chip Design with Deep Reinforcement Learning durchaus eine Möglichkeit den Chip Design Cycle deutlich zu verkürzen. Dies könnte dabei helfen schneller neue Chips zu entwickeln.