Werbung

Auf der VLSI-Konferenz präsentierte Intels CTO Mike Mayberry unter der Überschrift "The Future of Compute" einige Aspekte zur Zukunft des Chipgiganten. Dabei geht der Blick über die aktuelle FinFET- und künftige Gate-All-Around-Technologie hinaus. Transistoren auf Basis von Nanodrähten und Nanobändern sollen sich bereits in fünf Jahren in der Massenproduktion befinden.

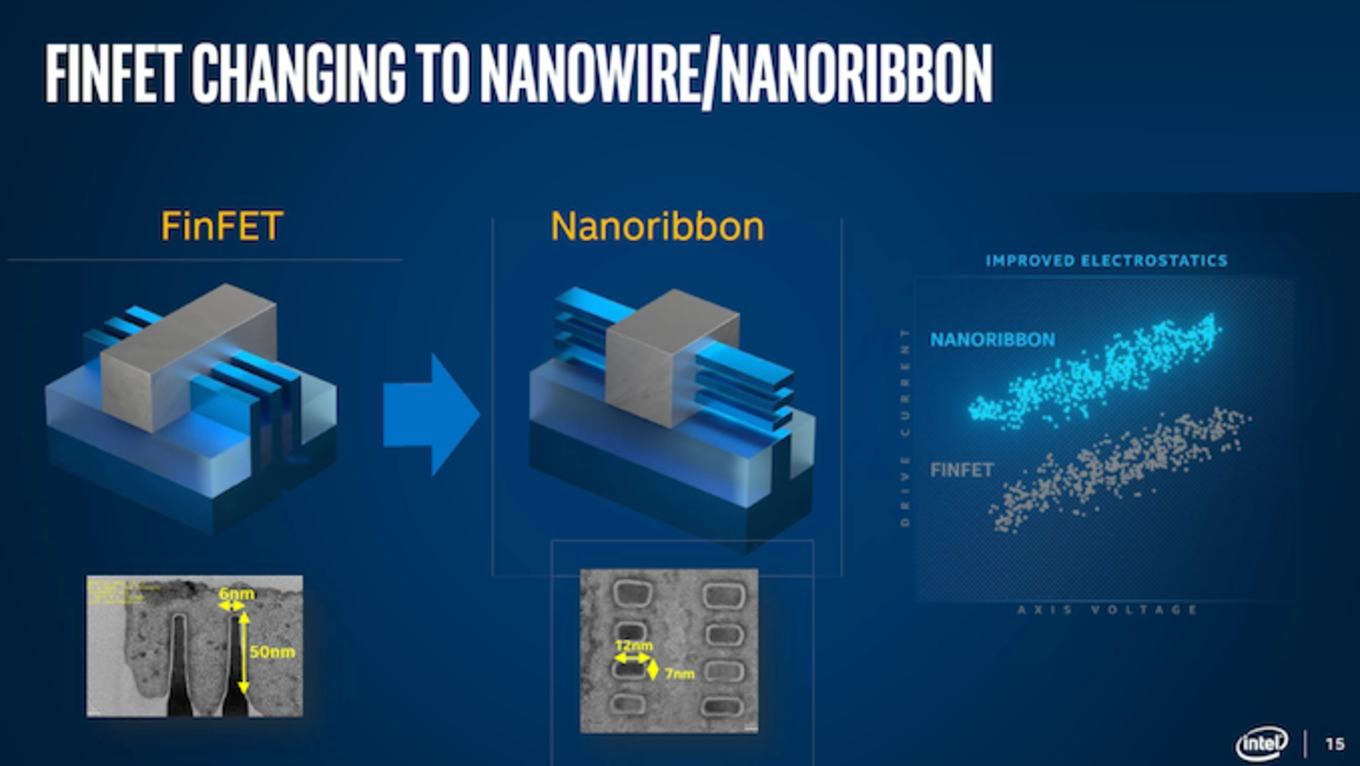

Auf die planaren Transistoren folgten für alle großen Chiphersteller bereits vor einiger Zeit die FinFETs (Feldeffekttransistoren). Diese können vor allem in der Packdichte und Schaltgeschwindigkeit punkten. Multi-Bridge-Channel-FETs (MBCFET) sind der nächste logische Schritt. Als erste Umsetzung arbeiten Samsung, Intel und viele andere Halbleiterhersteller an Gate-All-Around-Transistoren. GAA-Transistoren sind Feldeffekttransistoren (FET), deren Gates auf allen vier Seiten um ultradünne Kanäle gewickelt sind. Diese verbesserte Gate-Steuerung des Kanals überwindet die physikalischen Skalierungs- und Leistungsbeschränkungen von FinFETs und ermöglicht eine weitere Skalierung der Versorgungsspannung.

Zur Umsetzung der GAA-Transistoren sind Nanodrähte und/oder Nanobänder notwendig. Nanodrähte werden bei Samsung für die GAA-Transistoren eingeplant, die breiteren Nanobänder für die MBCFETs. Über die Breite der Nanobänder können die MBCFETs in ihren Betriebsparametern eingestellt werden. Während FinFETs eine festgelegte Frequenz/Spannungskurve haben, an der sich der Kunde bzw. Nutzer der Chips entlangarbeiten kann, ist das Spektrum bei den MBCFETs wesentlich größer.

Der von Mayberry angesprochene Zeitraum von fünf Jahren bis zu Massenproduktion klingt optimistisch. Samsung will noch in diesem Jahr mit der Risikoproduktion der MBCFETs beginnen. Von einer Massenproduktion kann also noch nicht die Rede sein. Ähnlich wie Samsung scheint auch TSMC ab der Fertigung in 3 nm mit Nanodrähten und Nanobändern arbeiten zu wollen.

2021 will Intel die ersten Chips in 7 nm ausliefern. 2023 oder 2024 stünde dann der Wechsel auf 5 nm an. Hinsichtlich der Packdichte dürfte Intels Fertigung in 5 nm auf Niveau der 3-nm-Fertigung von Samsung und TSMC liegen. Aktuell hat Intel hier ebenfalls mit 14 und 10 nm deutliche Vorteile gegenüber der Konkurrenz – kann jedoch in anderen Aspekten nicht mithalten. Mit 7 nm soll dann sozusagen der Reset-Knopf gedrückt und Intel wieder auf Spur gebracht werden.

Konkret nach einem Zeitpunkt gefragt ("Can you give us the timeline for the introduction of nanoribbon/nanowire process technology into high volume production?") sagte Mayberry:

"This is not a roadmap talk, so I'll be vague and say within in the next five years."

Die Kollegen von Anandtech haben die entsprechenden Folien und weitere Informationen vorliegen.

2023/2024 wäre also der frühstmögliche Zeitpunkt. Wahrscheinlicher ist eine leichte Verschiebung nach hinten, womit es 2025 soweit wäre. Bis dahin werden uns die FinFETs noch in 10, 7 und eventuell auch 5 nm begleiten, bevor eine der erfolgreichsten Halbleitertechniken in den Ruhestand geht.