Werbung

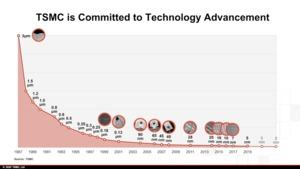

Auf dem Technology Symposium hat TSMC in virtueller Form über die Fortschritte und Neuentwicklung im Bereich der Halbleiterfertigung gesprochen. Bei TSMC ist man im Plan, die Fertigung in 5 nm in diesem Jahr immer weiter hochzufahren, 2022 soll dann die Fertigung in 3 nm folgen.

Verbesserungen gibt es in nahezu allen Bereichen der Fertigung bei TSMC. So bietet man eine optimierte Fertigung in 12 nm (N12e) an, die eine aktuelle Fertigung in 22ULL (22 nm, Ultra Low Voltage) ablösen soll. N12e basiert auf der etablierten 12FFC+_ULL-Fertigung, bietet jedoch zusätzliche Optimierungen. Mit N12e spricht TSMC IoT- und Edge-Hardware an, die besonders effizient betrieben werden soll.

Im Vergleich zu 22ULL soll N12e Chips bei gleicher Leistungsaufnahme um 49 % schneller machen. Die Packdichte der Transistoren steigt um 76 %. In N12e gefertigte Chips sind bei gleicher Leistung um 55 % sparsamer. Da immer mehr SRAM in solchen Chips zum Einsatz kommt, ist dessen Integration, bzw. Fertigung von entscheidender Bedeutung. Leakage im SRAM konnte um 50 % reduziert werden, was die Leistungsaufnahme reduziert. Mittels N12e hergestellte Chips können mit Spannungen von 0,4 V betrieben werden und sind daher besonders sparsam.

N5 und N3 sind TSMCs Wachstumstreiber

TSMC bietet zahlreiche Fertigungstechnologien für eben genannte Sonderfälle an. Das Brot-und-Buttergeschäft ist aktuell die Fertigung in 7 nm. AMD, NVIDIA und Apple sind nur die größten Kunden, die aktuelle N7/N7P verwenden. Doch der Blick geht natürlich schon auf die nächste Generation und hier soll N5 bereits in diesem Jahr zum Einsatz kommen. Apples nächste Generation der A-Series-SoC soll auf N5 setzen – ebenso wie die ersten Chips der Apple-Silicon-Initiative auch die Macs mit eigenen Prozessoren auszustatten. Seit dem zweiten Quartal 2020 fährt TSMC die Massenproduktion der Chips in 5 nm.

In einem nächsten Schritt wird N5P für einige Partner angeboten werden. Im Vergleich zu N5 soll N5P die Leistungsaufnahme um 10 % reduzieren können. Die Leistung steigt um 5 %. 2021 sollen die ersten Chips in N5P bei TSMC von den Bändern rollen. Gefertigt werden die Chips in 5 nm in der Fab18 in Südkorea. 9.000 Mitarbeiter sitzen in der vierten großen Fertigung von TSMC.

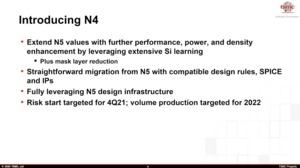

Der nächste Schritt wird N4 sein. Für die Fertigung in 4 nm plant TSMC den Einsatz von mehr EUV-Layern, als dies für N5/N5P der Fall ist. Die Fertigung in N4 soll für Designs, die für N5/N5P entwickelt wurden, ohne große Änderungen möglich sein. Die Migration soll also so leicht wie möglich gemacht werden. Zahlen zu den Verbesserungen in den Bereichen Leistungsaufnahme und Performance gibt es nicht.

Die Risk Production von N4 soll im vierten Quartal 2021 anlaufen. Eine Massenfertigung ist für 2022 geplant.

| Leistungsaufnahme | Performance | Packdichte | |

| N10 zu N7 | - 40 % | - | x 1.4 |

| N7 zu N5 | -30 % | +15 % | x 1,8 |

| N5 zu N5P | -10 % | + 5 % | - |

| N5 zu N3 | -25 - 30 % | +10 - 15 % | x 1,7 |

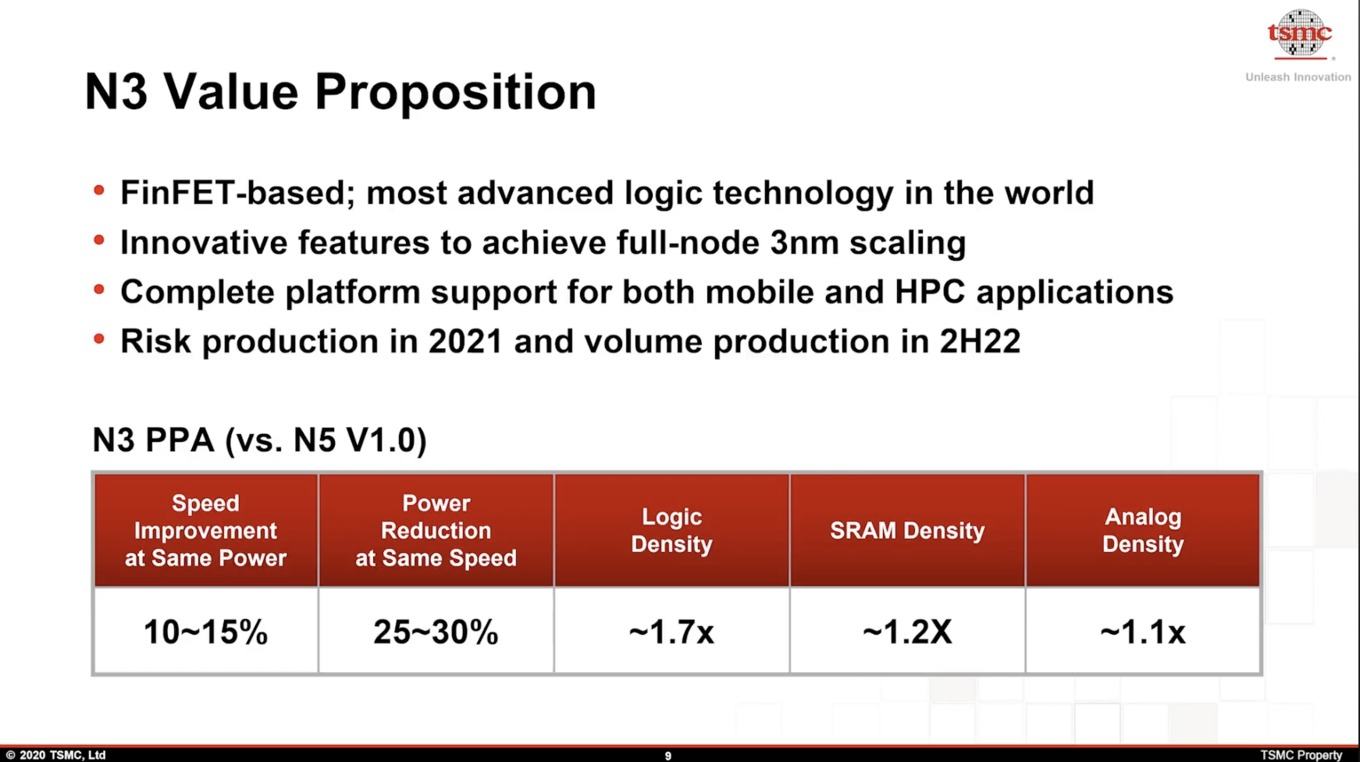

Ein größerer Schritt wird die Fertigung in N3 also 3 nm sein. Anders als Samsung (Multi Bridge Channel FET) wechselt TSMC für 3 nm noch nicht auf eine neue Transistor-Technologie, sondern bleibt dem FinFET treu. Im Vergleich zu N5 wird N3 die Leistung der Chips um 10 bis 15 % steigern können. Die Leistungsaufnahme soll um 25 bis 30 % sinken.

Die Packdichte der Transistoren soll um den Faktor 1,7 steigen. Allerdings kommt TSMC hinsichtlich der Skalierung der Größe an gewisse Grenzen. SRAM lässt sich für N3 nur noch um 20 % kleiner fertigen. Analoge Komponenten eines Chips können sogar nur noch um 10 % kleiner gefertigt werden.

N3 soll 2021 in der Risk Production aufgenommen werden. In der zweiten Jahreshälfte 2022 ist dann die Massenfertigung von Chips in N3 vorgesehen.

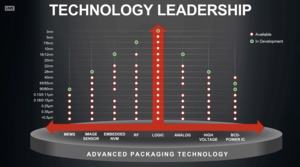

Das TSMC Technology Symposium läuft heute und morgen Vormittag. Ein weiterer Fokus werden die Fortschritte in den Packaging-Technologien sein. In mehreren Sessions wird TSMC die Neuerungen in diesem Bereich präsentieren.