Werbung

Auf dem diesjährigen IEEE International Electron Devices Meeting (IEDM) präsentierte Intel verschiedene Weiter- und Neuentwicklungen aus dem Bereich der Fertigungstechnologien. Eine der wichtigsten Forschungen betrifft die sogenannte Self-Aligned 3D Stacked Multi-Ribbon CMOS Transistoren – selbstausrichtende, gestapelte Transistoren, welche Intel theoretisch in die Lage versetzen sollen, die Transistordichte zu verdoppeln.

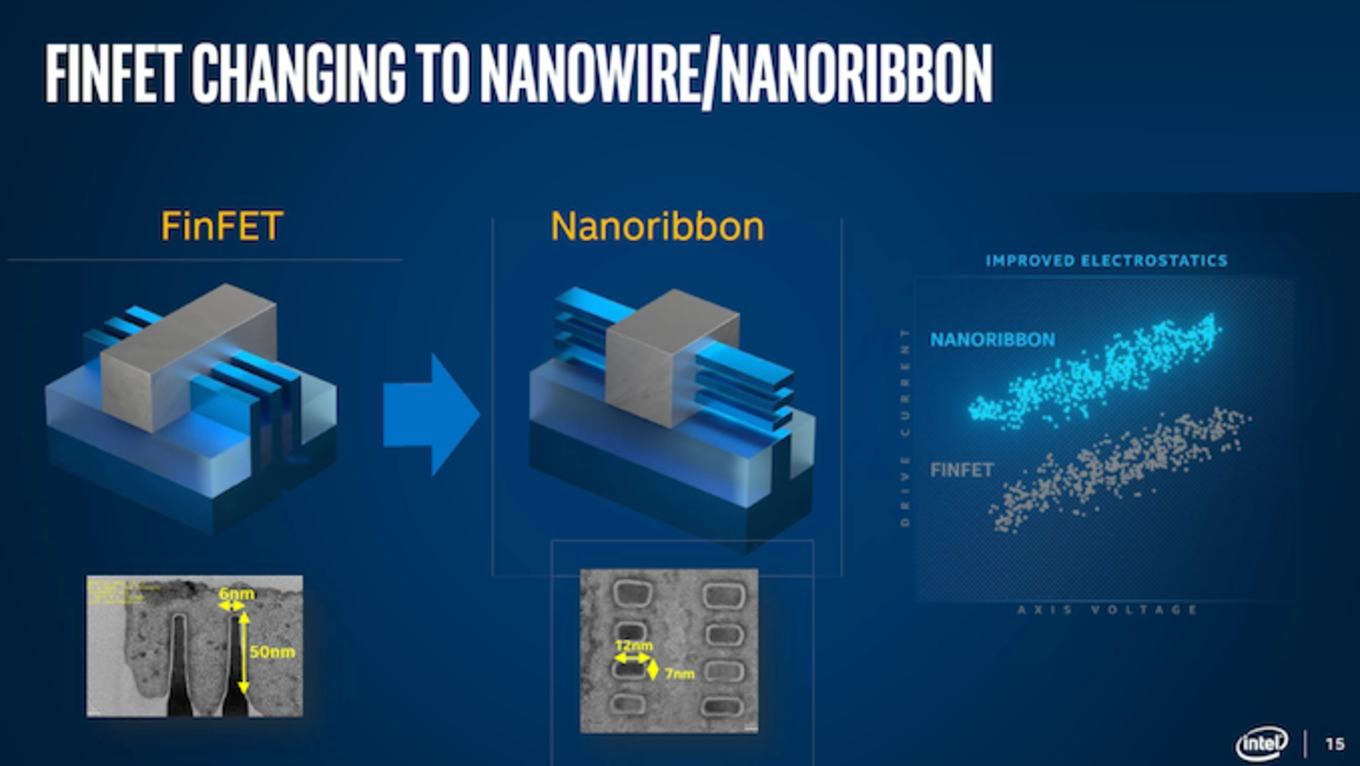

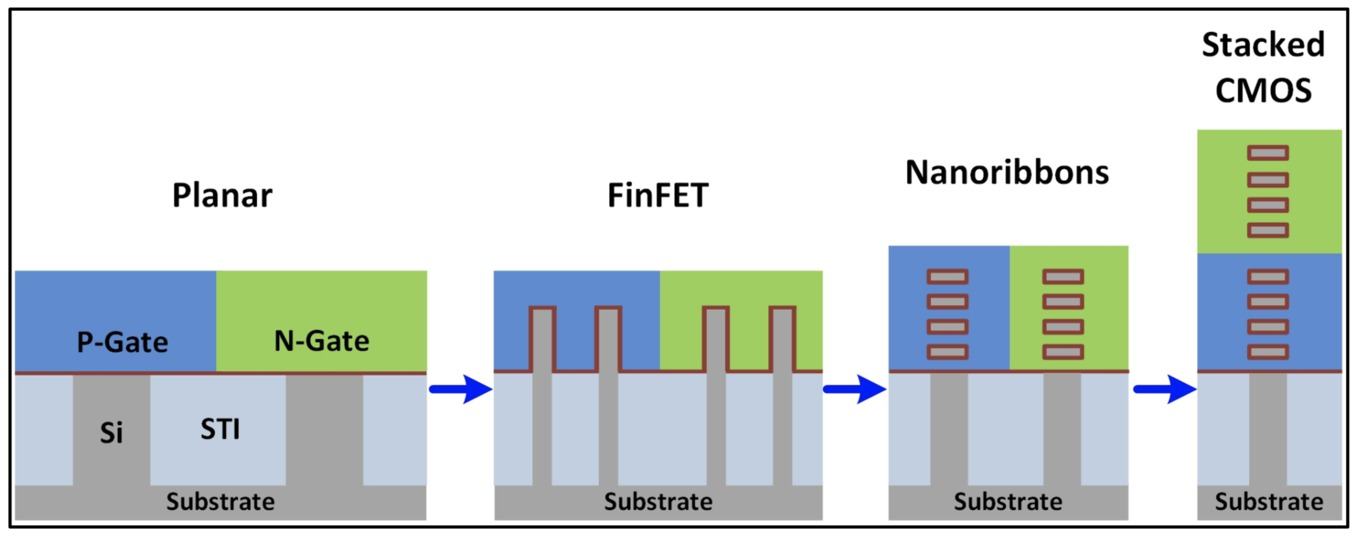

Die Transistoren moderner Halbleiterbauelemente sind in Form der FinFET-Transistoren zwar eine Art 3D-Transistor, die Anordnung dieser erfolgt allerdings noch immer in planarer Bauweise, also nebeneinander. Genau wie Samsung und TSMC arbeitet man bei Intel an neuartigen Transistoren mit Nanosheets und Nanobändern, bzw. Nanodrähten und fertigt damit Gate-All-Around-Transistoren. GAA-Transistoren sind Feldeffekttransistoren (FET), deren Gates auf allen vier Seiten um ultradünne Kanäle gewickelt sind. Diese verbesserte Gate-Steuerung des Kanals überwindet die physikalischen Skalierungs- und Leistungsbeschränkungen von FinFETs und ermöglicht eine weitere Skalierung der Versorgungsspannung. Damit wird die Leistung der Transistoren verbessert.

Künftig will Intel die Fläche, die ein solcher Transistor belegt, durch die Self-Aligned 3D Stacked Multi-Ribbon CMOS Transistoren halbieren. Dazu werden gleich zwei der Transistoren gestapelt gefertigt, jedoch nicht in einem separaten Fertigungsschritt (in dem man sie zum Beispiel getrennt voneinander fertigt und dann wieder zusammenbringt), sondern in einem einzigen. Dazu müssen allerdings Anpassungen an der Fertigung eines Nanosheet-Transistors vorgenommen werden.

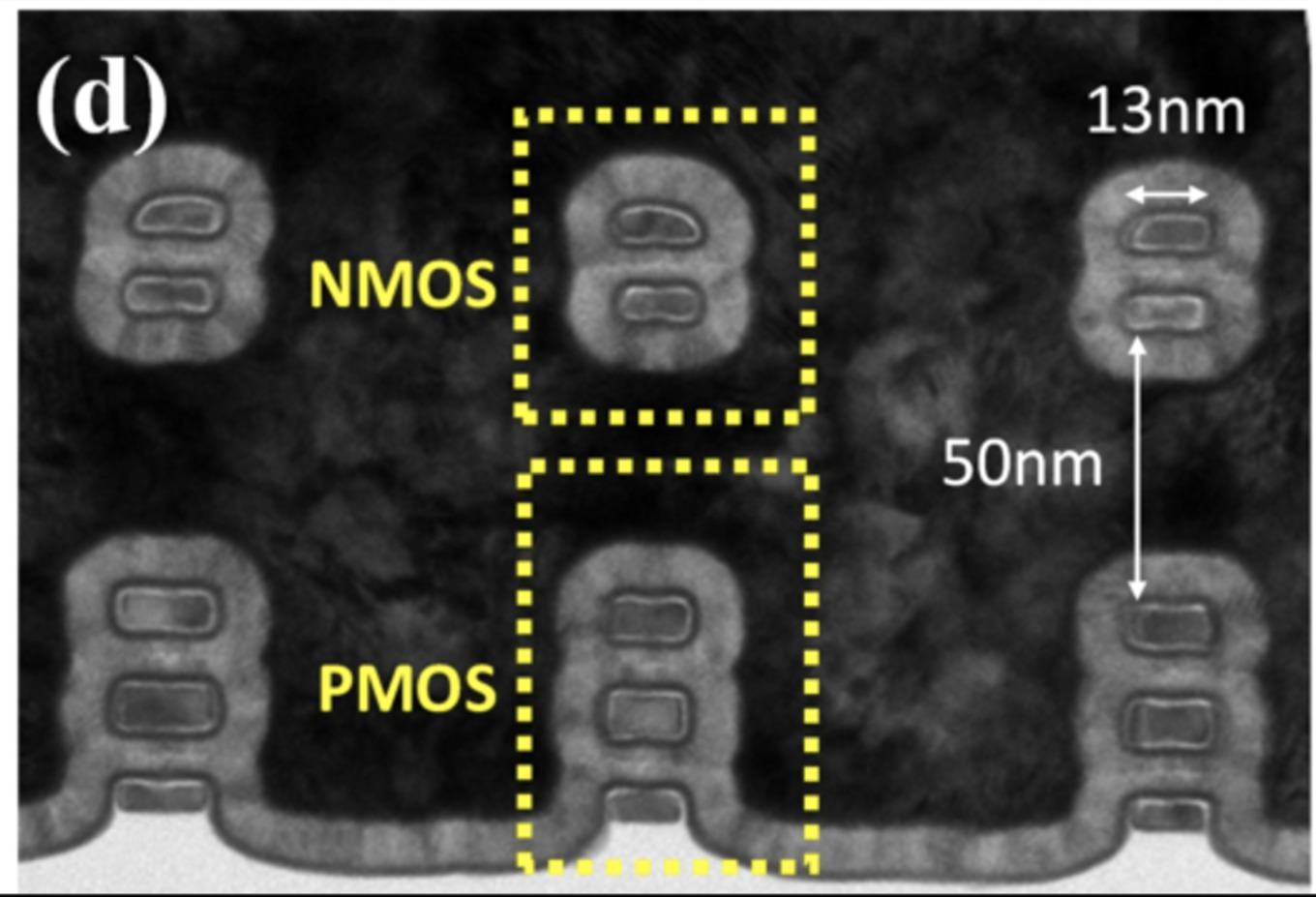

In immer wieder sich wiederholenden Schichten von Silizium und mit Germanium dotieren Silizium wird eine schmale Finne eingebracht, wo das Silizium-Germanium weggeätzt word, sodass eine beliebige Anzahl an Nanosheets übrig bleibt. Über die Anzahl der Nanosheets kann gesteuert werden, mit welcher Spannung der Transistoren arbeitet und wie viel Strom durch ihn hindurchgeleitet werden kann.

An dieser Stelle führt Intel nun einen weiteren Schritt ein: Die oberen beiden Nanosheets werden mit Phosphor dotiertem Silizium verbunden, um somit ein NMOS-Bauelement zu bilden. Die unteren beiden werden mit Bor dotiertem Silizium-Germanium verbunden, um ein PMOS-Bauelement zu erhalten.

Die Fertigung dieser Prozesse stellt laut Intel kein großes Problem dar. Nanosheet-Transistoren will man ohnehin fertigen. Die Aufteilung der Nanosheets soll ebenfalls ein gelöstes Problem sein. Allerdings muss Intel nun die Leistung der beiden Transistoren noch weiter optimieren, denn durch die Aufteilung des Nanosheet-Transistors kompromittiert man die Leistung der beiden einzelnen Bauteile.

Es wird noch einige Jahre dauern, bis Intel Nanosheet-Transistoren oder Gate-All-Around-Transistoren im Allgemeinen, in der Massenproduktion fertigen wird. Zuletzt ging Intel von mindestens fünf Jahren aus. Auch bei Samsung und TSMC arbeitet man an ähnlichen Technologien. Die Self-Aligned 3D Stacked Multi-Ribbon CMOS Transistoren aber bieten für Intel noch einmal ganz andere Möglichkeiten – vor allem hinsichtlich der Transistordichte. Bereits heute bestehen Chips aus verschiedenen Arten an Transistoren. Dies wird sich in der Zukunft so fortsetzen. GAA-Transistoren können besonders schnell sein und stellen eine Verbesserung der aktuellen FinFET-Transistoren dar. Self-Aligned 3D Stacked Transistoren ermöglichen eine hohe Packdichte, beispielsweise in den Caches und eventuellem SRAM. Von dieser Mischung verschiedener Transistor-Typen werden Intels zukünftige Prozessoren höchstwahrscheinlich Gebrauch machen.

Weitere Neuerungen auf dem IEDM von Intel

Zudem zeigte Intel auf dem IEDM erste High-Performance Short-Channel Gate-All-Around Transistoren, die Fertigung einer GaN NMOS/Si CMOS Integration auf einer 300-mm-Wafer und demonstrierte ein integriertes On-Die-Metall-Interconnect-System mit Luftspalten und speziellen Geometrien für die Leiterbahnen, um eine Steigerung der Interconnect-RC-Leistung zu erreichen.

Ebenfalls gezeigt wurden Sub-THz-Bauelemente auf einem organischen Subtrat, die für neue Vias-Prozesse verwendet werden sollen.