Werbung

Nicht nur AMD nahm an der 49. JPMorgan-Konferenz teil (und sprach dabei über Genoa und CDNA 2), auch Intel nutzte die Bühne für einige interessante Details. Dabei wiederholte Intel einige der Ansätze, die im Rahmen der IDM-2.0-Ankündigung bereits eine Rolle spielten.

So will Intel in seinen eigenen Möglichkeiten flexibler werden, aber auch seinen Kunden als Fertiger mehr Möglichkeiten bieten. So ist bereits bekannt, dass Intel für einige in 7 nm gefertigten Chips TSMC als Fertiger in Anspruch nehmen wird. Diese Chips werden dann von Intel selbst im Packaging zu einem Produkt zusammengebracht. Eben diese Möglichkeit will man offenbar seinen Kunden bieten.

"I've customers today that are saying, can I take my TSMC wafer and run it through your world leading packaged assembly and test? And the answer is yes."

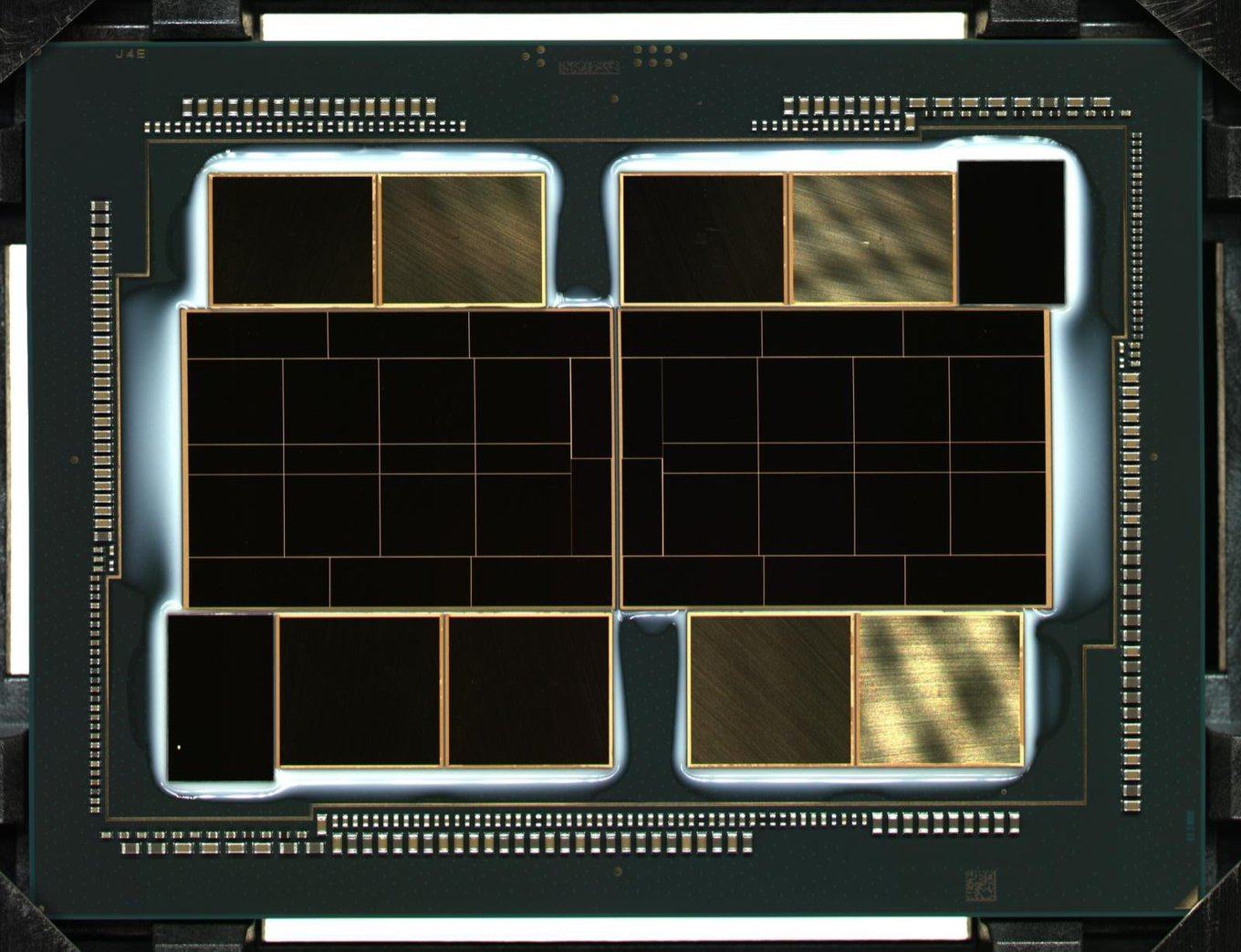

Beim Packaging geht es vor allem um Technologien wie Foveros und EMIB, die bisher nur exklusiv von Intel für die eigenen Produkte verwendet wurden. Offenbar deutet Intel hier an, dass auch externe Kunden diese verwenden können.

In der IDM-2.0-Ankündigung sprach Intel außerdem von einer möglichen Lizenzierung diverser weiterer IP von Intel durch externe Kunden. Dies wiederholte Pat Gelsinger auf der JPMorgan-Konferenz.

"We're also making all of our x86 and other core IP available, Intel graphics, Intel networking, Intel big core, Intel little core, things that were never made available before to foundry customers. Those are being made available for our foundries and we're seeing particular interest for what I'll call these hybrid designs from the large scale cloud guys."

Selbst die wichtigen Entwicklungen wie die CPU-Kerne will Intel möglichen Kunden gegenüber öffnen. Intel spricht von großem Interesse der Cloud-Anbieter. Ob und von welchem Hersteller wir dann beispielsweise Willow-Cove-, Golden-Cove- und später Ocean Cove-Kerne sehen werden, bleibt sicher die spannende Frage.

"So we're building on our packaging technologies with Foveros, EMIB, Co-EMIB, things that will lay out again later this year of how we're sustaining the package leadership. And then we got to line up the cores and we'll have a big and little cores, and they will have a yearly cadence as well, right."

Allem Anschein nach will Intel zum Tick-Tock-Rhythmus zurück. Das Tick-Tock-Modell wurde 2007 von Intel eingeführt und sollte Architektur-Verbesserungen und solche in der Fertigung im Wechsel durchführen. Ein Tick war immer dabei immer ein Fertigungsschritt, während der Tock die Verbesserung der Architektur bedeutete. Das Tick-Tock-Modell geriet aber 2013/14 aus den Fugen, spätestens mit Skylake ab 2015 sahen wir dann mehr Refreshes als geplante Wechsel in der Fertigung.

"I've set out a yearly cadence of process improvements. Also, we've restored our Tick-Tock product and core cadence." – so Gelsinger.

Ob es Intel tatsächlich gelingen wird den Weiterentwicklung in allen Bereichen auf diese Art wieder zu beschleunigen, bleibt abzuwarten. Den ersten Schritt will man aber bereits Ende 2021 mit Alder Lake sowie Sapphire Rapids machen, bevor dann 2022/23 die ersten Chips in 7 nm folgen sollen.