Werbung

Machine-Learning, bzw. AI-Anwendungen lassen sich in zwei Bereiche aufteilen. Im Training werden verschiedenste Eingabewerte so verarbeitet, dass sie über das Inferencing schnell wieder ausgewertet werden können. Für das autonome Fahren werden Videodaten ausgewertet und ein Netzwerk trainiert, damit die Erkennung der verschiedenen Situationen verbessert wird. Im Inferencing wird das Erlernte dann über die lokalen Systeme in den Fahrzeugen nur noch angewendet.

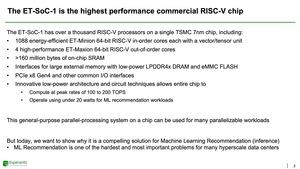

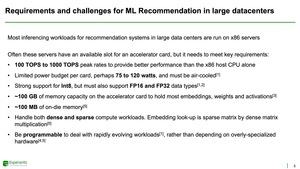

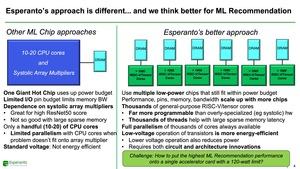

Esperanto hat mit dem ET-SoC-1 einen Chip entwickelt, der auf der RISC-V-Architektur basiert und auf das Inferencing ausgelegt ist. Chips wie der A100 von NVIDIA oder auch Ponte Vecchio von Intel sind sowohl auf das Training, als auch auf den Inferencing ausgelegt. Häufig ist die Effizienz im Inferencing aber nicht sonderlich hoch. Eben hier setzt der ET-SoC-1 an.

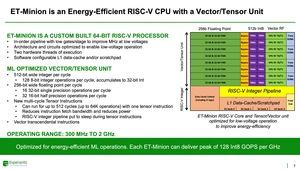

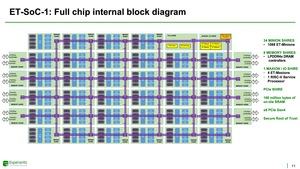

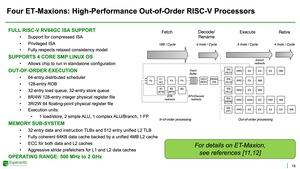

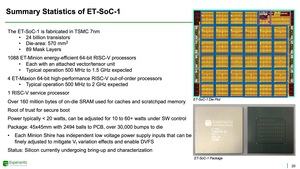

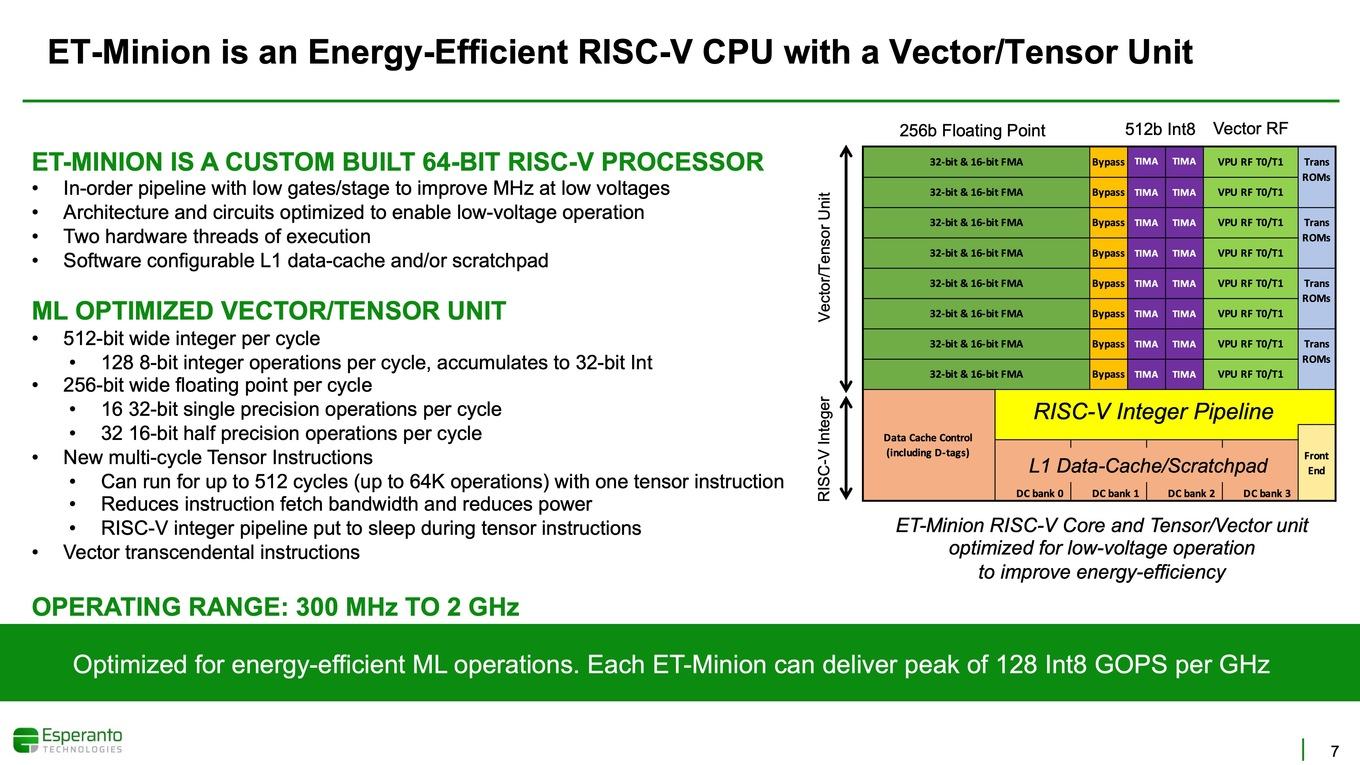

Auf dem ET-SoC-1 zum Einsatz kommen 1.088 energieeffiziente ET-Minion, so der Name der 64 Bit Out-of-Ordner-Kerne (RISC-V) mit jeweils einer Tensor-, bzw. Vektor-Einheit. Hinzu kommen vier Hochleistungskerne, ebenfalls im Out-of-Order-Design.

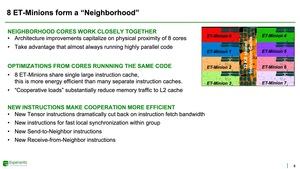

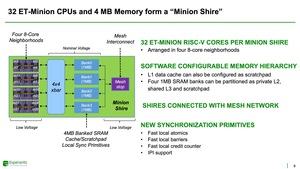

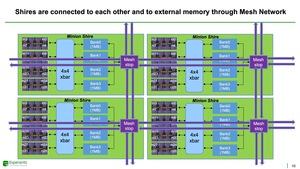

Die ET-Minion können 512 Bit an Integer-, 256 Bit an Fließkomma- oder Multi-Cycle Tensor-Instruktionen ausführen. Die Taktraten liegen bei 500 MHz bis 2 GHz. Organisiert sind die Kerne in Neighborhoods mit jeweils acht Kernen und vier dieser Neighborhoods wiederum zu Minion Shires, von denen sich 34x im ET-SoC-1 befinden. Ein Minion Shire mit acht Kernen teilt sich ein gemeinsames, 4 MB großes SRAM. 1 MB an L1-Cache können auch als privater L2-Cache oder geteilter L3-Cache angewendet werden. Ein Mesh-Netzwerk verbindet die 34 Minion Shires miteinander.

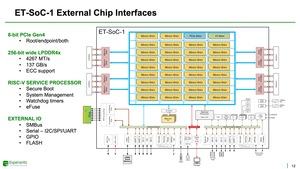

Die externe Anbindung findet über acht PCIe-4.0-Lanes statt. Außerdem gibt es acht LPDDR4X-Speichercontroller, an denen LPDDR4X-4267 eingesetzt werden kann. Die Speicherbandbreite liegt bei 137 GB/s. Ein ECC zum Speicher wird unterstützt.

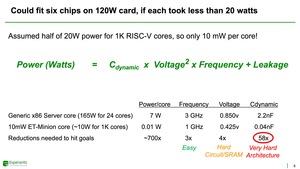

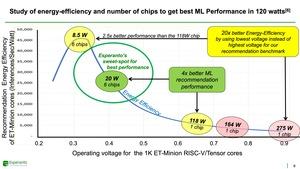

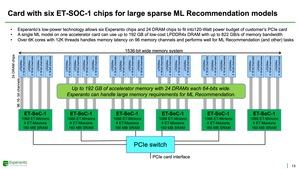

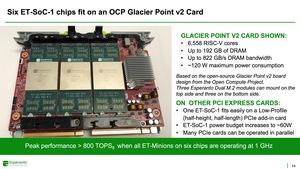

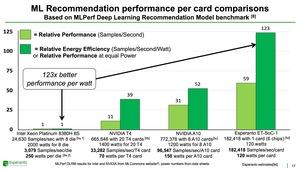

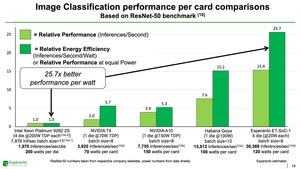

Der laut Espaeranto ideale Betriebspunkt des ET-SoC-1 sind gerade einmal 20 W. Dann arbeitet der Chip am effizientesten. Diesen Betriebspunkt hat Esperanto auch gewählt, um sechs ET-SoC-1 auf einer Glacier-Point-V2-Karte unterzubringen. Diese kommt dann auf 120 W, vor allem aber erreicht eine solche Karte die mehrfache Leistung der sonst üblichen Inferencing-Beschleuniger von NVIDIA oder den x86-Prozessoren von Intel. Die Leistungsaufnahme des Chips kann von 10 bis 60+ W angepasst werden.

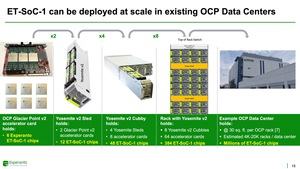

Zwei Glacier-Point-V2-Karten sollen in einem OCP-Datacenter in einem Schlitten untergebracht werden, vier der Schlitten in einem Cubby. Diese wiederum finden in einem Rack ihren Platz, welches dann 384 ET-SoC-1 beinhaltet.

Die Fertigung des ET-SoC-1 erfolgt in 7 nm bei TSMC. Bei 24 Milliarden Transistoren kommt der Chip auf eine Größe von 570 mm². Das Package misst 45 x 45 mm. Zum Board stellt der Chip über 2.494 BGAs den Kontakt, im Package sind es mehr als 30.000 Bumps.

Derzeit befindet sich Esperanto noch in der Evaluierungsphase deds ET-SoC-1. Die ersten Chips sind aus der Fertigung zurück und werden aktuell getestet.