Werbung

Die European Processor Initiative (EPI) macht einen ersten erfolgreichen Schritt hin zu HPC-Hardware, die in Europa entwickelt und später auch betrieben wird. Für den EU-Prozessor fährt man dabei mehrgleisig und will die Hardware auf verschiedene Architektur-Beine stellen. Zentrale Komponente wird ein Rhea-HPC-SoC auf Basis von 72 Arm-Kernen nebst HBM2 sein. Doch es werden auch spezielle Beschleuniger entwickelt, die auf RISC-V basieren. Eben solche haben nun den Tape Out geschafft, wurden also erstmals gefertigt und werden nun getestet.

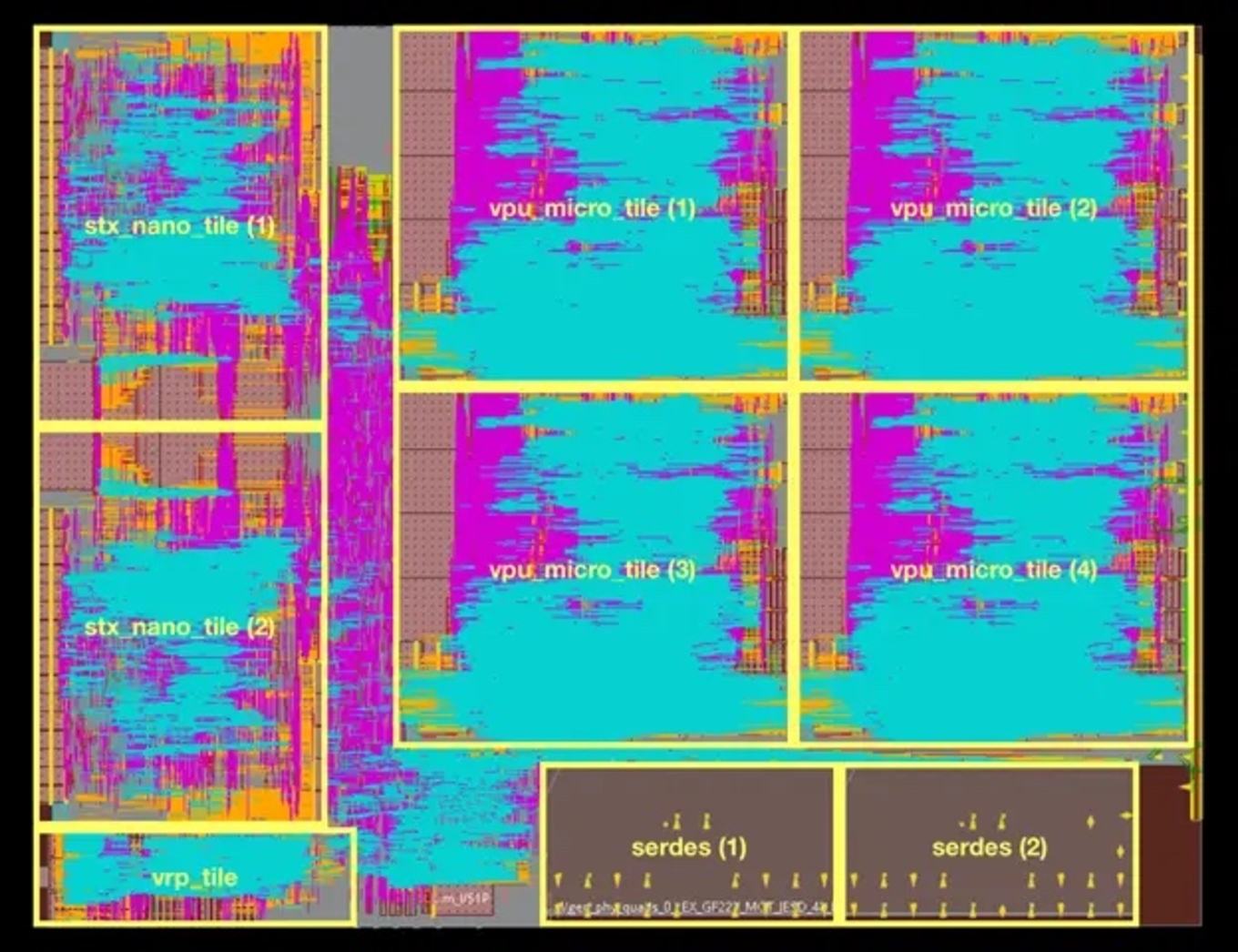

Die ersten Samples des EPAC1.0 RISC-V Testchip wurden bei GlobalFoundries in 22FDX hergestellt. Es handelt sich dabei um kleine High-End-Fertigung, wie wir sie von Samsung, TSMC oder Intel kennen, 22FDX ist von GlobalFoundries aber auf Kosten und Effizienz ausgelegt. 143 fertig mit einem Package versehene Chips werden gefertigt. Diese kommen jeweils auf eine Größe von 26,97 mm². Die Anzahl der Transistoren gibt EPI nicht an, spricht jedoch von 14 Millionen sogenannten Placeable Instances, was dem Äquivalent von 93 Millionen Gates entspricht. Sowohl Größe als auch Komplexität sind nicht mit Beschleuniger-Chips vergleichbar, die sonst bereits auf dem Markt sind. Es handelt sich um Testchips, die intern sechs unterschiedliche Beschleuniger aufweisen – in dieser Form handelt es sich also nicht um ein finales Produkt. Außerdem ist angedacht eine weitere Generation bereits in 12 nm zu fertigen.

Der aus sechs Bereichen bestehende Chip umfasst einen RISC-V-Kern, einen Variable Precision Prozessor (VRP), eine Vektorerweiterung, einen Stencil-Beschleuniger, einen Tensor-Beschleuniger und eine sogenannte Home Node mit dem L2-Cache. Alle Komponenten wurden von unterschiedlichen Firmen oder Instituten, allesamt über Europa verteilt, entwickelt und im EPAC1.0 RISC-V Testchip zusammengeführt.

Die Testchips arbeiten zunächst mit einer Taktfrequenz von 1 GHz. Hier wird man ebenfalls für das finale Design sicherlich höhere Taktfrequenzen anstreben. Im Labor konnten die ersten Programme auf dem Chip ausgeführt werden, nun geht es daran die einzelnen Tiles zu evaluieren – zu schauen, ob sie in Hardware die Simulationen bestätigen können. Für die einzelnen Beschleuniger-Einheiten muss dann noch bestimmt werden, wie wichtig sie im jeweiligen Verhältnis zueinander sind und in welchem Umfang sie dann im finalen Design eine Rolle spielen.

2022 soll der Rhea-HPC-SoC in seiner finalen Form vorgestellt werden. Zum Einsatz kommt hier ein Neoverse-Design von ARM, welches um entsprechende Vektoreinheiten ergänzt wurde. Ziel ist es sich unabhängig von Herstellern außerhalb Europas zu machen. Für das Design ist dies durchaus realistisch, allerdings weniger hinsichtlich der Fertigung.