Werbung

Im Rahmen eines Linux-Treiberupdates für AMDs EDAC (Error Detection and Correction) haben die entsprechenden Ingenieure offenbart, dass die zukünftigen EPYC-Prozessoren auf Basis der Zen-4-Architektur zwölf Speicherkanäle haben werden. Dies entspräche einer Steigerung von 50 % gegenüber der aktuellen Generation mit acht Kanälen.

An diese Speicherkanäle kann klassischer DDR5 angebunden werden, aber auch RDDR5 (Registered DDR5) und LRDDR5 (Load-Reduced DDR5). Der LRDDR5 wird analog zu LRDIMM bei DDR4 zum Einsatz kommen. Samsung hat DDR5-Module mit einer Kapazität von 512 GB geplant. Bei 12 Speicherkanälen und zwei Modulen pro Kanal wären somit 12 TB möglich – sollten die entsprechenden DDR5-Module in dieser Form erscheinen und der Maximalausbau so auch zur Anwendung kommen.

Anfang November präsentierte AMD seine Roadmap die kommende EPYC-Generation. Die EPYC-Prozessoren mit Zen-4-Kernen (Genoa) werden bis zu 96 Cores bieten. In einem angepassten Design alias Bergamo soll es 128 Zen-4c-Kerne sein. Wann im kommenden Jahr diese Prozessoren auf den Markt kommen werden, ist nicht bekannt.

Update:

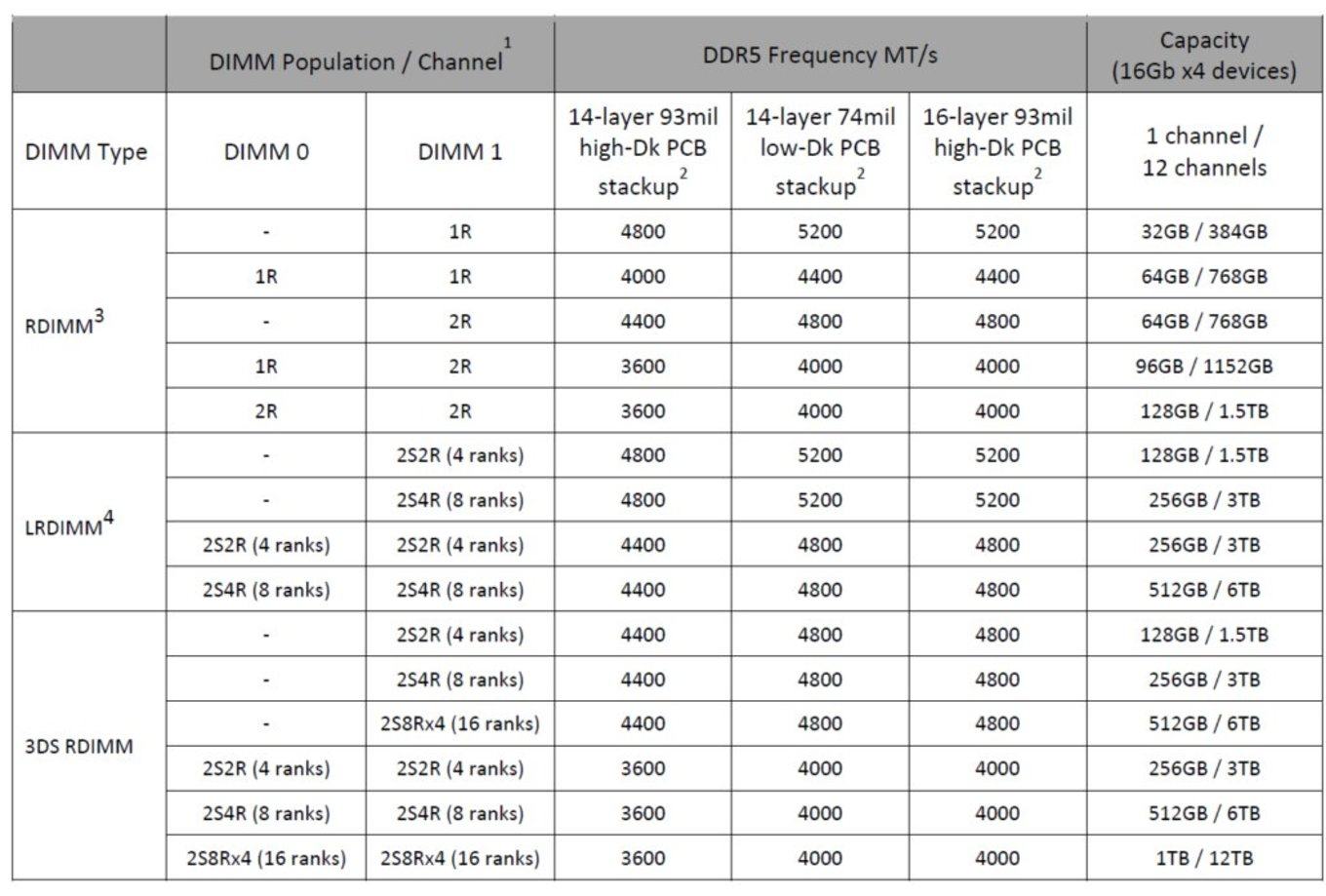

Aus dem Leak bei Gigabyte stammt ein Dokument, welche die Speicherunterstützung der EPYC-Prozessoren auf Basis des Genoa-Designs, sprich Zen 4, aufführt:

Je nach Speichertyp (RDIMM, LRDIMM oder 3DS RDIMM) und der Anzahl der Ranks sowie der Bestückung werden Transferrate von 3.600 bis 5.200 MT/s erreicht. Für DDR5-5200 sind allerdings nur maximal 3 TB möglich, während DDR5-4800 auch 6 TB erlaubt. Die maximalen 12 TB werden nur mit DDR5-4000 erreicht.