Werbung

Zur Hot Chips 33 im vergangenen Sommer veröffentlichte IBM die ersten Details zum Telum – einem 5+-GHz-Prozessor mit acht Kernen und einer völlig neuen Cache-Struktur. Nun, zur ISSCC 2022, konzentrierte sich IBM auf eine Beschreibung des Prozessors, wie die Cache-Struktur funktioniert und wie die virtuellen L3- und L4-Caches aufgebaut sein können.

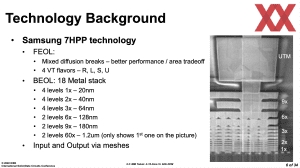

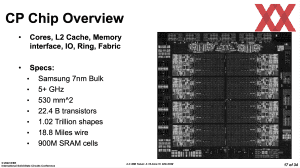

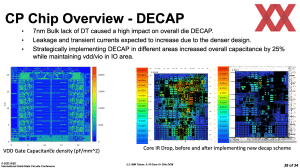

Zunächst gibt es einen Blick auf die Fertigung. Diese findet bei Samsung in 7 nm (7HPP) statt. Insgesamt ist der Prozessor aus 19 Schichten aufgebaut. Es gibt ein FEOL (Fron-End of Line) und einen Metal Stack bestehend aus 18 Schichten des BEOL (Back-End of Line). IBM beschreibt diese Schichten in den verschiedenen Größenleveln von 1,2 µm bis 20 nm. Bei 22,5 Milliarden Transistoren kommt der IBM Telum auf eine Fläche von 530 mm².

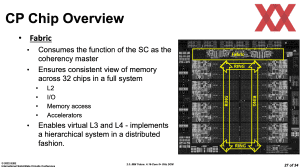

Den bei der vorherigen Generation gewählte Aufbau mit vier Central Processor (CP) und einem System Controller (SC) lässt IBM hinter sich. Ein einzelnes CPU-Design ist das Rückgrat und geht in weiten Bereichen einen (für IBM) neuen Weg. Mehr Kerne und mehr Cache auf gleichem Raum waren das Entwicklungsziel.

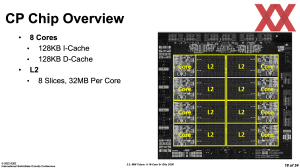

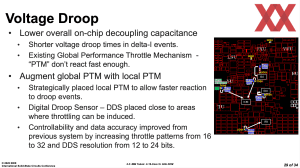

Einer der zentralen Bausteine des Prozessors sind die acht Out-of-Order-Kerne. Diese können per SMT2 jeweils zwei Threads ausführen. Für jeden Kern sieht IBM einen 32 MB großen L2-Cache vor, der zunächst exklusiv jedem CPU-Kern zur Verfügung steht. An L1-Cache vorhanden sind 128 kB an Instruction-Cache und 128 kB an Data-Cache. Auch die Zugriffe auf den L2-Cache sollen dank vier Pipelines und nur 19 Taktzyklen (3,8 ns) für ein komplettes Schreiben des Caches besonders schnell sein. Gemeinsam über alle Kerne können diese 8x 32 MB als 256 MB großer virtueller L3-Cache verwendet werden. Die Latenz von 3,8 ns zum privaten L2-Cache sowie 12 ns für Zugriffe auf den gemeinsamen L3-Cache sollen laut IBM deutlich schneller sein, als das, was AMD (Milan) und Intel (Ice Lake) anzubieten haben.

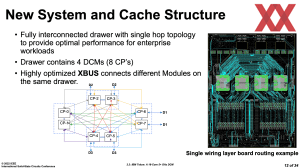

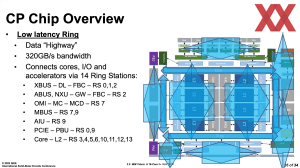

Für den L2-Cache kommt ein Ring-Interconnect mit 14 Ring-Stationen zum Einsatz, der eine Bandbreite von 320 GB/s anzubieten hat. Die Kerne, aber auch die weiteren Kommunikationsschnittstellen, sind Stops des Ring-Interconnects. Außerdem gibt es einen MBUS, der zwei der Chips auf einem Package miteinander verbindet. Dieser kommt auf eine Bandbreite von 224 GB/s.

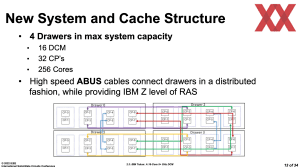

Ein XBUS und ABUS dient der Anbindung mehrerer Chips miteinander. Sechs XBUX-Schnittstellen kommen auf jeweils 46 GB/s. Ein weiterer ABUS kommt auf 35 GB/s. Über den Interconnect mehrere Chips wird der virtuelle L4-Cache aufgebaut. Bis zu acht Chips werden hier zusammengefasst: 8x 256 MB ergeben 2 GB an L4-Cache.

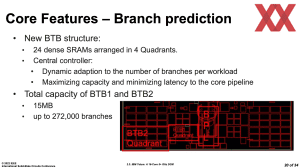

Ein weiterer Fokus lag auf der Sprungvorhersage. So gibt es zwei Branch Target Buffer (BTB) mit jeweils 15 MB, die bis zu 272.000 Sprungvorhersagen vorhalten können. Die BTB sind in vier Quadranten zu jeweils sechs SRAM-Bereichen organisiert. IBM ist hier im Vergleich zum Vorgänger von EDRAM auf SRAM gewechselt, der bis zu viermal dichter gepackt werden kann. Insgesamt befinden sich 900 Millionen SRAM-Zellen auf dem Chip.

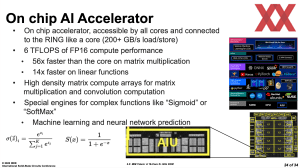

Um die acht CPU-Kerne in gewissen Aufgabenbereiche zu entlasten, verbaut IBM einen AI-Beschleuniger pro Chip. Dieser erreicht eine Rechenleistung von 6 TFLOPS für halbe Genauigkeit (FP16). Auch dieser AI-Beschleuniger ist an den Ring-Interconnect angeschlossen und kann Daten mit 200 GB/s aufnehmen. Die FP16-Berechnungen sind in der Berechnung um den Faktor 56 schneller als in einem der Kerne. Für lineare Berechnungen spricht IBM von einer Beschleunigung um den Faktor 14.

Noch einmal zum Packaging: Zwei der CPs (Central Processor) sitzen auf einem Package und das relativ dicht beieinander. Der Abstand zwischen den Chips beträgt nur 500 µm. Verbunden sind die Chips über den schon erwähnten MBUS mit 224 GB/s. Dies geschieht über einen 1.416 Bit breiten Bus bei voller Taktfrequenz von 5+ GHz.

Dabei ist es nicht so einfach, zwei Chips derart eng zu packen. Aus Sicht der Kommunikation will man sie natürlich so dicht zusammen wie möglich auf das Package setzen. Die mechanische Beanspruchung ist hoch, da sich das Laminate und Silizium anders ausdehnen. Die Kühlung wird über ein Thermal Interface Material (TIM) übernommen, ein Kupfer-Heatspreader nimmt die Abwärme zunächst auf und eine Wasserkühlung führt diese dann ab.

Insgesamt erwartet sich IBM eine um 10 % höhere Single-Threaded-Leistung. Die Systemleistung soll um 25 % höher ausfallen – wenngleich der Aufbau ein anderer ist und sich dies nicht zwangsläufig 1:1 vergleichen lassen kann.