News und Artikel durchsuchen

{{#data.error.root_cause}}

{{/data.error}}

{{^data.error}}

{{#texts.summary}}

[{{{type}}}] {{{reason}}}

{{/data.error.root_cause}}{{texts.summary}} {{#options.result.rssIcon}} RSS {{/options.result.rssIcon}}

{{/texts.summary}} {{#data.hits.hits}}

{{#_source.featured}}

FEATURED

{{/_source.featured}}

{{#_source.showImage}}

{{#_source.image}}

{{/_source.image}}

{{/_source.showImage}}

{{/data.hits.hits}}

{{{_source.title}}} {{#_source.showPrice}} {{{_source.displayPrice}}} {{/_source.showPrice}}

{{#_source.showLink}} {{/_source.showLink}} {{#_source.showDate}}{{{_source.displayDate}}}

{{/_source.showDate}}{{{_source.description}}}

{{#_source.additionalInfo}}{{#_source.additionalFields}} {{#title}} {{{label}}}: {{{title}}} {{/title}} {{/_source.additionalFields}}

{{/_source.additionalInfo}}

ISSCC

-

ISSCC 2024: Warum AMDs Zen-4c-Kern sogar schneller als der große Bruder sein kann

Mit den für Cloud-Anwendungen optimierten EPYC-Prozessoren mit Codenamen Bergamo sowie einigen Ryzen-Prozessoren für das Notebook-Segment präsentierte AMD im vergangenen Jahr die Zen-4c-Kerne. In Teilen sind wir damals bereits darauf eingegangen, wie es AMD schafft, doppelt so viele Kerne auf dem CCD unterzubringen. Mit bis zu 128 Kernen spielt dies für die EPYC-Prozessoren eine wichtige Rolle, aber natürlich darf auch die... [mehr]

Mit den für Cloud-Anwendungen optimierten EPYC-Prozessoren mit Codenamen Bergamo sowie einigen Ryzen-Prozessoren für das Notebook-Segment präsentierte AMD im vergangenen Jahr die Zen-4c-Kerne. In Teilen sind wir damals bereits darauf eingegangen, wie es AMD schafft, doppelt so viele Kerne auf dem CCD unterzubringen. Mit bis zu 128 Kernen spielt dies für die EPYC-Prozessoren eine wichtige Rolle, aber natürlich darf auch die... [mehr] -

ISSCC 2022: Design-Herausforderungen einer neuen System- und Cache-Struktur

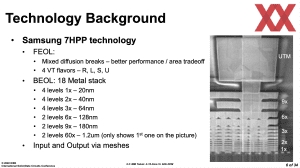

Zur Hot Chips 33 im vergangenen Sommer veröffentlichte IBM die ersten Details zum Telum – einem 5+-GHz-Prozessor mit acht Kernen und einer völlig neuen Cache-Struktur. Nun, zur ISSCC 2022, konzentrierte sich IBM auf eine Beschreibung des Prozessors, wie die Cache-Struktur funktioniert und wie die virtuellen L3- und L4-Caches aufgebaut sein können. Zunächst gibt es einen Blick auf die Fertigung. Diese findet bei Samsung in 7 nm (7HPP) statt... [mehr].

Zur Hot Chips 33 im vergangenen Sommer veröffentlichte IBM die ersten Details zum Telum – einem 5+-GHz-Prozessor mit acht Kernen und einer völlig neuen Cache-Struktur. Nun, zur ISSCC 2022, konzentrierte sich IBM auf eine Beschreibung des Prozessors, wie die Cache-Struktur funktioniert und wie die virtuellen L3- und L4-Caches aufgebaut sein können. Zunächst gibt es einen Blick auf die Fertigung. Diese findet bei Samsung in 7 nm (7HPP) statt... [mehr]. -

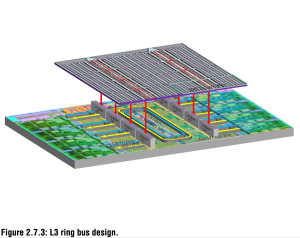

ISSCC 2022: AMD nennt Details zum 3D V-Cache und Ringbus (Update)

Noch ist der bisher wohl einzig geplante Ryzen-Prozessor (Ryzen 7 5800X3D) der aktuellen Generation mit 3D V-Cache nicht auf dem Markt, da nennt AMD auf der ISSCC 2022 einige Details zur Umsetzung, die über das hinaus gehen, was wir bisher schon wissen. Ein kleiner Rückblick: In der Cache-Hierarchie die größte Änderung in der Zen-3-Architektur sind der gemeinsame L3-Cache mit einer Kapazität von 32 MB für bis zu acht Kerne. Der Core... [mehr]

Noch ist der bisher wohl einzig geplante Ryzen-Prozessor (Ryzen 7 5800X3D) der aktuellen Generation mit 3D V-Cache nicht auf dem Markt, da nennt AMD auf der ISSCC 2022 einige Details zur Umsetzung, die über das hinaus gehen, was wir bisher schon wissen. Ein kleiner Rückblick: In der Cache-Hierarchie die größte Änderung in der Zen-3-Architektur sind der gemeinsame L3-Cache mit einer Kapazität von 32 MB für bis zu acht Kerne. Der Core... [mehr] -

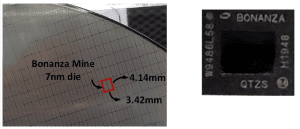

ISSCC 2022: Intel nennt Details zum Bitcoin-ASIC

Auf der International Solid-State Circuits Conference (ISSCC) hat Intel weitere Details zu ersten Generation seines Bitcoin-ASIC "BonanzaMine" bekanntgegeben. Vor einigen Wochen wurden entsprechende Gerüchte bekannt, obwohl Intel bereits seit einiger Zeit auch öffentlich darüber Informationen preisgab. Die Gerüchte bezogen sich dabei wohl vor allem auf eine Ankündigung spezieller Blockchain- und Krypto-Chips, zu denen Intel wenige... [mehr]

Auf der International Solid-State Circuits Conference (ISSCC) hat Intel weitere Details zu ersten Generation seines Bitcoin-ASIC "BonanzaMine" bekanntgegeben. Vor einigen Wochen wurden entsprechende Gerüchte bekannt, obwohl Intel bereits seit einiger Zeit auch öffentlich darüber Informationen preisgab. Die Gerüchte bezogen sich dabei wohl vor allem auf eine Ankündigung spezieller Blockchain- und Krypto-Chips, zu denen Intel wenige... [mehr] -

Quest: Schichten im SRAM Neural Prozessor sprechen per Induktionsschleifen

Für die Steigerung der Rechenleistung moderner Prozessoren sind möglichst viele Datenverbindungen essentiell – gleiches gilt für die Anbindung von schnellem Speicher. Im Falle von High Bandwidth Memory verwenden die meisten Hersteller sogenannte Through-Silicon Vias (TSVs). Bei den TSVs handelt es sich um eine Halbleitertechnik, die durch das Silizium-Substrat geführt wird. Neben der enorm komplizierten Fertigung dieser TSVs bestehen... [mehr]

Für die Steigerung der Rechenleistung moderner Prozessoren sind möglichst viele Datenverbindungen essentiell – gleiches gilt für die Anbindung von schnellem Speicher. Im Falle von High Bandwidth Memory verwenden die meisten Hersteller sogenannte Through-Silicon Vias (TSVs). Bei den TSVs handelt es sich um eine Halbleitertechnik, die durch das Silizium-Substrat geführt wird. Neben der enorm komplizierten Fertigung dieser TSVs bestehen... [mehr]