Werbung

Vor zwei Jahren stellte das in London ansässige Start-up Graphcore die Mk2 GC200 Intelligence Processing Unit (IPU) vor. Mit 59,4 Milliarden Transistoren auf einer Fläche von 823 mm², gefertigt in 7 nm bei TSMC, war die zweiten Generation der Angriff auf die etablierten Hersteller und hier vor allem NVIDIA.

Im vergangenen Jahr präsentierte Graphcore weitere Details, wie das Vorhandensein von 1.472 IPU-Cores, die 8.832 separate Compute-Threads verarbeiten können. Hinzu kommen 900 MB an SRAM, eine externe Anbindung von DDR4 sowie ein eigener Interconnect, der vier IPUs mit bis zu 2,8 TBit/s untereinander verbindet.

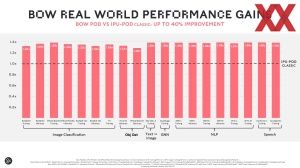

Nun stellte Gaphcore die dritte IPU-Generation vor. Diese soll eine um 40 % höhere Leistung als der Vorgänger bieten können. Bei der Effizienz soll es um 16 % vorwärts gehen.

Doch im Grund bei vieles beim Alten – auf den ersten Blick zumindest. Für Nutzer der IPU Pods ändert sich nichts. Es sind keinerlei Änderungen notwendig, damit die Software auch auf den neuen Bow-IPUs arbeitet. Auch am Preis soll sich nichts ändern. Ein IPU Pod mit 16 Beschleunigern kostete bisher etwa 150.000 US-Dollar und dies soll auch für die neue Generation der Fall sein.

Aber auch bei den eigentlichen IPUs tut sich auf den ersten Blick nichts. Der Prozessor besteht weiterhin aus 1.472 sogenannten IPU-Cores, die wiederum 8.832 separate Compute-Threads verarbeiten können. Man könnte hier also in gewisser Weise von einem SMT6 (Simultaneous Multithreading mit sechs Threads pro Kern) sprechen. Die Recheneinheiten der Bow-IPU sind auf die Berechnungen eines eigenen Datenformats optimiert. Graphcore nennt dies AI-Float und es wird versucht, alle Berechnungen nicht größer als 16 Bit werden zu lassen, um möglichst effektiv zu arbeiten. Die Recheneinheiten unterstützen außerdem FP32, FP16.32 (16 Bit Multiply mit 32 Bit Accumulate) und FP16.16 (16 Bit Multiply und Accumulate). Wie die Recheneinheiten der GA100-GPU von NVIDIA unterstützen die IPU-Cores Sparsity/Sparse Matrix oder die dünnbesetzte/schwachbesetzte Matrizen. Besteht eine Matrix aus sehr vielen mit Nullen besetzten Einträgen, können über verschiedene Techniken diese Bereiche in der Berechnung und Speicherung effizienter genutzt werden.

Die IPU-Cores können auf 900 MB In-Processor Memory zurückgreifen. Der SRAM verteilt sich über die IPU-Cores, die in IPU-Tiles organisiert sind. Die kumulierte Bandbreite beträgt 65 TB/s. In den Bow-Pods werden jeweils vier Bow-IPUs mittels eines IPU-Gateway miteinander verbunden. Dazu verfügen die Chips über 10 IPU-Links mit einer Bandbreite von 320 GB/s. An diesem IPU-Gateway-Chip können zudem DDR4- und NVMe-Speicher angebunden werden.

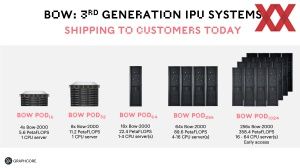

Die Bow Pods gibt es in Ausführungen mit 16, 32, 64, 256 und 1.024 IPUs. Vier Bow-IPUs befinden sich in einem Bow-2000 getauften System, in dem sich auch ein Prozessor befindet. Einen IPU Pod Classic mit 32 IPUs gab es bislang nicht, dieser wird nun als Zwischenstufe eingeführt. Die Bow Pods sind ab sofort verfügbar. Einzig das große Pod-1.024-System gibt es zunächst nur im Early-Access-Programm.

| Anzahl IPUs | GC2000 IPU | Bow-2000 IPU |

| 16 | 4 PFLOPS | 5,6 PFLOPS |

| 32 | - | 11,2 PFLOPS |

| 64 | 16 PFLOPS | 22,4 PFLOPS |

| 256 | 64 PFLOPS | 89,6 PFLOPS |

| 1.024 | 256 PFLOPS | 358,4 PFLOPS |

Dies sind die theoretischen Rechenleistungen der Chips, die in einer gewissen Anzahl zum Einsatz kommen. Für Systeme bis hunderten Chips wichtig, ist eine gute Skalierung. In dieser Hinsicht sah sich Graphcore schon auf einem guten Pfad, den man nun mit den neuen IPUs weiter fortsetzen kann.

Die rein theoretischen +40 % an Leistung belegt Graphcore mit eigenen Zahlen im Vergleich zum Vorgänger-IPU. Die Spanne reicht hier von 29 bis 39 % für wichtige AI-Anwendungen wie BERT, ResNet, GPT2, FastSpeech und mehr. Das Leistungsplus wird durch einen von 1,25 GHz ausgehend auf 1,85 GHz höheren Takt des Prozessors erreicht. Zugleich wird die Spannung reduziert, mit der der Chip betrieben wird. Graphcore beanspruchte schon mit der Vorgänger-Generation gewisse Vorteile gegenüber der Konkurrenz aus dem Hause NVIDIA. Schneller und zugleich kostengünstiger sollten die IPU-Systeme sein. Allerdings muss man hier ein paar Einschränkungen machen, denn sicherlich gibt es Anwendungen, in denen sich der Leistungsunterschied genau so darstellt, dies bedeutet aber nicht, dass man dies generell übertragen kann. Wie wir in den letzten Veröffentlichungen des MLPerf V1.1 sehen konnten, interpretiert jeder Hersteller die Ergebnisse anders. Natürlich soll die eigene Hardware immer bestmöglich dargestellt werden.

Aber wie immer bei Hersteller-Benchmarks: Diese sind mit Vorsicht zu genießen, was aber nicht nur bei Graphcore gilt, sondern auch bei den Daten, die AMD, Intel und NVIDIA veröffentlichen, der Fall ist.

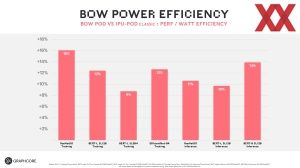

Schlussendlich hat Graphcore auch noch Daten, die eine Steigerung der Effizienz belegen sollen. Hier wurde der IPU-Pod16 gegen einen neuen Bow Pod16 gestellt. Für die Leistung auf den Verbrauch bezogen, erreicht das neue Bow-basierte System in den verschiedenen Anwendungen eine um 9 bis 16 % bessere Effizienz.

Erster Prozessor mit 3D Wafer-on-Wafer

Doch wie erreicht Graphcore das Leistungs- und Effizienzplus? Die Bow-IPU ist der erste Prozessor, der ein Verfahren namens 3D Wafer-on-Wafer verwendet. Graphcore hat dazu mit TSMC zusammengearbeitet und ließ hier auch schon die Vorgänger-IPU fertigen – greift nun auch auf eine SoIC-WoW-Technologie zurück, die wir nun genauer beschreiben wollen.

Das Verfahren sieht wie folgt aus: Der Wafer mit den IPUs wird wie gewohnt belichtet und darauf befinden sich etwa 60 Colossus-Chips (so der Name der Dies mit den IPUs). Auf Seiten der Back-end of line (BEOL), also dort, wo in mehreren Metallschichten und Bahnen der Kontakt zu den Bumps hergestellt wird, wird nun ein zweiter Wafer aufgebracht. Dieser enthält keinerlei aktive Transistoren, dafür aber wird über diesen Power Delivery Wafer die Strom- und Spannungsversorgung hergestellt.

Im Power Delivery Wafer gefertigt bzw. vorhanden, sind unter anderem Deep Trench Capacitor (DTC). Diese DTCs sind vertikal arrangierte Halbleiterbauelemente, die zur Kapazitätserweiterung eingesetzt werden. Ein Vorteil der DTCs gegenüber Kondensatoren die sich auf dem Package (bzw. dessen Rückseite) befinden ist, dass sie frei und so nah wie möglich an der gewünschten Schaltung (den eigentlichen IPU-Chips) platziert werden können. Zudem bieten DTCs eine höhere Kapazität pro Fläche als andere Lösungen, wie beispielsweise Metal-Insulator-Metal-Kondensatoren (MIM), wie sie bei Intel für die 10-nm-Technik (Intel 7) zum Einsatz kommen.

Der Aufbau sieht also wie folgt aus: Über die C4-Bumps wird der Chip mit dem Package verbunden. Eine Under-Bump Metallisierung (UBM) dient als Kontaktschicht. Back-side Through Silicon Vias (BTSV) führen von dieser direkt bis zur BEOL, um hier den Kontakt zwei BEOL der IPU-Wafer herzustellen. Die DTCs stellen an Reservoir an Ladung dar, welches von den IPU-Dies abgefragt werden kann.

Die beiden Wafer werden unabhängig voneinander gefertigt und dann zusammengeführt. Sind sie miteinander verbunden, wird der Power Delivery Wafer abgeschliffen, um darauf die UBM aufzubringen. Liegen die beiden 300-mm-Wafer übereinander und ist der obere abgeschliffen, werden die Chips darauf geschnitten.

Eines der Probleme im Wafer-on-Wafer-Verfahren ist die Tatsache, dass die Chips nicht erst getestet werden können. Die beiden Wafer werden miteinander verbunden, dann die einzelnen Chips daraus geschnitten und erst dann kann ein Testen der Chips stattfinden. Ist die Ausbeute der Chips nicht sonderlich hoch, vergeudet man natürlich viele Ressourcen auf ein Verfahren, bei dem am Ende kein funktionsfähiger Chip herauskommt.

An dieser Stelle kommen beim Bow-IPU mehrere Dinge zum Tragen. Zum Einen lässt Graphcore die IPU-Wafer weiterhin in 7 nm (TSMC N7) fertigen und die Ausbeute sollte hier inzwischen recht gut sein. Zum Zweiten besitzen die IPUs einen hohen Grad an redundanten Blöcken. Pro Chip sind am Ende 1.472 Kerne funktionsfähig, auf der Chipfläche werden aber weitaus mehr gefertigt. Gleiches gilt für die 900 MB an SRAM, die vorhanden sind. Auch diese sind in einem gewissen Anteil redundant vorhanden. Fehler in der Fertigung können so in gewisser Weise ausgeglichen werden.

Auf der ISSCC 2022 sprach Intel über die Wiederherstellbarkeit in der Fertigung für die Chips der nächsten Xeon-Generation. Solche Verfahren kommen auch für die Bow-IPUs zum Einsatz.

Bow-2000 IPU Machine und Ausblick

Laut Graphcore können die ersten Systeme auf Basis der Bow-IPUs ab sofort ausgeliefert werden. Der Preis ist identisch zu den Ausbaustufen des Vorgängers.

Als Basis eines Systems mit den neuen IPUs dient ein Bow-2000 getaufter Knoten mit vier Bow-IPUs. 16 IPU-Maschines mit jeweils vier Bow-IPUs können in ein Rack gepackt werden und nennen sich dann Bow-POD64. Die IPU-Maschines arbeiten komplett eigenständig von bestehenden Systemen und können als solche betrieben werden. Einzig zur Speicherung und dem Lesen der Daten der AI-Anwendungen sind noch Standard-Systeme notwendig.

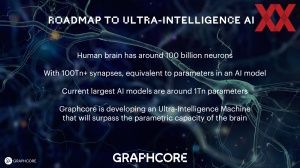

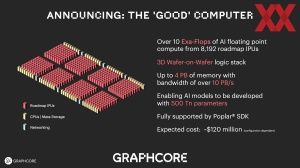

Perspektivisch plant Graphcore den Aufbau eines "Good"-Computers. Dieser soll die nächste Generation der IPUs verwenden und aus bis zu 8.192 IPUs aufgebaut sein. AI-Modelle mit 500 Billionen (amerikanisch 500 trillion, 500.000.000.000.000) Parametern sollen darauf verarbeitet werden können. 120 Millionen US-Dollar würde ein solches System nach heutigen Berechnungen kosten.

Aus technischer Sicht sind die IPUs von Graphcore interessant und sie bedienen scheinbar auch einen gewissen Markt an AI-Anwendungen, den sie als darauf ausgelegte Hardware auch gut bedienen können. Doch nun fehlt es an Kunden und Durchsetzungskraft, denn wenn Entwickler und Anwender die Wahl zwischen zwei inkompatiblen Systemen haben, dann entscheiden sie sich meist für das, mit der größten Marktmacht – und das ist nach wie vor NVIDIA mit seinem kompletten AI-Ökosystem. Graphcore hat allerdings ein paar Kunden hinzugewonnen, die sich nun mit den IPU-Systemen beschäftigen. Um NVIDIAs Marktmacht in diesem Bereich zu brechen, bedarf es aber noch zahlreicher Anstrengungen und viel Durchhaltevermögen.