Werbung

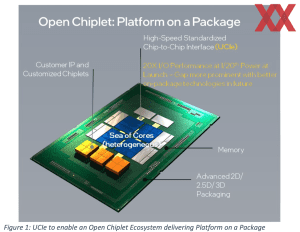

Einige der großen Halbleiterhersteller haben heute angekündigt, einen neuen, offenen Standard für Chiplet-Interconnects ins Leben rufen zu wollen. Universal Chiplet Interconnect Express oder kurz UCIe tritt dabei in gewisser Weise in die Fußstapfen von PCI-Express, bzw. orientiert sich in der grundsätzlichen Herangehensweise daran.

Ziel ist es gewisse Vorgaben zu entwickeln und in den beteiligten Unternehmen umsetzen zu lassen, die es dann theoretisch ermöglichen, dass alle Teilnehmer ihre Chiplets als Teil eines Ökosystems untereinander austauschen können. Dazu muss eine Kompatibilität in den Interconnects gewährleistet sein – nicht auf ebene der Protokolle, wohl aber in der physikalischen Umsetzung.

Eines scheint inzwischen unter allen Herstellern klar zu sein: Künftig sind Chiplets der einzige Weg, die Weiterentwicklung vorantreiben zu können. Monolithische Chips kommen an ihre Grenzen. AMD stellt seine CPUs und inzwischen auch die aktuelle Radeon-Instinct-Generation in einem Chiplet-Verfahren her. Intel wird in diesem Jahr sowohl bei den Prozessoren als auch bei den Beschleuniger-Chips klar diese Richtung einschlagen und auch bei anderen Herstellern ist zumindest längerfristig ein Wechsel zu Chiplets, bzw. Tiles angedacht.

Einen Standard oder eine Spezifikation über mehrere Unternehmen hinweg zu entwickeln, macht natürlich nur dann Sinn, wenn es das Ziel ist, Prozessoren, bzw. Beschleuniger zu entwickeln, die Chips von mindestens zwei unterschiedlichen Herstellern verwenden. Bei Intel hat man schon recht offen über dieses Thema gesprochen und will seine eigenen x86-Kerne in Lizenz anbieten, wenn ein fremdes Design in der IFS-Fertigung hergestellt werden soll. Von anderen Herstellern wurden entsprechende Wünsche zwar schon häufiger geäußert (Microsoft, Meta, usw.), bisher scheiterten solche Pläne jedoch an der fehlenden Offenheit der meisten Hersteller.

Intel ist wenig überraschend einer der Initiatoren von UCIe. Weiterhin beteiligt sind Advanced Semiconductor Engineering (ASE), AMD, Arm, Google, Intel, Meta, Microsoft, Qualcomm, Samsung und Taiwan Semiconductor Manufacturing Company (TSMC). Das Unternehmen wie AMD und Intel in gewisser Form für einen Standard zusammenarbeiten, ist dabei nicht weiter verwunderlich. Dass man dies auch für eine Spezifikation wie UCIe tut, zeigt, wie wichtig dieses Thema den beteiligten Unternehmen zu sein scheint. Auffällig: NVIDIA ist zunächst einmal kein Teil des UCIe-Konsortiums.

UCIe ist Protokoll-agnostisch und macht nur physikalische Vorgaben für die Verbindung der Chips. Es spielt hier also zunächst einmal keine Rolle ob Intels EMIB und Foveros zum Einsatz kommt oder eine SoIC-Technik von TSMC. Es gibt allerdings einige Vorgaben in der Charakteristik der Verbindung. Hier wird in zwei Klassen unterschieden: Standard Packaging und Advanced Packaging:

- Datenrate: 4, 8,12, 16, 24, 32 GT/s

- Bump Pitch: 100 bis 130 bzw. 25 bis 55 µm

- Kanal-Reichweite: <= 25 bzw. <= 2 mm

- Effizienz: 0,5 bzw. 0,25 pJ/Bit

- Latenz: < 2 ns

Es gibt noch einige weitere Vorgaben aus obiger Tabelle. Diese beschreiben die Dichte der Datenrate pro Millimeter Kantenlänge (B/W Shoreline) oder auf die Fläche bezogen (B/W Density). Viele dieser Vorgaben kennen wir als Eckdaten der bereits vorgestellten und verwendeten Interconnect-Technologien.

Dort, wo dies notwendig wird, soll ein Die-to-Die Adapter zum Einsatz kommen. Dieser stellt eine Kompatibilität zwischen der physikalischen und der Protokollebene her.

UCIe 1.0 ist nur ein erster Schritt, der grobe Richtlinien für die weitere Entwicklung vorgibt. Es ist kaum damit zu rechnen, dass es Chips mit UCIe-1.0-konformer Umsetzung geben wird. Es wird noch einige Zeit dauern, bis wir erste Chips sehen, die Chiplets unterschiedlicher Hersteller in dieser Form zum Einsatz bringen werden. Aktuell umschreibt UCIe lediglich Techniken für ein 2D- und 2,5D-Packaging, nicht für ein 3D-Stacking, wie es schon von einigen Herstellern geplant wird. UCIe 1.0 ist jedoch ein Anfang, der nun vor allem weitere Interessenten einsammeln soll. Gegen Ende des Jahres soll es dann weitere Details geben. Bis dahin ist www.uciexpress.org die Anlaufstelle.