Werbung

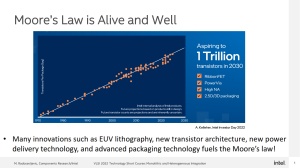

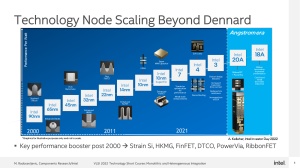

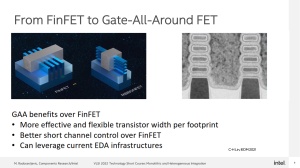

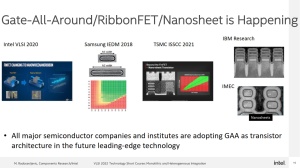

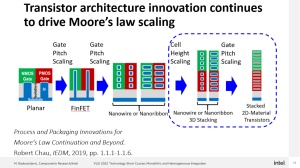

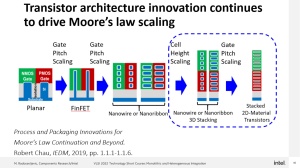

Auf dem VLSI Symposium hat Intel weitere Details zur Nutzung gestapelter und gefalteter Transistoren veröffentlicht. Ab Intel 20A und somit ab etwa 2024/25 steht ein fundamentaler Wechsel in der Art und Weise des Aufbaus der Transistoren an. Alle großen Fertiger arbeiten an GAA-Transistoren (Gate-All-Arround), die in verschiedenen Ausführungen umgesetzt werden und die FinFETs ablösen sollen. Intel nennt sie RibbonFET und tatsächlich gibt es unterschiedliche Ausführungen der gestapelten Transistoren.

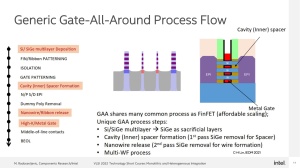

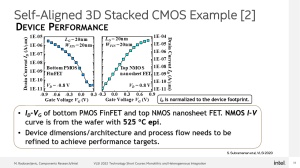

Die erste Generation der GAA-Transistoren wird aus NMOS- und PMOS-Halbleitern bestehen, deren Gates auf allen vier Seiten um dünne Kanäle gewickelt sind. Kommen Bänder zum Einsatz, nennt man sie Nanoribbon, sind es dünne Leiter, heißen sie Nanowire. Diese verbesserte Gate-Steuerung des Kanals überwindet die physikalischen Skalierungs- und Leistungsbeschränkungen von FinFETs und ermöglicht eine weitere Skalierung der Versorgungsspannung.

Ein weiterer Vorteil der GAA-Transistoren ist, dass diese den gleichen Strom schalten können, wie dies sonst mehrere FinFETs tun und das auf einer kleineren Fläche. Über die breite der Gates, die in der Fertigung variabel sind, können die GAA-Transistoren in den Eigenschaften angepasst werden.

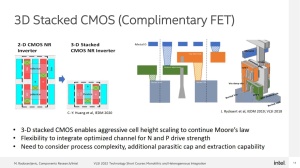

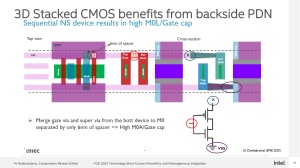

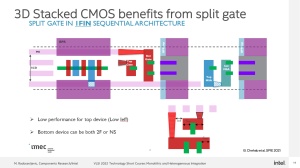

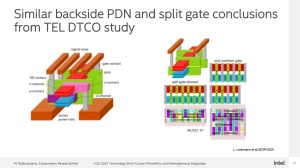

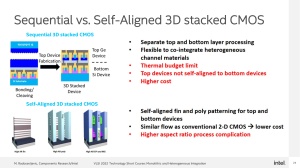

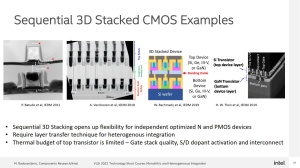

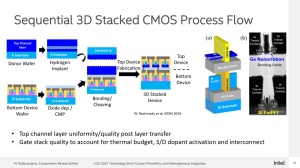

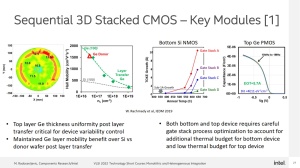

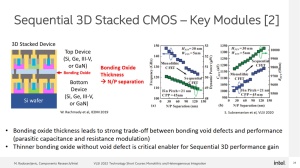

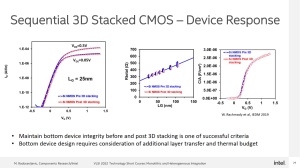

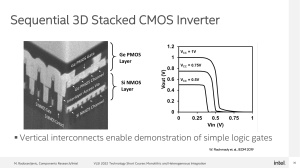

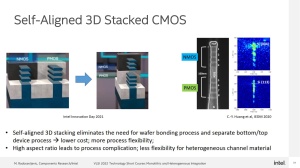

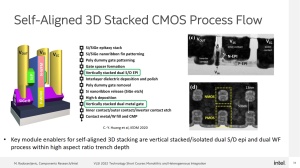

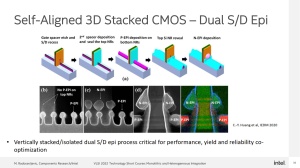

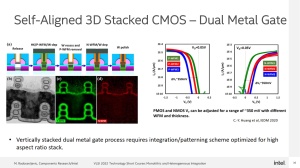

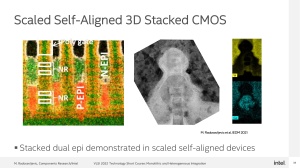

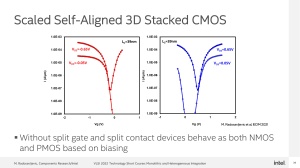

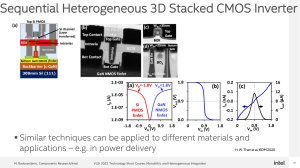

In einem weiteren Schritt will Intel diese NMOS- und PMOS-Bauteile übereinander stapeln. Alleine über diese Maßnahme soll die Fläche auf dem Chip um 30 bis 50 % besser genutzt werden. Intel arbeitet hier gerade an verschiedenen Methoden die NMOS- und PMOS-Halbleiter übereinander zu stapeln. Hier gibt es sequentielle Prozessschritte für Germanium-PMOS-GAA-Transistoren auf Silizium-NMOS-FinFETs oder selbstausrichtende NMOS- und PMOS-GAA-Transistoren mit einem Poly Pitch (Abstand zwischen den Gates) von 55 nm.

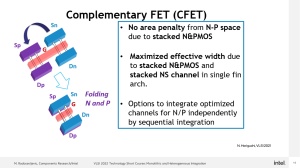

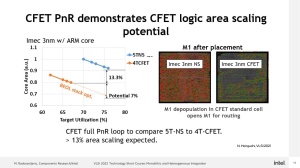

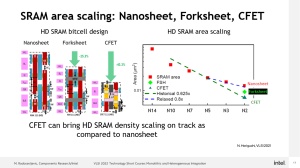

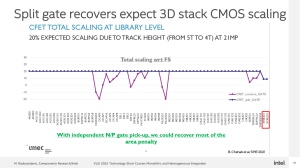

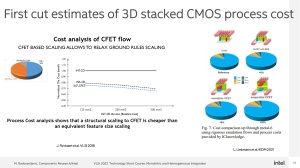

Complementary FETs (CFET) sind gefaltete N&P-MOS-Transistoren, die den Platzbedarf ebenfalls reduzieren sollen, ohne dabei jedoch in der Komplexität an GAA-Transistoren heranreichen zu müssen. Besonders High-Density SRAM-Zellen sollen davon profitieren und eine hohe Packdichte erreichen. Eine HD-Zelle aus Nanosheet-Transistoren ist fast doppelt so groß wie eine vergleichbare Bitzelle, die aus CFETs konstruiert wird.

Während sich die GAA-Transistoren also für die eigentlichen Schaltungen im Logikbereich eignen, sind es die CFETs, die im SRAM-Bereich die weitere Skalierung ermöglichen sollen. Dies ist nur ein Beispiel der Variabilität im Bereich der Fertigung eines Prozessors. Verschiedene Transistor-Typen und Bibliotheken kommen gemeinsam zum Einsatz – für jeden Bereich das optimierter Verfahren.

Gestapelte Transistoren führen aber natürlich auch zusätzliche Prozessschritte ein. Die Komplexität und Kosten in den Griff zu bekommen ist also eine wichtige Vorgabe, damit die Fertigung in dieser Form auch umgesetzt werden kann. Das Component-Research-Team bei Intel arbeitet natürlich schon seit Jahren an der Machbarkeit.

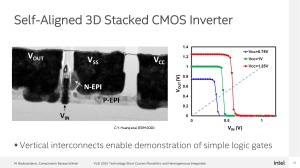

Je nach Art und Weise der Umsetzung eignen sich gestapelte Transistoren aufgrund thermischer Beschränkungen nicht für High-Performance-Bibliotheken. Um Prozessschritte einzusparen sollen Self-Aligned 3D Stacked Multi-Ribbon CMOS Transistoren umgesetzt werden.

Zunächst einmal steht für Intel die Fertigung in Intel 4 und Intel 3 an. Details zu Intel 4 hat der Chipriese ebenfalls auf dem VLSI Symposium veröffentlicht. Allerdings ist Intel 4 nur ein Zwischenschritt zu Intel 3. Für Intel 4 verzichtet der Hersteller auf HD- und I/O-Bibliotheken. Daher eignet sich diese Fertigung auch fast ausschließlich für Chips, die reine Recheneinheiten und kaum Caches enthalten. Für Meteor Lake macht sich Intel genau das zu Nutze, denn Intel 4 wird hier nur für den Compute Tile verwendet. Intel 3 hingegen wird dann auch für komplette Chips optimiert werden.