News und Artikel durchsuchen

{{#data.error.root_cause}}

{{/data.error}}

{{^data.error}}

{{#texts.summary}}

[{{{type}}}] {{{reason}}}

{{/data.error.root_cause}}{{texts.summary}} {{#options.result.rssIcon}} RSS {{/options.result.rssIcon}}

{{/texts.summary}} {{#data.hits.hits}}

{{#_source.featured}}

FEATURED

{{/_source.featured}}

{{#_source.showImage}}

{{#_source.image}}

{{/_source.image}}

{{/_source.showImage}}

{{/data.hits.hits}}

{{{_source.title}}} {{#_source.showPrice}} {{{_source.displayPrice}}} {{/_source.showPrice}}

{{#_source.showLink}} {{/_source.showLink}} {{#_source.showDate}}{{{_source.displayDate}}}

{{/_source.showDate}}{{{_source.description}}}

{{#_source.additionalInfo}}{{#_source.additionalFields}} {{#title}} {{{label}}}: {{{title}}} {{/title}} {{/_source.additionalFields}}

{{/_source.additionalInfo}}

GAA

-

Samsung Foundry: SF2Z kommt mit BSPDN, SF3 mit GAA startet dieses Jahr und SF4U für hohe Volumina

Auf dem Samsung Foundry Forum hat der südkoreanische Großkonzern und Chiphersteller einige Details zu seinen Plänen hinsichtlich der Fertigung in den kommenden Jahren verkündet. Unter anderem wurden zwei neue Prozess-Nodes SF2Z und SF4U angekündigt. Mit SF2Z wird Samsung auf ein Backside Power Delivery Network (BSPDN) setzen. Bei Intel wird man diesen Schritt mit Intel 20A gehen und TSMC hat seine Pläne für eine BSPDN-Technik auf die... [mehr]

Auf dem Samsung Foundry Forum hat der südkoreanische Großkonzern und Chiphersteller einige Details zu seinen Plänen hinsichtlich der Fertigung in den kommenden Jahren verkündet. Unter anderem wurden zwei neue Prozess-Nodes SF2Z und SF4U angekündigt. Mit SF2Z wird Samsung auf ein Backside Power Delivery Network (BSPDN) setzen. Bei Intel wird man diesen Schritt mit Intel 20A gehen und TSMC hat seine Pläne für eine BSPDN-Technik auf die... [mehr] -

2 nm und GAA: Samsung legt los, TSMC trennt BPD von N2-Fertigung (Update)

Auf dem Technology Symposium 2022 sprach TSMC über seine Pläne hinsichtlich der kommenden Fertigungsschritte. Während der Fokus in den kommenden Jahren auf auf Fertigung in diversen N3-Varianten liegen wird, steht mit N2 der Wechsel von den FinFETs auf GAA-Transistoren an. Mit N2 wird TSMC aber noch nicht direkt auf die Backside Power Delivery (BPD), sprich die Strom- und Spannungsversorgung durch die Rückseite des Wafers, umsteigen... [mehr].

Auf dem Technology Symposium 2022 sprach TSMC über seine Pläne hinsichtlich der kommenden Fertigungsschritte. Während der Fokus in den kommenden Jahren auf auf Fertigung in diversen N3-Varianten liegen wird, steht mit N2 der Wechsel von den FinFETs auf GAA-Transistoren an. Mit N2 wird TSMC aber noch nicht direkt auf die Backside Power Delivery (BPD), sprich die Strom- und Spannungsversorgung durch die Rückseite des Wafers, umsteigen... [mehr]. -

GAA, CFET: Wie Intel Moores Law mit gestapelten Transistoren fortsetzen will

Auf dem VLSI Symposium hat Intel weitere Details zur Nutzung gestapelter und gefalteter Transistoren veröffentlicht. Ab Intel 20A und somit ab etwa 2024/25 steht ein fundamentaler Wechsel in der Art und Weise des Aufbaus der Transistoren an. Alle großen Fertiger arbeiten an GAA-Transistoren (Gate-All-Arround), die in verschiedenen Ausführungen umgesetzt werden und die FinFETs ablösen sollen. Intel nennt sie RibbonFET und tatsächlich... [mehr]

Auf dem VLSI Symposium hat Intel weitere Details zur Nutzung gestapelter und gefalteter Transistoren veröffentlicht. Ab Intel 20A und somit ab etwa 2024/25 steht ein fundamentaler Wechsel in der Art und Weise des Aufbaus der Transistoren an. Alle großen Fertiger arbeiten an GAA-Transistoren (Gate-All-Arround), die in verschiedenen Ausführungen umgesetzt werden und die FinFETs ablösen sollen. Intel nennt sie RibbonFET und tatsächlich... [mehr] -

Samsung will ab 2025 in 2 nm produzieren

Auf dem Samsung Foundry Forum hat der koreanische Großkonzern über seine Pläne hinsichtlich der Fertigung gesprochen. Dabei greift Samsung gar nicht so weit vor und will schon ab Ende 2022 mit der Fertigung in 3GAE (3 nm Gate All Around Early) beginnen – so wie man dies auch zuletzt bereits bekräftigte. Für eine Fertigung besonders wichtig ist dabei die Ausbeute. Nach aktuellem Stand soll 3GAE auf Niveau der Fertigung in 4 nm zum... [mehr]

Auf dem Samsung Foundry Forum hat der koreanische Großkonzern über seine Pläne hinsichtlich der Fertigung gesprochen. Dabei greift Samsung gar nicht so weit vor und will schon ab Ende 2022 mit der Fertigung in 3GAE (3 nm Gate All Around Early) beginnen – so wie man dies auch zuletzt bereits bekräftigte. Für eine Fertigung besonders wichtig ist dabei die Ausbeute. Nach aktuellem Stand soll 3GAE auf Niveau der Fertigung in 4 nm zum... [mehr] -

Aus 10 werden 7 nm: Intel benennt Fertigungsgrößen neu und gibt Vorschau auf die nächsten Jahre

Im Rahmen eines "Intel Accelerated" getauften Webcasts hat Intel am Abend über seine Pläne bei den Prozess- und Packaging-Roadmaps gesprochen. CEO Pat Gelsinger und Dr. Ann Kelleher, SVP und GM des Technology Development, haben noch einmal die grundsätzliche Neuausrichtung der IDM-2.0-Strategie aufgezeigt. Demnach wird Intel einerseits weiterhin (und eventuell auch im größeren Maßstab) die externe Fertigung von TSMC,... [mehr]

Im Rahmen eines "Intel Accelerated" getauften Webcasts hat Intel am Abend über seine Pläne bei den Prozess- und Packaging-Roadmaps gesprochen. CEO Pat Gelsinger und Dr. Ann Kelleher, SVP und GM des Technology Development, haben noch einmal die grundsätzliche Neuausrichtung der IDM-2.0-Strategie aufgezeigt. Demnach wird Intel einerseits weiterhin (und eventuell auch im größeren Maßstab) die externe Fertigung von TSMC,... [mehr] -

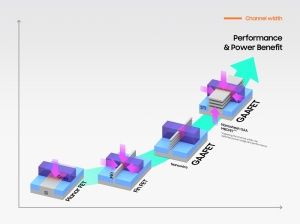

Ab 2022 in 3 nm: Samsungs Multi Bridge Channel FET als Zukunft der Halbleitertechnik

Samsung stellt mit den Multi Bridge Channel FETs (MBCFET) die nächste Generation der Feldeffekttransistoren (FET) vor. Diese sollen alle aktuellen physikalischen und elektrischen Schranken umgehen können und ab 2022 bei Samsung in der Massenfertigung in 3 nm zum Einsatz kommen. Bereits 2021 soll es aber erste Samples geben. Bereits Anfang 2019 sprach Samsung erstmals über das Thema, fügt diesem nun aber weitere Details hinzu. Durch den... [mehr]

Samsung stellt mit den Multi Bridge Channel FETs (MBCFET) die nächste Generation der Feldeffekttransistoren (FET) vor. Diese sollen alle aktuellen physikalischen und elektrischen Schranken umgehen können und ab 2022 bei Samsung in der Massenfertigung in 3 nm zum Einsatz kommen. Bereits 2021 soll es aber erste Samples geben. Bereits Anfang 2019 sprach Samsung erstmals über das Thema, fügt diesem nun aber weitere Details hinzu. Durch den... [mehr] -

Samsung spricht über Fertigung in 3 nm mit GAA-Transistoren

Samsung hält gerade das 3. US Samsung Foundry Forum ab und präsentiert dabei die Neuheiten und Pläne rund um die Halbleiterfertigung. Nicht ganz zufällig dürften darin auch GAA-Transistoren genannt werden, zu denen wir eine Meldung zum Einsatz als Nanowires für Transistoren in 5 nm und kleiner hatten. Samsung hat derzeit folgende Pläne für die Fertigung: 7LPP (7nm Low Power Plus), 5LPE (5nm Low Power Early), 4LPE/LPP (4nm Low... [mehr]

Samsung hält gerade das 3. US Samsung Foundry Forum ab und präsentiert dabei die Neuheiten und Pläne rund um die Halbleiterfertigung. Nicht ganz zufällig dürften darin auch GAA-Transistoren genannt werden, zu denen wir eine Meldung zum Einsatz als Nanowires für Transistoren in 5 nm und kleiner hatten. Samsung hat derzeit folgende Pläne für die Fertigung: 7LPP (7nm Low Power Plus), 5LPE (5nm Low Power Early), 4LPE/LPP (4nm Low... [mehr]