Werbung

In einem eher ungewöhnlichen Schritt gibt das 2023 Symposium on VLSI Technology & Circuits eine Vorschau auf einige der Beiträge, die vom 11. bis 16. Juni in Kyoto (Japan) präsentiert werden sollen.

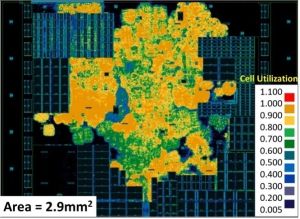

Unter anderem wird Intel in einem seiner Vorträge die Umsetzung eines Efficiency-Kerns aus der Intel-4-Fertigung mit Backside Power Delivery (BPD) vorstellen. Die Fertigung in Intel 4 wird unter anderem für das Compute-Tile von Meteor Lake verwendet werden. BPD oder wie Intel es nennt, PowerVia, ist neben den GAA-Transistoren ein zweiter wichtiger Faktor, der in den kommenden Jahren zu einer Weiterentwicklung in der Halbleiterfertigung führen soll.

PowerVia stellt eine neue Methode in der Stromversorgung eines Chips dar. Bisher werden die Leiterbahnen und Kanäle im Silizium von der gleichen Seite ausgeführt – sowohl für die eigentlichen Logikelemente, spricht die Transistoren, wie auch für die Spannungsversorgung dieser. Dies kann aber zu Problemen führen, da es zu Interferenzen zwischen mehreren, stromführenden Elementen und den Logikbauteilen bzw. den Metallschichten für die Kommunikation mit den Transistoren kommen.

Die Komplexität innerhalb eines Chips mit mehreren Milliarden Transistoren und mehr als einem Dutzend an Metallebenen ist ohnehin schon nicht unerheblich. Mit PowerVia wird nun die Rückseite des Wafers verwendet. Während auf der einen Seite weiterhin die Logikelemente und Interconnects belichtet werden, soll die Stromversorgung nun von der anderen Seite erfolgen. Die für PowerVia verwendeten TSVs sollen 500mal kleiner sein, als das was heutzutage für die TSVs im Packaging möglich ist.

Samsung spricht über SF3 (3 nm)

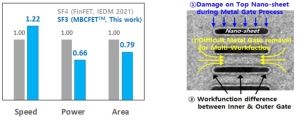

Nachdem Samsung mit der Fertigung in 4 nm (SF4) bisher keine großen Erfolge feiern und Kunden an Land ziehen konnte, soll SF3 den Konzern wieder auf die Erfolgsspur führen. Im Vortrag werden offenbar die Unterschiede zu SF3 sowie der Aufbau der bei Samsung als Multi Bridge Channel FETs (MBCFET) bezeichneten GAA-Transistoren eine Rolle spielen.

Im PPA-Vergleich (Performance/Power/Area) bietet SF3 ein Plus von 22 % in der Leistung (bei gleicher Leistungsaufnahme) oder bei gleicher Leistung eine um den Faktor 0,66 reduzierte Leistungsaufnahme. Der Platzbedarf für ein bestimmtes Design sinkt um den Faktor 0,79 im Vergleich zu SF4.

Ein Querschnitt durch einen GAA-Transistor zeigt dessen Aufbau, den wir in dieser Form bereits häufiger gesehen haben. Samsung deutet in seinem Vortrag aber wohl auf die Herausforderungen und Probleme hin, wie etwa Beschädigungen, die im Verlaufe des Prozesses vorkommen können. Die dazugehörigen Prozess-Optimierungen sind die Herausforderungen vor denen Samsung offenbar noch steht.

Das VLSI-Symposium bzw. einige der Vorträge werden wir auswerten, sobald diese stattgefunden und die dazugehörigen PDF vorliegen. Die Vorschau zeigt allerdings bereits einige Interessante Themen.