Werbung

Mit fünf Fertigungs-Schritten in vier Jahren will Intel wieder auf die Erfolgsspur. Die aktuell erhältlichen Desktop- und Server-Chips fertigt man in Intel 7, mit Meteor Lake und Granite Rapids soll dann Intel 4 übernehmen, aber man ist für so manches Chiplet-Design auch noch auf externe Fertigungspartner angewiesen – allen voran TSMC. Da die Intel Foundry Services ab Mitte des Jahrzehnts eine zunehmend wichtige Rolle einnehmen sollen und dies mit den eigenen Bedürfnissen nach einer High-End-Fertigung zusammentrifft, laufen in Intels Entwicklungsabteilung aktuell zahlreiche Projekte, um den Chipriesen in dieser Hinsicht wieder auf die Spitze zu bringen.

Einer der Bausteine dabei ist PowerVia – Intels Name für eine rückseitige Versorgung des Chips. Die Signalwege sowie Strom- und Spannungsversorgung sollen räumlich voneinander getrennt werden, was zahlreiche Vorteile nach sich zieht. Zusammen mit den RibbonFETs soll PowerVia ab 2024 in der Fertigung der ersten Chips in Intel 20A und Intel 18A zum Einsatz kommen. Auf dem VLSI-Symposium hat Intel über die Entwicklung von PowerVia für Intel 4 gesprochen

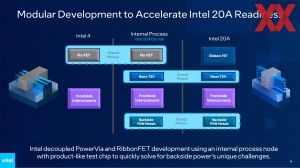

Seit der Ankündigung der Erweiterung der Fertigungskapazitäten in Oregon (D1X Mod 3) ist klar: PowerVia und RibbonFET werden ab Intel 20A zum Einsatz kommen. Bis dahin fährt Intel mit Intel 4 und Intel 3 in der aktuellen Form fort. Es gibt einen internen Test-Prozess, den Intel bisher nicht wirklich definierte, der aber nicht für konkrete Produkte zum Einsatz kommen sollte.

Mit dem VLSI-Komposium bzw. der Präsentation dort ist klar: Intel baut diesen internen Prozess zur Risikominimierung auf Intel 20A auf.

Nicht jede rückseitige Versorgung ist gleich

Aber zunächst einmal wollen wir erläutern, warum nicht nur Intel an dieser Technik arbeitet, die allgemein als Backside Power Delivery Network (BS-PDN) bezeichnet wird.

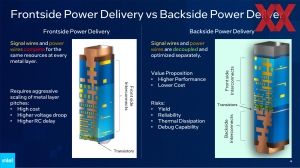

Die aktuelle Prozess-Technik sieht die Daten- und Power-Leitungen von einer Seite vor. Das Front-End besitzt die Interconnects und Lagen im Chip. Bis zu 14 dieser Lagen kommen inzwischen zum Einsatz und die Materialforschung muss immer größere Anstrengungen unternehmen, damit die Versorgung und Signalintegrität weiterhin gewährleistet werden kann. Hohe Kosten und dennoch vorhandene technische Limitierungen durch einen starken Spannungs-Abfall sowie durch Interferenzen sind die Folge.

Durch eine rückseitige Versorgung werden die Signal- und Versorgungsleitungen voneinander getrennt. Das Front-End besitzt weiterhin die Daten-Interconnects, über die Rückseite kommen die Vias und Layer für die Versorgung. Potentiell eine höhere Leistung und geringere Kosten sind die Vorteile der neuen Technik. Aber es gibt auch Nachteile und diese liegen in der großen Umstellung der Fertigung, was wiederum die Ausbeute verringert oder Auswirkungen auf die Zuverlässigkeit, die Abführung der Abwärme und mehr hat. All diese Punkte will Intel über den internen Test-Prozess auf Basis von Intel 4 und Intel 20A prüfen und Lösungen finden.

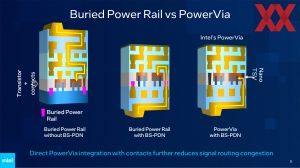

In der Umsetzung eines BS-PDN gibt es aber ebenfalls einige Unterscheidungen, die man machen muss. Oftmals ist hier einfach nur von Buried Power Rails die Rede. Bei diesen befinden sich einige spannungsversorgende Leiterbahnen zwar auf der Rückseite der Transistoren, die Zuführung der Power Rails findet aber weiterhin über das Front-End statt. Die Nachteile, dass sich diese Versorgung auch den Bereich der Datenleitungen teilt, sind also weiterhin vorhanden.

Buried Power Rails mit einem BS-PDN sind der nächste Schritt und hier findet die Versorgung dann tatsächlich über die Rückseite statt, was die Daten- und Versorgungsbereiche weitestgehend trennt. Aber für die unterste Ebene (M0) wird weiterhin das Front-End verwendet.

Für die PowerVia-Technologie setzt Intel Nano-TSVs ein, die direkt mit den Transistoren verbunden werden.

Intel will das Risiko in der Fertigung entkoppeln. In Module aufgeteilt, sollen einzelne Schritte gemacht, die dann zusammengeführt werden. So wird man für den internen Risiko-Prozess in 20A zunächst die FinFETs beibehalten, die PowerVia-Technologie in Form der Nano-TSVs und BS-PDN aber umsetzen und testen. Parallel dazu läuft die Entwicklung der RibbonFETs, die dann in Intel 20A zusammenkommen – mit den dann fertig entwickelten Technologien rund um PowerVia.

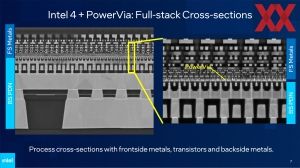

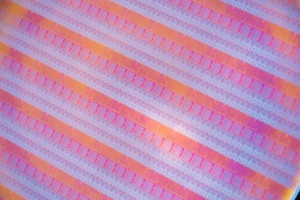

In einem Schnitt durch einen in Intel 4 hergestellten Test-Chip sieht man die Front-Side Metalllagen und die das BS-PDN. Die großen Lagen und Durchführungen des PS-PDN ermöglichen eine gute und effektive Spannungsversorung, während die Front-Side-Metalllagen relativ einfach gestaltet und extrem eng zusammengeführt werden können. Die mit gelber Beschriftung markierten weißen Säulen sind die Nano-TSVs.

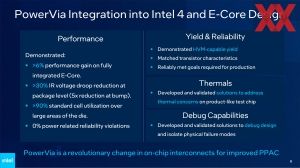

Als Test-Vehicle hat Intel einen Efficiency-Kern in Intel 4 mit PowerVia gefertigt und vergleicht diesen mit einem E-Core in Intel 4 ohne die neue Versorgung. Es handelt sich dabei um das E-Kern-Design welches für Meteor Lake vorgesehen ist. Die Leistung des E-Kerns konnte um 6 % gesteigert werden. Der Spannungsabfall liegt bei nur noch 30 % und dennoch kann Intel auf mehr als 90 % der Fläche auf Standard-Cell-Bibliotheken für seine Transistoren zurückgreifen.

Einige Eckdaten zum Testchip:

- 22 Millionen Transistoren für die Abbildung eines E-Kerns

- jeweils ein E-Kern pro Quadrant

- jeder E-Kern hat eine Fläche von 2,9 mm²

- zweitgeteilter Chip mit 40 % an Design of Experiment (DOE)

- ein solcher Chip hat eine Fläche von 4 x 8,3 = 33,2 mm²

- Takt von 3 GHz

- Betriebsspannung von 1,1 V

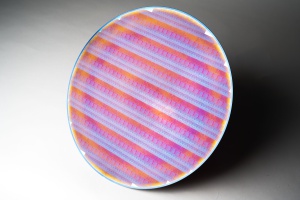

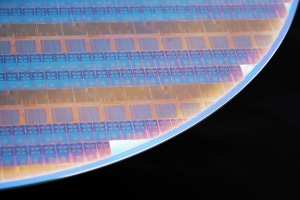

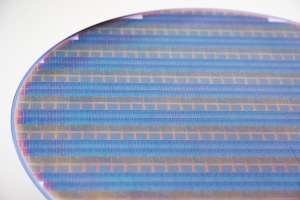

Auf der anderen Seite bestätigt Intel, dass die Fertigung in Intel 4 mit PowerVia bereits eine Ausbeute hat, die eine Massenproduktion zulässt. Dazu gehört auch, dass in der Fertigung keinerlei besondere Probleme aufgetreten sind und das obwohl man den Wafer soweit herunterschleift, dass nur noch die Transistorebene übrig bleibt.

Hinsichtlich der Kühlung dient die bisher ungenutzte Seite des Chips auch der Kühlung. Die Hersteller wie AMD und Intel legen eine gewisse Dicke des Chips fest, der nicht zu dünn werden darf, denn die Abgabe der Wärme findet in alle Richtungen statt. Warum es hier eine ideale Dicke gibt, dazu hatten wir Anfang des Jahres einen Mitteilung. Das Hinzufügen des BS-PDN sorgt aber dafür, dass die Wärmeabfuhr weiterhin gewährleistet ist. Für das Debugging ist die Rückseite des Chips im Rahmen der Entwicklung aber ebenfalls wichtig und so musste Intel nun Wege finden, wie man auf eventuelle Fehler im Design nun reagieren kann. Auch dazu hatten wir einen Artikel, der unseren Besuch bei Intel in Israel beschreibt und einen Einblick in die Debug & Developement Labs gibt. Aber auch hier hat Intel Mittel und Wege gefunden weiterhin im Debugging die notwendigen Maßnahmen durchführen zu können.

Soweit sieht alles gut aus

Die Analysen zur Fertigung in Intel 4 mit PowerVia sehen also so weit gut aus. Ergebnisse dazu präsentiert Intel auf dem VLSI Symposium.

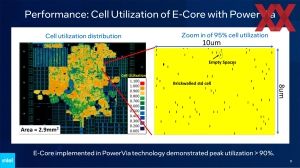

Das Schaubild zeigt die Nutzung Standard-Zellbibliotheken für den E-Kern. Für große Bereiche kommt man hier auf 80 bis 90 %, in manchen aber auch auf deutlich weniger, was aber nicht unüblich ist. Die Zell-Nutzung sieht in jedem Kern-Design in etwa so aus, je dichter man die Bereiche aber vollgepackt bekommt, desto besser. Bei den vielen dunklen Bereichen könnte es sich beispielsweise um Caches handeln, die sich auch in den aktuellsten Prozessoren kaum mehr dichter packen lassen.

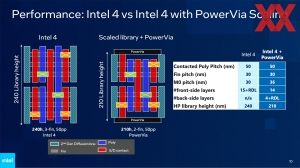

Die Zell-Bibliothek für Intel 4 sieht ein 3+3-Design vor: Drei Fins oben, drei Fins unten und ist insgesamt 240 nm hoch. Für Intel 4 + PowerVia wurde eine 2+2-Design verwendet. Die PowerVia-Kontakten befinden sich jeweils oben und unten an den Zellen, die insgesamt auf eine Höhe von 210 nm kommen. Durch das schlankere Design kann Intel die Zell-Bibliothek also kleiner ausführen und erreicht dennoch eine höhere Leistung.

Der Vergleich für einige Größen in den Metalllagen zeigt, dass Intel für die unterste M0-Lage die Abstände von 30 auf 36 nm entspannen kann. Bei den Front-End-Lagen kann Intel ebenfalls zurückfahren, fügt aber durch das BS-PDN an der Rückseitige einige hinzu. Der zusätzliche Aufwand und die Kosten will man aber durch das wesentlich entspanntere M0-Layer-Design bereits kompensieren können.

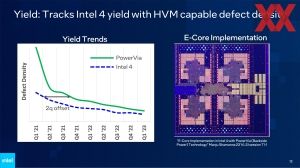

Im Vergleich zu Intel 4 liegt Intel bei Intel 4 mit PowerVia zwei Quartale vor dem Prozess, der aktuell für Meteor Lake nun verwendet wird. Dies soll zeigen, dass die Integration von PowerVia keinerlei Stolperstein sein muss und offenkundig auch nicht ist. Natürlich gibt Intel hier auf der Y-Achse keinerlei Einheiten an, so dass wir die Defekt-Dichte nur im Verhältnis zueinander kennen. Aber Intel sieht PowerVia bereit für die Massenproduktion.

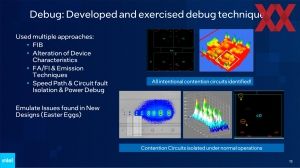

Vier E-Kerne hat Intel im Testchip umgesetzt. Jeder davon hat andere Charakteristiken erhalten und es wurden absichtlich Fehler eingebaut, damit die Debugg-Möglichkeiten getestet werden konnten.

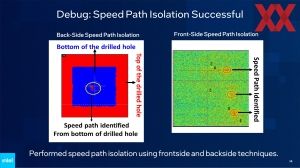

Die Fehler konnten detektiert und analysiert werden. Auch physische Maßnahmen im Debugging, wie das Bohren von Löchern mittels Focused Ion Beam (FIB) ist von beiden Seiten möglich und somit sieht Intel auch hier keinerlei Hindernisse PowerVia nicht einzusetzen.

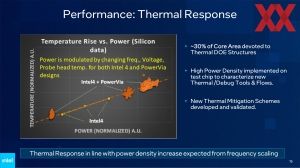

Auch im Hinblick auf die Kühlung sieht Intel keinerlei Hindernisse, denn durch das Hinzufügen der PowerVia-Technologie bewegt sich das Temperaturverhalten in Abhängigkeit der Leistungsaufnahme nicht außerhalb des erwarteten Bereichs. Um dies zu testen hat man etwa 30 % der Chipfläche des Testchips mit Strukturen entworfen, die einfach nur dazu da sind eine möglichst hohe Leistungsaufnahme zu generieren.

Die Komplexität verschiebt sich

Weniger aufwändige M0-Metalllagen an den Transistoren und dafür aber vier Lagen für die Umsetzung des PowerVia-Leiterbahnen – so lautet der Kompromiss, den Intel hier eingeht. Laut Intel aber ist der Aufwand für das Design der M0-Lage aktuell so komplex, dass man spielend deutlich weniger komplexe Lagen in der Rückseite unterbringen kann.

Dies macht es den EDA-Werkzeugen (Electronic Design Automation) auch einfacher ein Design für die bis zu 14 Font-Side-Lagen zu entwerfen.

Das Handling der Wafer im Reinraum ändert sich natürlich. Zunächst wird der Chip mit seinen Metalllagen wie aktuell auch von der Vorderseite des Wafers belichtet. Die deutlich weniger komplexe M0-Metalllage soll laut Intel auch hier eine Vereinfachung des Prozesses bedeuten.

Danach wird ein Carrier-Wafer aufgebracht, die beiden Wafer werden herumgedreht und die Rückseite des schon belichteten Wafers wird bis an die Transistorebene heruntergeschliffen. Dann wird hier mit dem Aufbau der Nano-TSVs und der Metalllagen für die Versorgung begonnen.

PowerVia ist für 2024 fertig

Intel ist zuversichtlich und sollte es zum aktuellen Zeitpunkt auch sein, dass PowerVia ab 2024 für Intel 20A bereitsteht. Neben den Prozessoren sieht Intel auch bei den GPU- und AI-Beschleunigern den Bedarf nach einer verbesserten Fertigung, die eine höhere Leistung und mehr Effizienz hervorbringt.

Zusammen mit der Entwicklung der RibbonFETs will Intel wieder an die Spitze der Halbleiterentwicklung. Mit all dem Wissen was man aktuell von der Entwicklung der Konkurrenz hat, sieht sich Intel einen Schritt vor dieser – mit Einführung von Intel 20A in 2024. Davon will man als Unternehmen in den eigenen Produkten profitieren, bietet seine Expertise und die Fertigung aber auch externen Kunden an.