Werbung

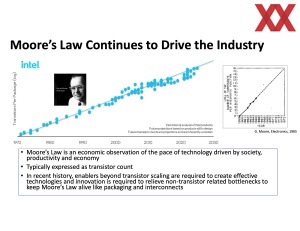

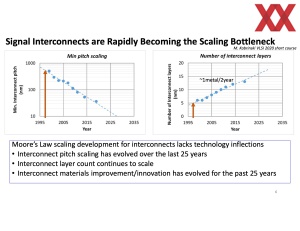

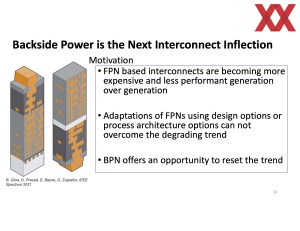

Auf dem 2023 IEEE International Electron Devices Meeting (IEDM 2023) präsentieren Halbleiterunternehmen, Forschungsgruppen und Universitäten ihre aktuellen Forschungsergebnisse rund um die aktuelle Halbleiterentwicklung. In diesem Jahr konzentrieren sich Präsentatoren vor allem auf die Entwicklung von Technologien im Bereich der Backside Power Delivery Networks (BSPDN), des Packagings und der Skalierung der Transistoren auf 2 nm und weniger. In diesem Bericht wollen wir uns auf die Entwicklungen der BSPDN konzentrieren.

Das was Unternehmen wie Intel, TSMC, Samsung oder Forschungsunternehmen wie imec auf dem IEDM 2023 präsentieren ist ein Fenster zu dem, was wir in den kommenden Jahren oder gar Jahrzehnten im Halbleiterbereich sehen werden. Im Falle von Intel werden die Forschungsergebnisse von der Components Research (CR) Group präsentiert. Diese wiederum bietet die entsprechenden Technologien der Entwicklungsgruppe in der Fertigung oder dem Packaging an. Wann, in welche Form oder zu welchem Produkt die Technologien dann eingesetzt werden, steht auf einem ganz anderen Blatt.

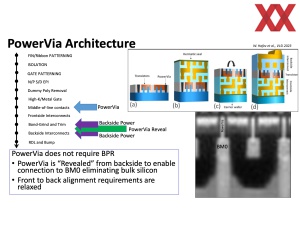

Aber natürlich gibt es hin und wieder eine direkte Verbindung zwischen den präsentierten Technologien und einer konkreten Roadmap. Im Falle von PowerVia werden wir die rückseitige Spannungsversorgung des Chips in den ersten Prozessoren sehen, die in Intel 20A gefertigt werden. Zu den Vorteilen von PowerVia hatten wir bereits zahlreiche Berichte, die auf die Vorteile der Trennung der Spannungs- und Signalversorgung eingehen. So zum Beispiel zu diesjährigen VLSI und auch mit ersten konkreten Ergebnissen auf Basis einer Testfertigung in Intel 4.

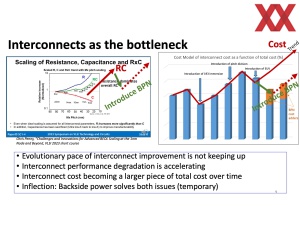

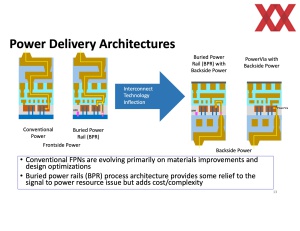

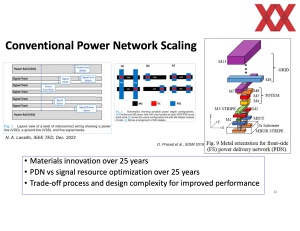

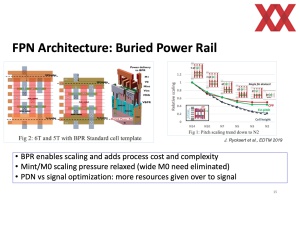

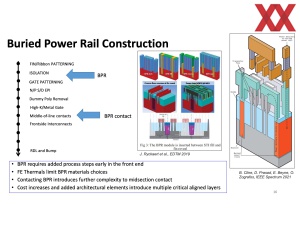

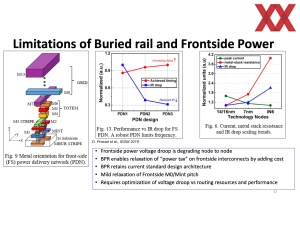

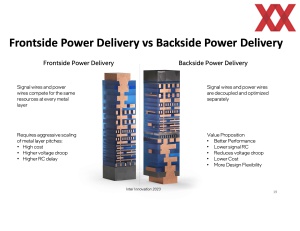

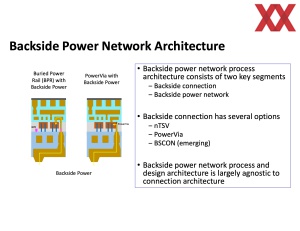

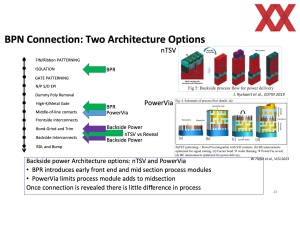

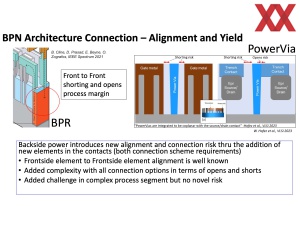

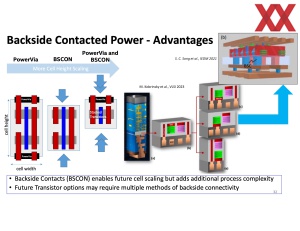

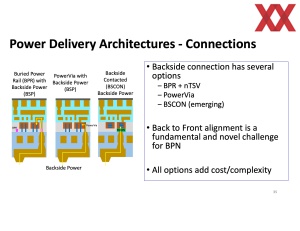

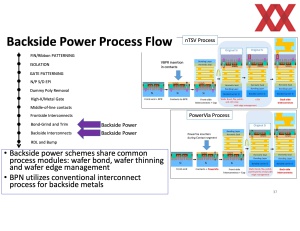

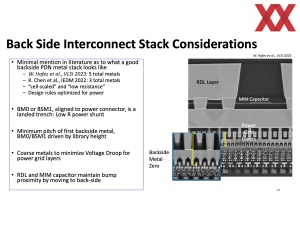

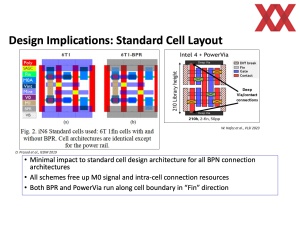

Intels PowerVia-Technologie ist aber nur eine von vielen Formen eines Backside Power Delivery Networks. Die PowerVias führen die Spannungsversorgung von der Rückseite des Chips direkt an die Transistorzelle. Eine weitere Umsetzung erfolgt mittels Buried Power Rails (BPR), die horizontal in den Chips integriert werden und dann die Transistorzellen versorgen. Die Umsetzung von BPR kann aber auch über eine vorderseitige Spannungsversorgung (Frontside Power Delivery) erfolgen.

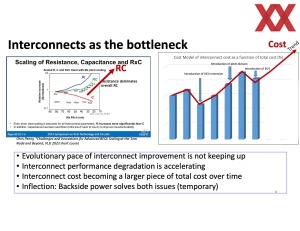

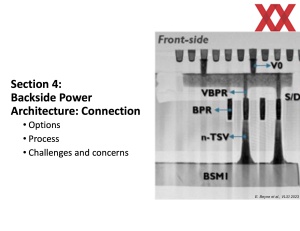

Für die nächsten Schritte in der Prozesstechnik und die immer feineren Strukturen muss Intel aber über die PowerVias hinausgehen. Dazu hat man die Back-Side Contacts (BSCON) entwickelt. BSCON wird dann zum Einsatz kommen, wenn die Transistorzellen gestapelt werden, was der nächste Schritt in der Transistortechnologien sein wird. Bei Intel arbeitet man an dieser Stelle an den RibbonFET, die anderweitig auch als Nanosheet-Transistor bezeichnet werden. In einer ersten Generation wird man diese RibbonFET nebeneinander platzieren, in einem weiteren Schritt aber auch stapeln und dann weiter skalieren wollen. Entsprechend muss eine Methode entwickelt werden, wie man diese Transistorzellen mit der notwendigen Spannung versorgt. Hier kommen dann die Back-Side Contacts ins Spiel.

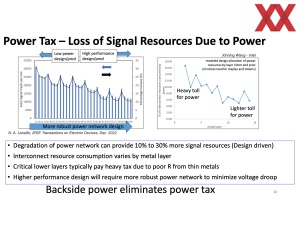

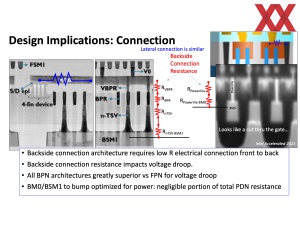

Die BSCON bieten aufgrund der geringeren Länge aus den Power Distribution Layers hinaus eine geringere Kapazität, was die Transistoren schneller schalten und damit einen höheren Takt erreichen lässt. Auf der anderen Seite muss eine stabile Spannungsversorgung erreicht werden, weswegen in die Entwicklung der PowerVias und Back-Side Contacts viel Forschungsarbeit in dieses Segment einfließt.

Die noch nicht eingeführten PowerVias sollen dann für zukünftige Prozessschritte wieder weggelassen werden, um in der vertikalen Ebene Platz zu sparen und die Transistordichte zu erhöhen. Dies wird vor allem für die Stacked RibbonFET (NMOS auf PMOS etc.) wichtig werden.

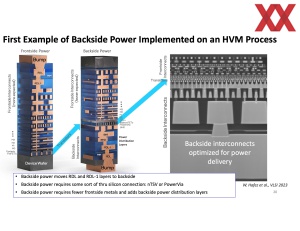

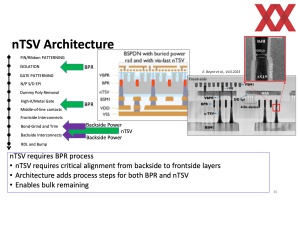

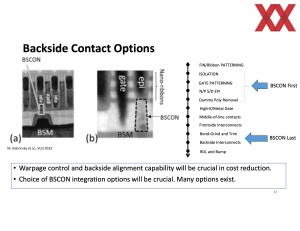

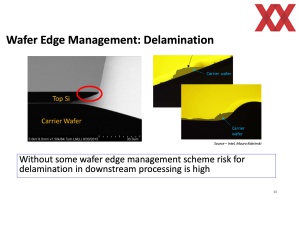

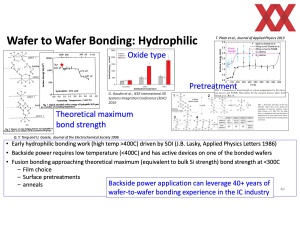

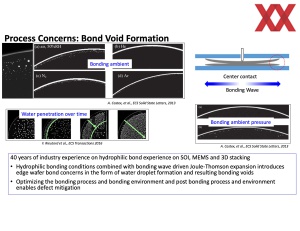

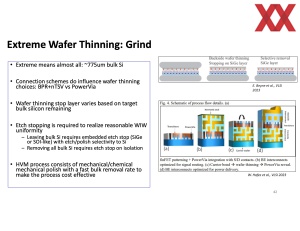

Um die Transistoren von zwei Seiten mit Kontakten zu belegen (von einer Seite das Signaling, von der anderen die Spannungsversorgung), muss der Wafer natürlich anders behandelt werden. Zunächst wird der Chip mit seinen Metalllagen wie aktuell auch von der Vorderseite des Wafers belichtet. Die deutlich weniger komplexe M0-Metalllage soll laut Intel auch hier eine Vereinfachung des Prozesses bedeuten. Danach wird ein Carrier-Wafer aufgebracht, die beiden Wafer werden herumgedreht und die Rückseite des schon belichteten Wafers wird bis an die Transistorebene heruntergeschliffen. Dann wird hier mit dem Aufbau der Nano-TSVs und der Metalllagen für die Versorgung begonnen.

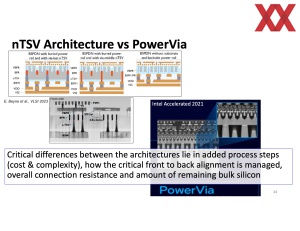

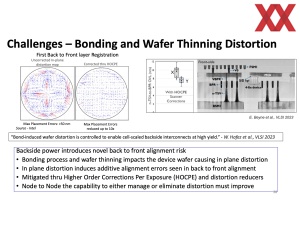

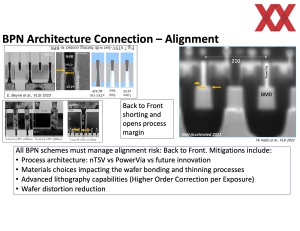

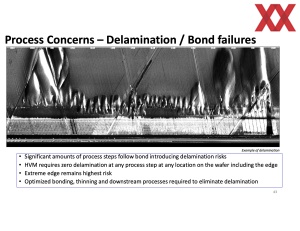

Der Bondprozess und das Herunterschleifen des Wafers wirken sich allerdings auf den Wafer aus und verursachen eine Verzerrung. Diese Verzerrung in der horizontalen Ebene führt zu Ausrichtungsfehlern des BSPDNs. Intel arbeitet aber auch hier an entsprechenden Technologien, um diesen Effekt zu minimieren.

Im Grunde kennt man die Problematik auch aus dem Packaging, wo immer kleinere Kontaktpunkte zueinander finden müssen. Für Foveros Direct soll der Bump Pitch, also der Abstand der Kontakte auf weniger als 10 µm schrumpfen. TSMC setzt dafür seine Packaging-Prozesse wie das ein Hybrid Bonding ein, dessen Bump Pitch schon bei 9 µm liegt. Die für PowerVia verwendeten TSVs sollen 500mal kleiner sein, als das was heutzutage für die TSVs im Packaging möglich ist, was dann auch die Genauigkeit im Bondprozess für ein BSPDN unterstreicht.

Während uns die PowerVias bereits im kommenden Jahr mit den Arrow-Lake-Prozessoren in Intel 20A erwarten werden und dann auch die RibbonFETs verwendet werden, wird es noch etwas dauern, bis wir Technologien wie Back-Side Contacts (BSCON) in konkreten Produkten sehen werden.