Werbung

Meta hat die zweite Generation seines MTIA (Meta Training and Inference Accelerator) präsentiert. Erst Anfang Februar hatte ma verkündet, dass der MTIAv2 in die eigenen Rechenzentren wandert, nun nennt man technische Details. Je nach Datentyp hat Meta die Rechenleistung des MTIA vervierfacht.

Gefertigt wird der neue Chip in 5 nm bei TSMC. Die 2,35 Milliarden Transistoren kommen auf eine Chipfläche von 25,6 x 16,4 mm und somit 421 mm². Das gesamte Package kommt auf 50 x 40 mm. Meta hat die Frequenz von 800 MHz auf 1,35 GHz angehoben, aber auch die TDP steigt von 25 auf 90 W, was man im Hinblick auf die gestiegene Rechenleistung ebenfalls im Blick haben sollte. Die Anbindung an das Host-System findet über acht PCI-Express-5.0-Lanes statt.

Der SRAM wächst von 128 auf 256 MB. Der angebundene LPDDR5 geht von 64 auf 128 GB. Neben des größeren SRAM steigt auch dessen Bandbreite deutlich an. Mehr dazu in der Vergleichstabelle.

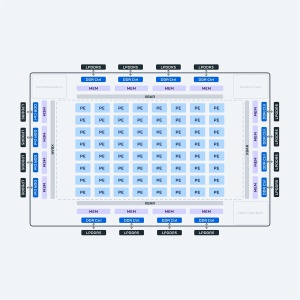

Gerechnet wird in 64 Processing Elements (PEs), die in einem 8x8-Grid angeordnet sind. Miteinander verbunden ist alles über ein Network on Chip (NoC), dessen Durchsatz ebenfalls gesteigert wurde, was zu einer höheren Bandbreite des SRAM zu jedem PE beiträgt.

Meta setzt zwei dieser Chips auf einer PCI-Express-Karte ein. Insgesamt 72 dieser Karten sitzen in einem Rack. Meta hat den Software-Stack für MTIA für PyTorch 2.0 und Funktionen wie TorchDynamo und TorchInductor integriert. Compiler und APIs sind natürlich aufeinander abgestimmt und so kann Meta Soft- und Hardware extrem auf die eigenen Anforderungen hin optimieren.

| MTIAv1 | MTIAv2 | |

| Fertigung | 7 nm (TSMC) | 5 nm (TSMC) |

| Anzahl der Transistoren | 1,12 Milliarden | 2,35 Milliarden |

| Chipgröße | 373 mm² | 421 mm² |

| Frequenz | 0,8 GHz | 1,35 GHz |

| Spannung | 0,67 V | 0,85 V |

| TDP | 25 W | 90 W |

| Host-Interface | PCIe 4.0 x8 | PCIe 5.0 x8 |

| Cache pro PE | 128 kB | 384 Kb |

| SRAM | 128 MB | 256 MB |

| LPDDR5 | 64 GB | 128 GB |

| Cache-Bandbreite | 400 GB/s pro PE | 1 TB/s pro PE |

| SRAM-Bandbreite | 800 GB/s | 2,7 TB/s |

| LPDDR5-Bandbreite | 176 GB/s | 204,8 GB/s |

| GEMM TOPS | 102,4 TFLOPS/s (INT8) 51,2 TFLOPS/s (FP16/BF16) | 708 TFLOPS/s (INT8) (sparsity) 354 TFLOPS/s (INT8) 354 TFLOPS/s (FP16/BF16) (sparsity) 177 TFLOPS/s (FP16/BF16) |

| SIMD TOPS | Vektor: 3,2 TFLOPS/s (INT8) 1,6 TFLOPS/s (FP16/BF16) 0,8 TFLOPS/s (FP32) SIMD: 3,2 TFLOPS/s (INT8/FP16/BF16) 1,6 TFLOPS/s (FP32) | Vektor 11,06 TFLOPS/s (INT8) 5,53 TFLOPS/s (FP16/BF16) 2,76 TFLOPS/s (FP32) SIMD: 5,53 TFLOPS/s (INT8/FP16/BF16) 2,76 TFLOPS/s (FP32) |

Nach MTIAv2 arbeitet Meta natürlich auch weiter an Custom-Silicon. Daneben nutzt man aber auch Hardware anderer Hersteller.

Meta ist einer der größten Kunden für KI-Hardware. Alleine in 2024 will das Unternehmen 350.000 H100-Beschleuniger von NVIDIA kaufen. Insgesamt soll das Volumen an KI-Hardware für 2024 dem Äquivalent von 600.000 H100-GPUs entsprechen. Neben dem Inferencing, beispielsweise in Form einer Ausgabe eines KI-Assistenten, ist das Training ein wichtiger Faktor. Dieses kann von Metas eigener Hardware nicht durchgeführt werden, dazu wird Meta noch immer die Hardware eines anderen Herstellers verwenden müssen.