Werbung

Ähnlich wie im Sommer 2021 zum Telum der ersten Generation hat IBM auf der Hot-Chips-Konferenz in diesem Jahr nun den Telum II vorgestellt. Bei den Prozessoren und den dazugehörigen Systemen von IBM geht es um höchste Verfügbarkeit und möglichst geringe Latenzen. Anwendungsbereiche sind das Finanzwesen, sicherheitsrelevante Anwendungen und solche, die eine extreme Zuverlässigkeit erfordern.

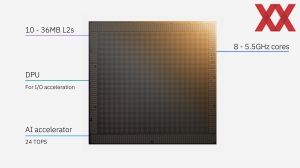

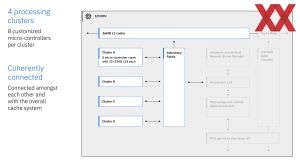

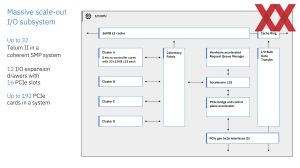

Der Telum II bietet acht Kerne bei einem Takt von 5,5 GHz. Hinzu kommen eine DPU (Data Processing Unit) mit vier Clustern mit jeweils acht Microcontroller-Kernen mit jeweils 64 kB L1-Cache (32 kB Instruction- und 32 kB Data-Cache). Das I/O-Subsystem bietet 192 PCI-Express-5.0-Lanes (5 x 16 Lanes), die in 16 Steckplätzen umgesetzt werden können.

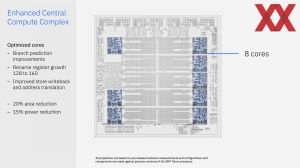

Viele Details zu den acht Kernen gibt es nicht. IBM will den Platzbedarf der Kerne um 20 % reduziert haben. Die Leistungsaufnahme konnte um 15 % reduziert werden.

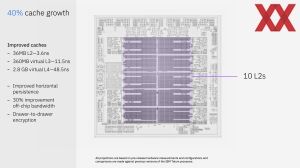

Im Vollausbau bietet der Telum II zehn SRAM-Cluster für jeweils an 36 MB L2-Cache – insgesamt also 360 MB. Die Latenz liegt laut IBM bei 3,6 ns. Einen L3-Cache gibt es auf dem Chip nicht. Aus dem L2-Cache kann ein virtueller L3-Cache erstellt werden, dessen Größe dann ebenfalls 360 MB umfasst. Die Latenzen gibt IBM mit 11,5 ns an. Einen virtuellen L4-Cache gibt es ebenfalls wieder. Dieser kann bis zu 2,8 GB erreichen und hat eine Latenz von 48,5 ns. Im Vergleich zum Telum I steigen die Latenzen leicht an.

| IBM Telum I | IBM Telum II | |

| L2-Cache | 3,8 ns | 3,6 ns |

| virtueller L3-Cache | 12 ns | 11,5 ns |

| virtueller L4-Cache | - | 48,5 ns |

| Chipgröße | 530 mm² | 600 mm² |

| Anzahl der Transistoren | 22,5 Milliarden | 43 Milliarden |

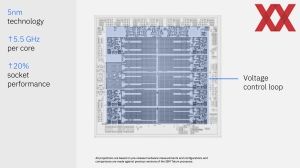

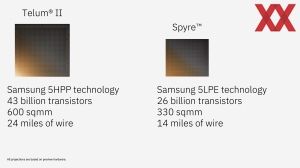

Gefertigt wird der Telum II bei Samsung in 5HPP. Den Vorgänger ließ IBM ebenfalls bei Samsung, allerdings in 7 nm fertigen. Die Größe gibt der Hersteller mit 600 mm² bei 43 Milliarden Transistoren an.

IBMs Spyre KI-Beschleunigerkarte

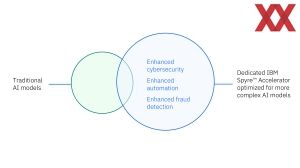

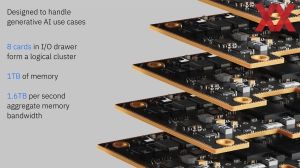

Neben den Beschleunigern mit einer Rechenleistung von 24 TOPS, die sich direkt auf dem Telum-II-Chip befinden, stellt IBM eine eigene Beschleunigerkarte namens Spyre vor.

Dabei handelt es sich um eine PCIe-5.0-Karte, die über 16 Lanes angebunden ist und die eine KI-Rechenleistung von mehr als 300 TOPS zur Verfügung stellen soll. Dem Chip zur Seite stehen 128 GB LPDDR5-Speicher.

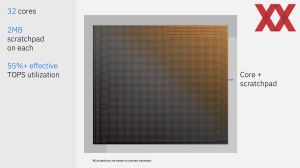

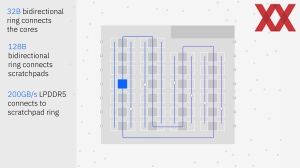

Der Spyre-Chip verfügt über 32 KI-Kerne und 2 MB an Scratchpad-Speicher. Ein Ringbus mit 32 Byte pro Taktzyklus verbindet die 32 Kerne miteinander. Der Scratchpad-Speicher ist über 128 Byte pro Taktzyklus in einem Ringbus angebunden. Die 128 GB LPDDR5 sind wiederum mit 200 GB/s an den Scratchpad-Speicher angeschlossen.

Auch der Spyre-Chip wird bei Samsung gefertigt, allerdings im 5LPE getauften Verfahren. Er kommt auf 330 mm² und 26 Milliarden Transistoren. IBM will den Telum II und die Spyre-Karte als Gesamtsystem anbieten, welches dann auf eine Rechenleistung von 30 PetaOPS (INT8) kommt. Zum Vergleich: Ein GB200-Beschleuniger von NVIDIA bringt es auf 20 PetaFLOPS in FP8.