Werbung

In einer Pressemitteilung gibt AMD weitere Details zum Ryzen 7 9800X3D bekannt, der in der kommenden Woche erscheinen wird. Neben der Pressemitteilung, welche Preis und Taktraten nennt, hat AMD auch ein Video veröffentlicht, in dem erstmals auch Benchmarkvergleiche gezeigt werden.

Zunächst einmal wird das Gerücht zum Preis bestätigt, welches seit heute Vormittag die Runde machte. Der Ryzen 7 9800X3D wird 479 US-Dollar kosten. Der Ryzen 7 7800X3D kam ab Frühjahr 2023 für 449 US-Dollar vor Steuern in den Handel.

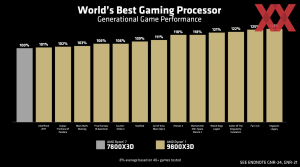

Gegenüber einem Core Ultra 9 285K soll der Ryzen 7 9800X3D im Schnitt um 20 % schneller in Spielen sein. Gegenüber dem Ryzen 7 7800X3D ist das neue Modell laut AMD um 8 % schneller. Diese Zahlen werden wir natürlich im Rahmen eines Tests überprüfen.

Im Video ist aber auch zu erkennen, was wir ebenfalls aus den Gerüchten schon wussten: AMD platziert den SRAM-Chip mit den zusätzlichen 64 MB an L3-Cache nun unter dem CCD mit den Zen-5-Kernen. Im Pressetext wird dies bestätigt:

In der Animation ist zu erkennen, dass der SRAM-Chip dabei die gleiche Größe wie das CCD hat. Dies dürfte den höheren Takt erklären und Auswirkungen auf die Temperaturen haben. Zudem benötigt AMD keinerlei Filler-Chiplets, welche den Bereich rechts und links neben dem sonst kleineren SRAM-Chip füllen. Auf der anderen Seite hat der SRAM-Chip in dieser Form auch die Aufgabe die Verbindung zwischen dem Interposer des Package und dem CCD herzustellen. Signal- und Versorgungsleitungen führen durch den SRAM-Chip zum CCD.

Erscheinen wird der Ryzen 7 9800X3D am 7. November. Einen Euro-Preis kennen wir noch nicht.

| Modell | Kerne / Threads | Basis-Takt | Boost-Takt | L3-Cache | Speicher | TDP | Preis |

|---|---|---|---|---|---|---|---|

| Ryzen 9 9950X | 16 / 32 | 4,3 GHz | 5,7 GHz | 2x 32 MB | DDR5-5600 | 170 W | 620 Euro |

| Ryzen 9 9900X | 12 / 24 | 4,4 GHz | 5,6 GHz | 2x 32 MB | DDR5-5600 | 120 W | 450 Euro |

| Ryzen 7 9800X3D | 8 / 16 | 4,7 GHz | 5,3 GHz | 32 + 64 MB | DDR5-5600 | 120 W | 479 US-Dollar |

| Ryzen 7 7800X3D | 8 / 16 | 4,2 GHz | 5,0 GHz | 32 + 64 MB | DDR5-5200 | 120 W | 440 Euro |

| Ryzen 7 9700X | 8 / 16 | 3,8 GHz | 5,5 GHz | 32 MB | DDR5-5600 | 65 W | 340 Euro |

| Ryzen 5 9600X | 6 / 12 | 3,9 GHz | 5,4 GHz | 32 MB | DDR5-5600 | 65 W | 245 Euro |

Datenschutzhinweis für Twitter

An dieser Stelle möchten wir Ihnen einen Twitter Feed zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Twitter setzt durch das Einbinden des Applets Cookies auf ihrem Rechner, mit welchen sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf diesen Feed. Der Inhalt wird anschließend geladen und Ihnen angezeigt.Ihr Hardwareluxx-Team

Tweets ab jetzt direkt anzeigen

Update:

Im Video liefern die Kollegen von GamersNexus noch etwas Hintergrundinformationen.

Really, it was the structural silicon over the core that was the blanket. In the original one, it was the core die that was thin. It was thinned down to, I think, 20 microns or something. If you think about it, all the heat that the cores are generating is in that 20-micron layer before it hits that oxide layer that Josh was talking about. So what we saw was that the heat would go laterally because it couldn't go vertically. Because of that, it would pool up. Now, the bottom thinnest layer is the X3D and the core CCD is actually much thicker. I think that helps a lot with the heat dissipation.

Every layer that the CCD had to go through to get heat out to the IHS was a problem and you just had more layers. Because of the way you have to assemble the package was, even on top of the SRAM there's that carrier wafer that's just more dead silicon up there. That's not a good conductor. It's going through all of those layers, then it's going through the indium, then it's going through the IHS.

It was structural bonding layers that they had to put for stability reasons and to help adhere it. In the original package they needed 3 and there was a standard safe thickness for those. When you look at the package stackup, those are some of the biggest insulators, so they were causing a lot of problems.

We worked with TSMC on how much we can actually reduce that oxide layer and what we could do to make them less insulating. We prototyped it with some Zen 4 X3Ds, but took those learnings and applied them to the new stackup. There are much [fewer] of them, which is the best, and the ones we do have were optimized to be less impacting.

Demnach musste man in der bisherigen X3D-Technik den CCD extrem dünn abschleifen. Dies führt allerdings dafür, dass die Abwärme kaum mehr in vertikaler Richtung abgegeben werden kann – zusätzlich zu der Problematik, dass der Struktur-Die die Kerne abdeckte. Zudem benötigte man mehr sogenannte Structural Bonding Layers, die weitere Isolationsschichten bilden und deren Anzahl man nun reduzieren konnte.