Werbung

Microsoft hat auf der Ignite-Konferenz eine neue Cloud-Instanz namens Azure HBv5 vorgestellt, die auf einem neuen Custom-EPYC-Prozessoren basiert, den man gemeinsam mit AMD entwickelt hat. Der EPYC-Prozessor verwendet Zen-4-Kerne und kombiniert diese mit HBM3. Die VMs von Azura sollen damit auf Anwendungen ausgelegt sein, die auf eine besonders hohe Speicherbandbreite angewiesen sind, deren Datenmenge aber größer war, als der L3-Cache der Milan-X-Prozessoren mit zusätzlichem 3D V-Cache auf jedem der CCDs. Die Prozessoren der EPYC-7000X-Serie bieten 768 MB an L3-Cache.

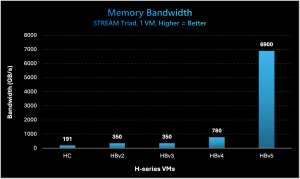

Einen EPYC-Prozessor mit HBM gab es anders als bei Intel mit den Xeon-Max-CPUs bei AMD bisher nicht. 6,9 TB/s an Speicherbandbreite soll die Azure HBv5 VM anbieten können. Dabei besteht diese aber nicht aus nur einem Prozessor, sondern Microsoft gibt 352 Zen-4-Kerne mit einem Takt von bis zu 4 GHz an. Jedem Kern sollen bis zu 9 GB zur Verfügung stehen und die erwähnten 6,9 TB/s werden im STREAM Triad auf 400 bis 450 GB an HBM3 erreicht. SMT ist deaktiviert und pro Server gibt es nur eine VM, sodass sich nicht mehrere VMs die Hardware teilen müssen.

Angebunden sind die Server über 800 GBit/s auf Basis von NVIDIAs Quantum-2 InfiniBand. Per Azure VMSS Flex ist es möglich, eine Anwendung auf mehrere VMs zu verteilen. Der lokale NVMe-Speicher eines Servers beläuft sich auf 14 TB mit einer Datenraten von 50 GB/s für das Lesen und 30 GB/s für das Schreiben von Daten.

Bisher verwendete Microsoft in den Azure-Instanzen wie HBv3 und HBv2 (EPYC-Prozessoren der dritten Generation mit 3D V-Cache alias Milan-X und die der zweiten Generation alias Rome. Im Vergleich dazu bieten die neuen Custom-EPYC-CPUs mit HBM eine deutlich höhere Bandbreite.

Offenbar waren die EPYC-Prozessoren mit HBM als Instinct MI300C in der Entwicklung bei AMD. Die Modellbezeichnung lautet EPYC 9v64H. Auch wissen wir aktuell noch nicht, wie viele EPYC-Prozessoren Bestandteil der HBv5 VM sind. Da Microsoft in der Netzwerkanbindung von insgesamt 800 GBit/s, aufgeteilt in viermal 200 GBit/s, spricht, könnte man von vier Prozessoren ausgehen. Bei 352 Kernen würde dies 88 Kerne pro Prozessor bedeuten – eine eher ungewöhnliche Zahl. Dies liegt daran, dass AMD hier vier CCDs mit jeweils 24 Kernen verwendet. Die CPU bietet demnach 96 Kerne, von denen aber nur 88 Kerne der VM zur Verfügung stehen.

In jedem Fall ist es nicht damit getan, die Speichercontroller des IOD von DDR4 auf einen solchen für HBM zu tauschen. Bei DDR4 sind 64+8 Bits pro Speicherkanal notwendig. Jeder HBM-Stack/Chip benötigt aber eine 16x 64 Bit breite Anbindung. Das Speicherinterface ist bei HBM also um ein Vielfaches breiter, als bei klassischem DDR. Der IOD hat womöglich mehr mit dem der Instinct-MI300-Familie zu tun, der bereits HBM3 unterstützt.

Die Azure HBv5 VM steht ab sofort als Preview zur Verfügung und wird ab der ersten Jahreshälfte 2025 allen Kunden angeboten werden können.