Werbung

Offenbar hat AMD per AGESA eine Funktion der Zen-4-Architektur abgeschaltet, was einer ersten Analyse der Kollegen von Chips and Cheese keinerlei Einfluss auf die Leistung hat, aber dennoch einen interessanten Umstand darstellt. Konkret geht es um den Loop Buffer der Zen-4-Architektur, also vor allem der Prozessoren der Ryzen-7000-Serie sowie der entsprechenden EPYC-Modelle.

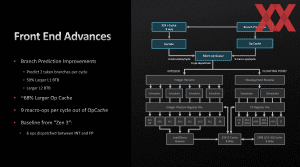

Bisher setzt AMD einen Loop Buffer ausschließlich in der Zen-4-Architektur ein, für Zen 5 verzichtet man darauf wieder. Eine vollständige Dokumentation des Loop Buffer gibt es bei AMD nicht, was auch zugleich ein Hinweis darauf sein könnte, dass es sich bei der Implementation nur um einen Testlauf gehandelt haben könnte. Konkret genannt wird er nur als ein Micro-Op Dispatcher, neben dem Op Cache und der Decoder-Einheit.

Der Loop Buffer ist in einer Linie eine Maßnahme zur Leistungsoptimierung im Hinblick auf dem Stromverbrauch. Insgesamt passen in der Zen-4-Architektur 144 Einträge in den Loop Buffer, bei aktiviertem SMT sind es 72 Einträge pro Thread. Allerdings scheint dem Loop Buffer keine allzu wichtige Rolle zuzukommen bzw. seine Auswirkungen sind nicht nennenswert, da der Op Cache bereits eine ausreichende Bandbreite liefert und die nachgelagerten Rename- sowie Allocate-Einheiten der Kerne auslasten kann. Stattdessen ermöglicht es der Loop Buffer dem Kern einen Großteil des Frontends, einschließlich des Op Cache, abzuschalten.

Aufgefallen ist die Abschaltung des Loop Buffer nach der Installation eines aktuelleren BIOS auf dem ASRock B650 PG Lightning. Zusammen mit einem Ryzen 9 7950X3D zeigte sich mit dem BIOS 3.10 und der AGESA 1.2.0.2a die entsprechende Änderung über ein Hardware Performance Monitoring, welches keine Rückmeldung zum Loop Buffer mehr lieferte. Mit der BIOS-Version 1.21 (AGESA 1.0.0.6) war dies noch möglich.

Die Kollegen von Chips and Cheese haben einige Benchmarks gemacht und versucht zu analysieren, ob das Fehlen des Loop Buffers Auswirkungen hat. Die Ergebnisse waren allerdings sehr gemischt und lassen keinerlei Rückschlüsse zu.

Die Frage, warum AMD den Loop Buffer bei den Prozessoren mit Zen-4-Architektur wieder abgeschaltet hat, kann vorerst nicht geklärt werden. Meist wird ein solcher Schritt gegangen, wenn es einen Fehler in der Umsetzung einer solchen Funktion gegeben hat. Ein solcher Vorgang ist für die Zen-4-Architektur bisher aber nicht bekannt. Intel musste den Loop Buffer (LSD) in der Skylake-Architektur abschalten und verwendet einen solchen genau wie diverse ARM-Designs bereits seit einigen Jahren. Hier wird bei den Programming Guides auch auf entsprechende Optimierungen verwiesen, was bei AMD nicht der Fall ist.

Für AMD könnte es in der Zen-4-Architektur der erste Versuch gewesen sein, einen Loop Buffer umzusetzen. Ob man daran gescheitert ist eine Validierung dessen letztendlich fehlgeschlagen ist, spielt letztendlich wohl keine Rolle. Die Zen-Architektur ist durch den Op Cache entsprechend ausgelegt, sodass AMD auf einen Loop Cache nicht angewiesen ist.

Letztendlich zeigt die Integration eines Loop Cache in der Zen-4-Architektur, dass AMD die entsprechenden Ressourcen zur Entwicklung neuer Core-Komponenten hat. Man lässt die Ingenieure experimentieren, ohne ein Risiko einzugehen oder das Produkt zu gefährden. Am Ende bleibt der Loop Cache in der Zen-4-Architektur eine Randnotiz, mehr nicht.