Werbung

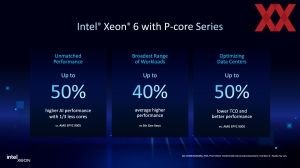

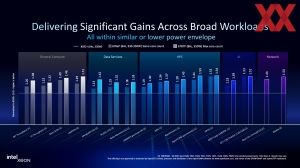

Nachdem Intel im vergangenen Jahr bereits die 6700E-Serie mit bis zu 144 Efficiency-Kernen und die 6900P-Serie mit bis zu 128 Performance-Kernen vorgestellt hatte, folgt nun planmäßig zum ersten Quartal die Vorstellung der 6700P/6500P- sowie der 6900E-Serie. Innerhalb dieser gibt es ein paar Besonderheiten in der Ausrichtung und Positionierung, auf die wir nun genauer eingehen werden. Intel hat aktuell mit einem sinkenden Absatz für das Datacenter-Geschäft zu kämpfen. AMD knabbert dem einstigen Branchen-Primus immer mehr an Marktanteil ab. Ob die Xeon-6-Serie hier eine Kehrtwende einleiten kann, wird sich zeigen müssen.

Zu den bisher vorgestellten Xeon-Prozessoren hatten wir entsprechende Tests. Dies wären:

- Intels Comeback: Zweimal Xeon 6972P mit 96 Kernen und 12x DDR5-6400 im Test

- Intel Xeon 6700E Serie: 144 Efficiency-Kerne im Test

Bisher fehlt uns noch ein Test der stärkeren 6900P-Modelle mit jeweils 128 Kernen und auch die Leistung der MRDIMMs konnten wir uns noch nicht genauer anschauen.

| Xeon-6-Serie | Sockel | Kerne | TDP (Max) | Speicherkanäle | PCIe / CXL | UPI-Links | Start |

| Xeon 6700E | LGA7529 | 144 E-Kerne | 350 W | 8x DDR5-6400 | 88 | 4x UPI 2.0 | Juni 2024 |

| Xeon 6700P | LGA7529 | 86 P-Kerne | 350 W | 8x DDR5-6400 8x MCR-8000 | 88 | 4x UPI 2.0 | Q1 2025 |

| Xeon 6900E | LGA7529 | 288 E-Kerne | 500 W | 12x DDR5-6400 | 96 | 6x UPI 2.0 | Q1 2025 |

| Xeon 6900P | LGA7529 | 128 P-Kerne | 500 W | 12x DDR5-6400 12x MCR-8800 | 96 | 6x UPI 2.0 | Q3 2024 |

Zur Einordnung vorweg: Die Xeon-Prozessoren mit Performance-Kernen verwenden die Redwood-Cove-Architektur und für die Prozessoren mit Efficiency-Kernen die Crestmont-Architektur. Grundsätzlich ist es möglich, innerhalb einer Plattform beide Kerne zum Einsatz zu bringen. Die 6900-Serie setzt auf den LGA7529 mit zwölf Speicherkanälen und bis zu 96 PCIe/CXL-Lanes und die 6700-Reihe auf den LGA7529 mit acht Speicherkanälen und 88 PCIe/CXL-Lanes.

Diese Flexibilität in der Plattform wird durch zwei Faktoren möglich: Da sich die Speichercontroller in den Compute-Tiles befinden, muss eine jeweilige Anzahl an Compute-Tiles vorhanden sein, damit das Angebot an Speicherkanälen abgedeckt werden kann. Für die 6900-Serie sind dies entweder zwei Compute-Tiles mit den Efficiency-Kernen oder drei Compute-Tiles mit den Performance-Kernen. Für die 6700-Serie sind entweder ein Compute-Tile mit Efficiency-Kernen oder bis zu zwei mit Performance-Kernen vorgesehen.

Die I/O-Kompatibilität wird durch den Einsatz zweier identischer I/O-Tiles sichergestellt, die für jedes der eben erwähnten Packages verwendet werden. Während die Compute-Tiles in Intel 3 gefertigt werden, kommt für die I/O-Tiles die Fertigung in Intel 7 zum Einsatz. Die Verbindung der Tiles erfolgt per EMIB.

Gleich zu Beginn sei gesagt: Während es die 6900P-, 6700P/6500P- und 6700E-Serie auch in den Servern der OEMs geben wird, ist dies für die 6900E-Serie nicht der Fall. Die großen Sierra-Forest-CPUs wird Intel nur in direkter Zusammenarbeit mit den Hyperscalern anbieten. Dies tut man laut Intel, da die Prozessoren mit bis zu 288 Efficiency-Kernen ohnehin fast ausschließlich für die großen Cloud-Anbieter interessant sind.

Einer der Partner, die von Intel bereits angekündigt wurden, ist AWS. Je nach Anwendung können AWS und Intel abstimmen, wie viele Kerne unter welchem Power-Budget verwendet werden sollen. Intel liefert die entsprechende Konfiguration. Da große Anbieter wie AWS, aber auch Microsoft mit Azure oder Google mit der eigenen Cloud ausreichende Stückzahlen abrufen, werden auch die kompletten Server in Eigenregie entwickelt. Alles ist aufeinander abgestimmt und macht die Entscheidung, die 6900E-Serie nur als Custom-Produkt anzubieten, umso verständlicher.

Während die Prozessoren der 6900P-Serie nur für 2S-Server vorgesehen sind, skalieren die Modelle der 6700P-Serie auch auf 4S- und 8S-Systemen. Sprechen wir in der 6900P-Serie von maximal 256 CPU-Kernen je Server, sind es in der 6700P-Serie bei 86 Kernen und acht Sockeln satte 688 Kerne sowie 64 Speicherkanäle. Arbeiten diese Kerne zusammen, kommt dem UPI-Interconnect zwischen den Sockeln eine wichtige Rolle zu. Theoretisch möglich ist ein maximaler Speicherausbau von 32 TB an Arbeitsspeicher je Server. Je nach Anwendung sind dies Faktoren, die entscheidend für die Kunden sein können.

AMD bietet aktuell nur noch die Unterstützung von 2S-Servern. Aber auch hier ist die Anzahl an Kernen, Speicherkanälen und im Speicherausbau fast auf Augenhöhe dessen angekommen, was Intel bieten kann. Laut AMD sind 4S- und 8S-Konfigurationen auch nur für wenige Kunden interessant, weshalb man sich auf 2S-Systeme konzentriert.

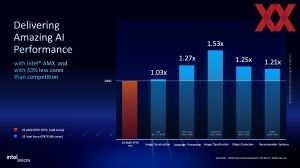

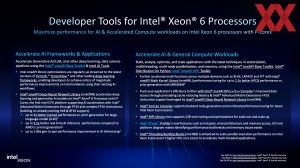

Als x86-Konkurrenz sieht sich NVIDIA im Hinblick auf die KI-Leistung gut aufgestellt. Auf den Prozessoren kommt aber allenfalls ein Inferencing zum Einsatz, während das Training auf den dedizierten KI-Beschleunigern angewendet wird. In der Nutzung von KI-Netzwerken wie den LLMs oder der Bildgenerierung könnten Prozessoren eine wichtige Rolle spielen. Dank der AMX-Einheiten in den Kernen will Intel mit den Xeon-6-Prozessoren eine Alternative zu den dedizierten Beschleunigern anbieten können.

Intel will natürlich auch beim KI-Training mitspielen. Hier tut man dies als Host-CPU und engster Partner ist NVIDIA. Auch wenn NVIDIA hier mit den Grace-CPUs inzwischen eine eigene Alternative entwickelt so, so kommen meist noch x86-Prozessoren als Host zur Anwendung. Zwischen 32 und 72 Kerne haben die dafür vorgesehenen Modelle.

Eine gewisse Rechenleistung, vor allem die Anbindung per PCI-Express und eine schnelle Speicheranbindung, sind für die Host-Prozessoren für solche KI-Beschleunigersysteme entscheidend. Intel führt allerdings auch eine Verlässlichkeit der Hardware an, in der man durch die jahrzehntelange Erfahrung noch immer führend sein möchte.

In diesem Zusammenhang sei erwähnt, dass mit TDC Connect eine neue, schnelle und verschlüsselte Verbindung zwischen CPU und GPU angedacht ist. Trainingsdaten und Anfragen an die Modelle sollen so abgesichert vor fremden Zugriffen übertragen werden können. Welche GPUs, bzw. KI-Beschleuniger TDX Connect unterstützen werden, ist offiziell noch nicht bekannt. In Anbetracht der guten Zusammenarbeit zwischen Intel und NVIDIA darf man davon ausgehen, dass NVIDIA in Kürze eine entsprechende Unterstützung ankündigen wird. NVIDIA erwähnt in seinem Backwell-Whitepaper zudem, dass die Blackwell-Beschleuniger die ersten sind, die TEE-I/O (Trusted Execution Environment) bzw. TDC Connect unterstützen werden.

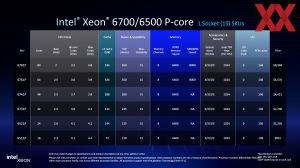

Xeon 6700P und 6500P

Während die Xeon-6900P-Serie auf den größeren LGA7529 der Birch-Stream-Plattform setzt, werden die Xeon 6700P und 6500P genau wie die von uns bereits getesteten Prozessoren der Xeon-6700E-Serie als SP-Modelle auf den Sockel LGA4710 setzen.

Anstatt bis zu 128 Kernen in einem 1S- und 2S-Server kommen für die 6700P-Serie bis zu 86 Kerne je Prozessor zum Einsatz. Zudem bietet diese acht Speicherkanäle mit der Unterstützung von DDR5-6400 (1DPC), bzw. DDR5-5200 (2DPC) sowie MRDIMMs mit 8.000 MT/s. Per UPI 2.0 können bis zu acht Xeons in einem Server zusammenarbeiten und somit kommt ein Server theoretisch auf bis zu 688 Kerne. Zusammen mit achtmal acht Speicherkanälen ergibt sich eine enorme Rechenleistung.

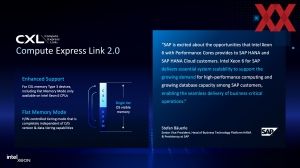

Je nach Multi-Socket-Konfiguration bieten die Prozessoren der 6700P-Serie bis zu 88 PCI-Express-Lanes nach 5.0-Standard und 64 CXL-2.0-Lanes.

Auch wenn sich der Fokus immer auf die Spitzenmodelle und das High-Performance-Umfeld richtet, so spielt sich die Masse eher im Bereich von 24 bis 48 Kernen ab. Für diese sieht Intel die 6500P-Serie vor, die dann auch nur eine 2S-Konfiguration ermöglicht.

1S-Variante mit bis zu 136 PCIe-Lanes

Vor allem im Storage-Bereich geht es darum, so viele PCI-Express-Lanes wie möglich anbieten zu können. Dazu bietet Intel einige Modelle innerhalb der 6700P- und 6500P-Serie an, die als Single-Socket-Lösung bis zu 136 PCI-Express-Lanes anzubieten haben.

Für eine 1S-Konfiguration kann Intel die UIO (Universal IO-Blöcke) des I/O-Tiles anstatt für die UPI-Verbindung zu einem weiteren Sockel für weitere PCI-Express-Lanes nutzen (siehe Bild oben). Insgesamt besitzt der I/O-Tile zwei I/O-Blöcke für PCIe oder CXL und vier UIO-Blöcke, die für PCIe, CXL und UPI verwendet werden können.

Mit dem Verzicht auf UPI kann Intel für die 1S-Konfiguration also weitere PCIe-Lanes anbieten, sodass man hier auf insgesamt 136 Lanes kommt. Kunden, die nicht viele Kerne, aber möglichst viele PCIe-Lanes benötigen, wird dies sicherlich freuen. AMD bietet auf seiner aktuellen EPYC-Plattform bis zu 128 PCIe-Lanes, insofern hätte Intel hier sogar die Nase vorn.

Vier bis acht Kerne für die 6300P-Serie

Nach unten hin rundet Intel die Xeon-6-Serie mit den 6300P-Prozessoren ab. Diese beinhaltet Modelle mit vier bis acht Kernen. Ihr Einsatz ist auf 1S-Systeme beschränkt, dafür fällt die Leistungsaufnahme mit bis zu 95 W deutlich geringer aus. Dies gilt zudem für die Anzahl der PCI-Express-Lanes, von denen es nur noch 16 gibt. Die Anzahl der Speicherkanäle beträgt derer zwei.

Anstatt der Performance-Kerne auf Basis der Redwood-Cove-Architektur verwendet die 6300P-Serie die bereits angestaubte Raptor-Cove-Architektur. Diese Xeon-Serie tritt gegen AMDs EPYC-4004-Serie an.

Anhand dieser und der weiteren Spezifikationen wird deutlich, wo Intel diese Modelle positioniert.