Werbung

Auf dem VLSI Symposium hielten Forschungsmitarbeiter von TSMC einen interessanten Vortrag über eine mögliche Kühllösung zukünftiger Chips, die eine direkte Integration einer Wasserkühlung in den Chip selbst vorsieht. Studien und Versuche hat es in der Vergangenheit bereits gegeben. Die Konzepte sehen dabei immer Mikrokanäle vor, die direkt in die obersten Schichten des Chips eingearbeitet werden. Für TSMC scheinen solche Lösungen aber immer konkreter zu werden und insofern hat mich sich etwas tiefergehend mit der Materie beschäftigt und nun untersucht, welche Möglichkeiten es zur Umsetzung gibt.

Zunächst einmal sollte man sich die Frage stellen, warum eine direkte Wasserkühlung im oder auf auf dem Chip notwendig sein könnte. Chips wie der A100-Beschleuniger von NVIDIA kommt zusammen mit dem HBM2E und als SXM4-Modul bereits auf eine Abwärme von bis zu 500 W. Für Intels Xe-HPC-Chip Ponte Vecchio stehen sogar bis zu 600 W im Raum. Es wird also trotz moderner Fertigungstechniken immer schwieriger solche Chips auch zu kühlen. Eine Wasserkühlung ist im Datacenter-Bereich keine Besonderheit. Die Kühler sitzen dabei auf den Prozessoren und Beschleunigern und transportieren die Abwärme ab. Doch auch wenn die Chips eine Fläche von mehreren hundert Quadratmillimeter haben, eine Abwärme im Bereich von 400+ W auf einer derart kleinen Fläche lässt sich nicht einfach bewältigen.

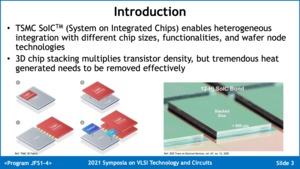

Hinzu kommt, dass zukünftig vermehrt Chips mit 3D-Integration zum Einsatz kommen werden. AMD wird den 3D V-Cache als zusätzlichen SRAM für die Prozessoren ab Ende 2021/Anfang 2022 zum Einsatz bringen. Der zusätzliche Cache befindet sich dabei direkt über dem schon vorhandenen L3-Cache und sitzt auch nicht über den Zen-3-Kernen, was die Kühlung dieser erschweren würde. Aber ein 3D-Stacking wird hier nicht Halt machen, sondern immer komplexere Verbindungen sind vorgesehen. Wenn man diese nicht vollständig in X- und Y-Richtung ausbreiten will, wie dies bei Ponte Vecchio der Fall ist, dann wird ein Stapeln und Kühlen der Chips in den unteren Ebenen immer wichtiger.

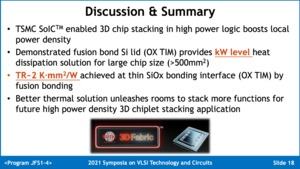

TSMCs Ziel ist es Kühllösungen für eine Abwärme im Bereich von 10 W pro Quadratmillimeter zu entwicklen. Je nach Größe des Chips sind diese 10 W/mm² aber schon sehr ambitioniert. Für größere Chips (500 mm² und mehr) peilt TSMC eine TDP von 2.000 W (2 kW) an.

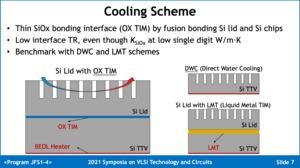

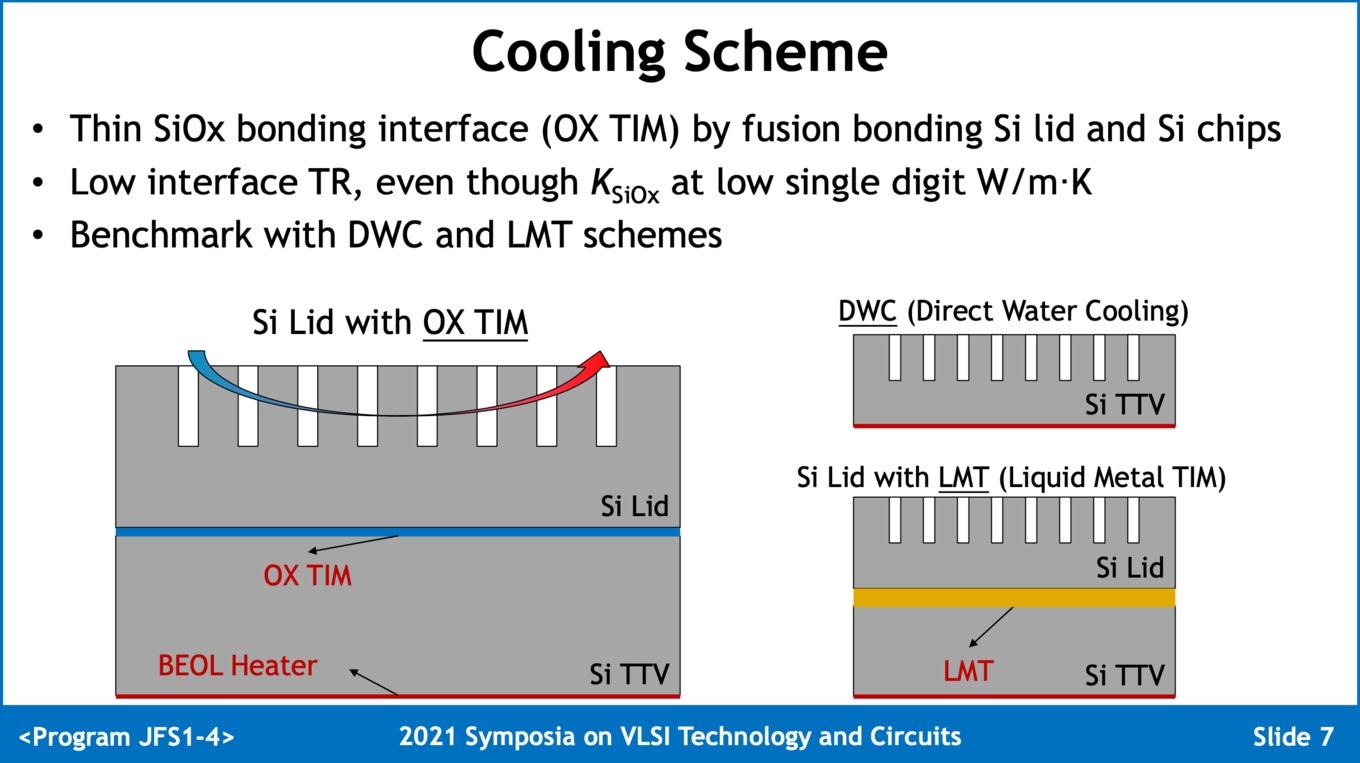

Nun gibt es mehrere Methoden solch eine Wasserkühlung in den Chip selbst zu integrieren. Um die Fehlerrate so gering wie möglich zu halten, sollten die Chips selbst weiterhin eigenständig gefertigt und dann mit der Kühlung versehen werden. Aber die direkte Methode dürfte gleichzeitig auch die effizienteste sein:

- DWC (Direct Water Cooling): Die Kanäle für die Wasserkühlung werden direkt in die obersten Silizium-Schichten des Chips eingearbeitet

- Si Lid with OX TIM: Die Wasserkühlung wird in eine eigene Silizium-Schicht eingearbeitet und diese wiederum mittels eines OX (Silicon Oxide Fusion) als Thermal Interface Material (TIM) mit dem Chip zusammengebracht

- Si Lid with LMT: Anstatt der OX-Schicht kann auch einfach Flüssigmetall zum Einsatz gebracht werden

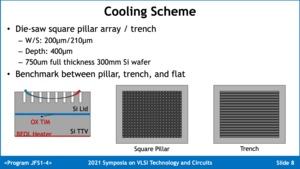

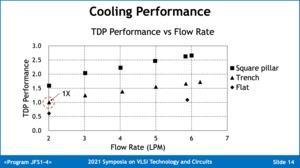

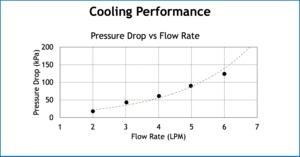

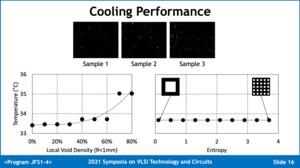

Um die Kanäle in das Silizium einzuarbeiten, wurde eine Technik verwendet, die auch zum Schneiden der Chips aus dem Wafer zum Einsatz kommt. Eine Diamantsäge schneidet 200 bis 210 µm breite und 400 µm tiefe Kanäle. Die Dicke der Siliziumschicht beträgt für einen 300-mm-Wafer 750 µm. Diese Schicht sollte natürlich so dünn wie möglich sein, um die Wärmeübergang vom aktiven Chip darunter zu vereinfachen. TSMC testete zudem, ob Kanäle in einer Richtung ausreichend sind, oder ob quadratische Säulen (also Schnitt in Quer- und Längsrichtung) die beste Wärmeabfuhr bieten. Auch eine einfache flache Oberfläche ohne Kanäle hat man getestet.

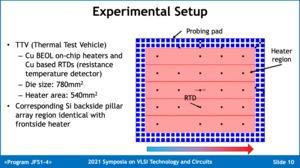

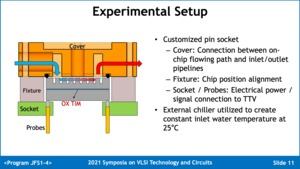

Das TTV (Thermal Test Vehicle) bestand aus einem Heizelement aus Kupfer. Im Heizelement selbst befanden sich Temperatursensoren. Die Oberfläche des Heizelements betrug 540 mm², die gesamte Fläche des TTV 780 mm². Das TTV wurde in einen eigenen Sockel gespannt, der die Versorgung mit Strom, die Zu- und Ableitung des Wassers und die Verbindung von Sensoren ermöglichte. Das Wasser wurde mit einer konstanten Temperatur von 25 °C eingeleitet.

Die Ergebnisse sahen wie folgt aus:

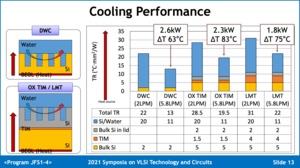

Für das Direct Water Cooling, also das Vorhandensein der Kühlung im Chip selbst, erreicht es TSMC eine Abwärme von 2,6 kW abzuführen. Die Temperaturdifferenz betrug dabei 63 °C. Für die Verbindung zwischen Chip und Silizium-Schicht mit Wasserkülung mittels OX TIM kommt TSMC auf eine Abwärme von 2,3 kW die abgeführt werden kann und die Temperaturdifferenz lag bei 83 °C. Flüssigmetall zwischen den beiden Schichten ermöglichte den Abtransport von nur 1,8 kW und eine Temperaturdifferenz von 75 °C. TSMC hat auch mit zwei Durchflussmengen getestet – einmal 2 l pro Minute und einmal 5,8 l pro Minute. Angeben zur Abwärme und Temperaturfifferenz macht man aber nur für 5,8 l pro Minute, da nur dies praktikable Werte ergab.

Der Wärmewiderstand sollte so gering wie möglich sein. TSMC schlüsselte hier aber auch auf, wo denn die größte Hürde beim Wärmeübergang ist. Für das DWC ergibt sich eigentlich nur der Übergang zwischen Silizium und Wasser als größte Schwierigkeit. Kommen getrennte Ebenen zum Einsatz, gibt es hier einen weiteren Übergang, den die OX-Verbindung am besten löst.

Auf die Frage, welche Struktur der Kanäle die bessere ist, hat TSMC ebenfalls eine klare Antwort: Die TDP-Performance einer flachen Oberfläche ist unzureichend und verbessert sich auch mit der Durchflussrate nicht sonderlich. Die besten Ergebnisse liefern die Kanäle in beiden Richtungen (Square Pillar), während einfache Kanäle deutlich weniger Abwärme abführen können. Wir sprechen hier von einer bis zu Faktor zwei besseren Wärmeabfuhr.

TSMC hält es für durchaus möglich, dass zukünftige Chips auf direkterem Wege mit einer Wasserkühlung versehen werden. Dann sitzt kein Kühler aus Metall mehr auf dem Chips, sondern das Wasser wird direkt durch eine Silizium-Schicht geführt und kühlt den darunterliegenden Chip. Mehrere Kilowatt an Abwärme sollen somit abgeführt werden können. Bis wir eine solche Lösung aber in der Praxis sehen werden, könnte es noch etwas dauern. Noch immer evaluieren verschiedene Hersteller eine solche Kühlung.