emissary42

Kapitän zur See

Thread Starter

- Mitglied seit

- 13.04.2006

- Beiträge

- 39.073

- Ort

- Nehr'esham

- Desktop System

- Endlos-Baustelle

- Details zu meinem Desktop

- Prozessor

- AMD & Intel

- Mainboard

- alle Hersteller

- Kühler

- Luft

- Speicher

- G.SKILL, Corsair & Co

- Display

- 8K, 5K, 4K

- Netzteil

- 80plus Platinum

Intel Ibex Peak

Chipsätze: P55 /P57 / H55 / H57 / Q57

Spezifikationen

Plattformen

Hersteller-Produktseite: P55, tba

Release-Termine: (Q3/2009 für P55), Q1/2010 für H55/H57

Preisvergleich Mainboards: Geizhals

Ibex Peak im Überblick

Sockel-Chaos

News

Sammelthreads

Reviews

Bilder

Anhang A) "Braidwood" --> vermutlich gecancelt

Chipsätze: P55 /

Spezifikationen

Intel P55 (BD82P55)

Typ: PCH – Plattform Controller Hub (Single Chip, Funktionsumfang entspricht einer Southbridge)

Sockel: LGA1156 Varianten ( LGA1156, LGA1156B, LGA1156C)

Anbindung-CPU: DMI - Direct Media Interface

PCIe-Lanes: 8 PCIe (2.0), ? Links

Storage: 6x Serial ATA 3.0 Gbit/s (RAID 0, 1, 0/1, 5, JBOD, Matrix)

Networking: 1x Gigabit Ethernet (RJ45)

IO: 14x USB 2.0

Der BD82P55 wird von Intel in 65nm gefertigt und verfügt nicht über einen Heatspreader. Die TPD liegt Southbridge-typisch im einstelligen Wattbereich, etwa 4.5w. Eine besonders aufwändige Kühlung ist damit nicht notwendig. Die 8 PCIe-Lanes des BD82P55 stehen zusätzlich zu den 16 Lanes der CPU zur Verfügung, damit erhöht sich die Anzahl der PCIe-Lanes der gesamten Plattform auf 24. Einige Hersteller planen den Einsatz von Chips wie Nvidias NF200 oder Hydravision, um die virtuelle Zahl an Lanes weiter zu erhöhen und damit Triple SLI oder gar Quad-Crossfire zu ermöglichen.

Feautures

- Matrix Storage Technology 9.0 mit FIS Port Multiplier (das erste Stepping des P55 vermutlich ohne!)

- Thermal Sensor Data via SMBUS für diskrete Onboard-Steuerungen

- Integrated Clocking Buffer Through Mode

- vermutlich für die H/Q-Serie reserviert:

- Active Management Technology 6.0

- Anti-Theft Technologie

- Remote PC Assist Technologie

Plattformen

1) Piketon

Sockel: 1156

CPU: Lynnfield (inoffiziell "Core i5")

Plattform Release: Q3/2009

- basiert auf der Nehalem Architektur

- unterstützt: Intel Turbo Boost / Turbo Modus & Hyper-Threading Technology

- PU: 4 Cores (8 Threads), 8 MB Intel SmartCache

- MCH: Dual-Channel DDR3

- PEG: 1x PCIe (2.0) x16 oder 2x PCIe (2.0) x8, SLI + Crossfire Unterstützung

2) Kings Creek

Sockel: 1156(B/C)

CPU:Havendale (45nm Nehalem, canceled), Clarkdale

Plattform-Release:

- basiert auf der Westmere Architektur (32nm), Clarkdale entspricht einem Havendale Shrink

- unterstützt: Intel Turbo Boost / Turbo Modus & Hyper-Threading Technology

- PU: 2 Kerne (4 Threads), 4 MB Intel SmartCache

- MCH: Dual-Channel DDR3

- IGP: Integrierter Grafikkern (iGFX, 45nm) , Flexible Display Interface (FDI*)

- PEG: 1x PCIe (2.0) x16

Havendale Q1 / 2009, Clarkdale Q2-Q3 / 2010

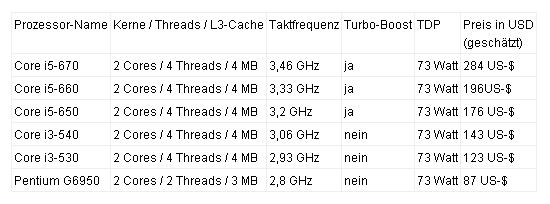

Clarkdale Modelle:

*FDI: "The Intel Flexible Display Interface will allow the integrated graphics core in the Havendale processor to channel its graphics data to the display controller in the future Ibex Peak (Intel 5-series) chipset for output to the monitor."

Hersteller-Produktseite: P55, tba

Release-Termine: (Q3/2009 für P55), Q1/2010 für H55/H57

Preisvergleich Mainboards: Geizhals

Ibex Peak im Überblick

Der P57 sollte zusätzlich unterstützen:

Im Moment ist der Release des P57 zu einem späteren Zeitpunkt jedoch mehr als fraglich, da Intel scheinbar technische Probleme mit Braidwood hat und die Entwicklung daran angeblich eingestellt hat. Dies war das wichtigste Unterscheidungsmerkmal der beiden Chipsätze (Quelle: Digitimes).

- Braidwood Turbo Memory, NVMHCI (Non-Volatile-Memory-Host-Controller-Interface) + „ONFI“ 2.0-Schnittstelle (Open NAND Flash Interface)

- Coral Harbour

- Quiet System Technology

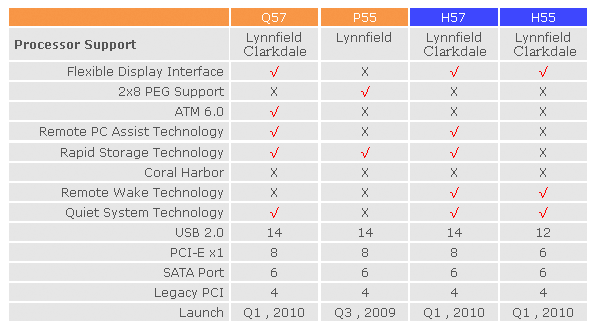

Tabelle:

Vorherige Version der Tabelle:

http://img223.imageshack.us/img223/2280/hkepctable.png

(Achtung: Havendale wurde von Intel gestrichen, siehe Dailytech News Link)

Sockel-Chaos

Ursprünglich: LGA1160

Pre-Cebit: LGA1155 (CPU, ohne IGP) & LGA1156 (CPU, mit IGP)

Cebit: LGA1156 (CPU, ohne IGP) & LGA1156B (CPU, mit IGP), LGA1156C (zu einem späteren Zeitpunkt geplant)

aktuell: LGA1156

Lochabstand: 75mm x 75mm, diagonal 11cm

News

- VR-Zone: Intel P55 Ibex Peak Chipset Features (LINK)

- Techarp: Intel's Desktop CPU Roadmap @ October, 2008 Rev. 2.0 (LINK)

- Fudzilla: LGA 1160 is now LGA 1156 (LINK)

- Fudzilla: Intel P55, P57 don't have SATA 3 support (LINK)

- Fudzilla: LGA-1156 to last six months to a year (LINK)

- Guru3D: Intel P55 Express is single-chip due Q3 2009 (LINK)

- Dailytech: Intel Replaces "Havendale" and "Auburndale" With 32nm Die Shrinks (LINK)

- Computerbase: Details zu Intels 5er-Chipsätzen für 2009/2010 (LINK)

- Intel: Westmere 32nm Press Release (LINK)

Sammelthreads

- ASRock P55 Pro

- ASUS Maximus III Formula R.o.G.

- ASUS P7H57D-V EVO

- ASUS P7P55D

- Asus P7P55D Deluxe

- ASUS SABERTOOTH 55i

- DFI LANparty DK P55-T3eh9

- EVGA P55 Series (alle Modelle)

- Foxconn Inferno Katana (-GTI) <-- sucht neues Herrchen

- Gigabyte P55-UD3/UD4/UD5

- MSI H55M-ED55

- MSI P55 Series (alle Modelle)

- Zotac H55-ITX WiFi

Sammelthread Sockel 1156 Overclocking --> http://www.hardwareluxx.de/community/showthread.php?t=638406

Reviews

Werden im Thread gepostet. Wer auf dem laufenden bleiben möchte, schaut regelmäßig vorbei oder abonniert den Thread einfach

Bilder

Hardwareluxx: DFI P55-Platine abgelichtet (LINK)

Hardwareluxx: Zu Gast bei MSI @ Cebit 2009 (LINK)

Hardwareluxx: Zu Gast bei Asus (P7K, P7K Pro) @ Cebit 2009 (LINK)

Hardwareluxx Forum: Cebit 2009 Mainboard Bilder (LINK)

Hardware-Aktuell: Intel P55 @ Cebit 2009 (LINK)

Gigabyte-Forum: Gigabyte P55-UD4P (LINK)

ECS LFH-A

Asus P7P55-Pro

ASRock P55-Deluxe

MSI P55-GD80

DFI Lanparty DK P55-T3eH8

DFI Lanparty UT P55-T3eH8

(viele weitere Bilder findet ihr Dank der Mithilfe einiger Luxxer wie Crisch hier im Thread)

Anhang A) "Braidwood" --> vermutlich gecancelt

ONFI 2.0

Übertragungsrate: 133MB/s

ONFI 2.1

Übertragungsraten: 166MB/s, 200MB/s

Besseres Power Management, erweiterte ECC-Funktionalität

ONFI Homepage: LINK

Übertragungsrate: 133MB/s

ONFI 2.1

Übertragungsraten: 166MB/s, 200MB/s

Besseres Power Management, erweiterte ECC-Funktionalität

ONFI Homepage: LINK

Auf Grund der zum jetzigen Zeitpunkt (25.03.09) teilweise noch inoffiziellen Details, sind Änderungen bei den technischen Merkmalen und den Terminen nicht ausgeschlossen. Ergänzungen, Berichtigungen (jeweils unter Angabe der Quelle) und Unterstützung bei der Pflege dieses Threads ist ausdrücklich erwünscht

Zuletzt bearbeitet: