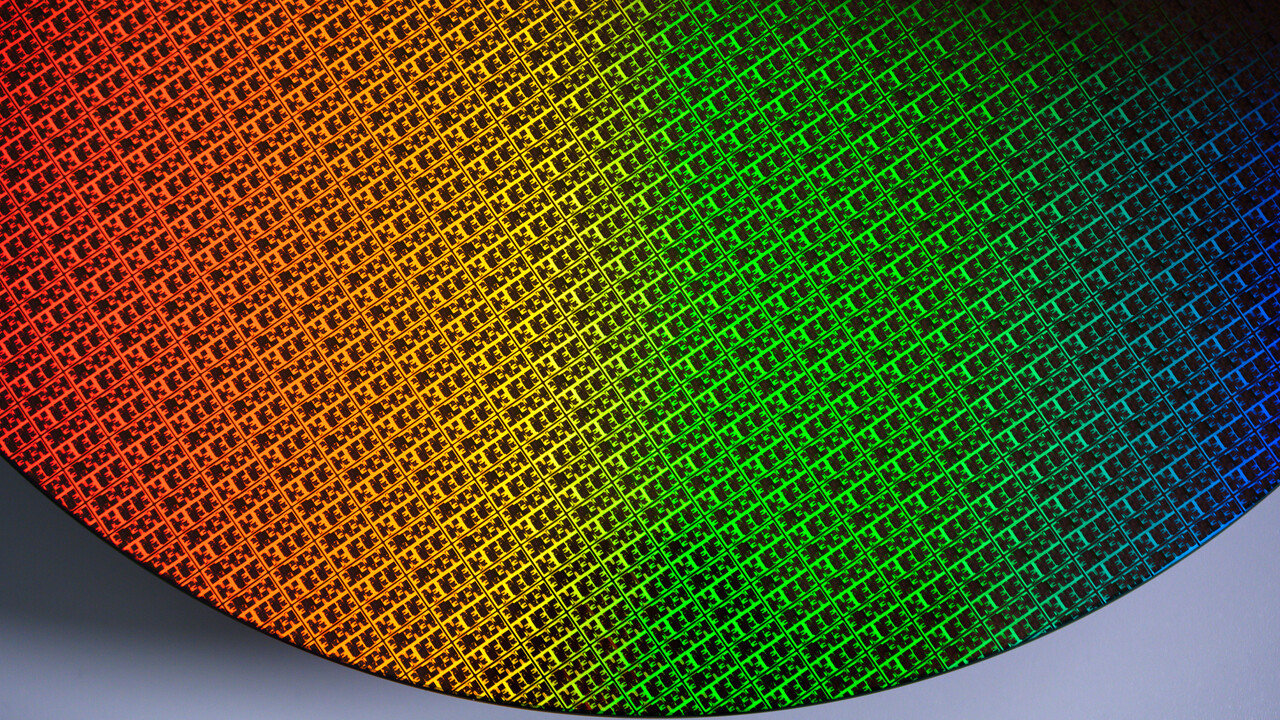

Die Fertigung des Compute-Chips mit maximal 8P+16E-Kernen soll bei TSMC in N3B stattfinden

Habt ihr einen Beleg für diese Gerücht? Alle Aussagen von Intel sagen, dass die CPU Tiles in Intel 20A gefertigt werden und praktisch keine seriöse Seite wiederholt diese Gerücht von der Fertigung der 8+16 Tiles bei TSMC. Es würde auch Null Sinn machen, da Intel 20A viel fortschrittlicher als der alte N3 Prozess ist, der nun von N3 in N3B umbenannt wurde: Wenn, dann wäre N3E schon besser, der schafft mehr Takt und ist effizienter, aber der kommt für Arrow Lake ein wenig zu spät. Also wenn man annimmt, dass Intel es sich antut die gleichen Designs (die Anzahl der Kerne ändert daran ja wenig) für zwei verschiedene Fertigungen zu entwickeln und validieren, dann würde es mehr Sinn machen das kleine 6+8 Die bei TSMC fertigen zu lassen, da dies dann auch in den mobilen CPUs eingesetzt wird und sowieso nicht die höchsten Taktraten erzielen muss, wie man es von dem 285K erwartet, der aber eben ein 8+16 Kerner ist.

Intel 20A hat sowohl PowerVia (backside power delivery) als auch RibbonFET (gate-all-around), während GAA (gate-all-around) bei TSMC erst mit N2 eingeführt wird und backside power delivery erst mit A16. Während wir mit Arrow Lake die ersten Produkte aus der Intel 20A Fertigung schon im Oktober bekommen, plant wird

TSMC die N2 Massenfertigung erst 2025 zu starten und die N2P Variante für höhere Taktraten erst in der zweiten Hälfte 2026.

Frühestens 2026 kommt auch erst

TSMCs A16 Prozess mit backside power delivery, was ursprünglich für den N2P Prozess vorgesehen war. Ende 2026 plant Intel dann schon die Risk Production von Intel 14A, seines ersten (High-NA) EUV Prozesses. Es sollte also klar sein, dass Intel 20A dem alten N3B Prozess weit überlegen ist und Intel TSMC wohl schon jetzt bzgl. der Fertigung überholt hat. Deswegen ist es auch logisch, dass Intel Pather Lake komplett in eigenen Prozessen fertigen wird und ich würde auch erwarten, dass sie ihre GPUs dann künftig selbst fertigen werden. Das GPU Tile von Arrow Lake und wer weiß welche anderen Tiles, werden aber in der Tat bei TSMC in N3 (vermutlich N3B) gefertigt und vermutlich hat dies jemand durcheinander geworfen und dann ist die Frage wo das Packaging erfolge wird, bzw. welcher Teil des Packagings wo stattfinden wird, was auch für Verwirrung in der Gerüchteküche sorgen kann.

Man kann aber klar davon ausgehen, dass alle CPUs Tiles für Arrow Lake auf der gleiche Fertigung kommen werden und dies Intel 20A sein wird, wie Intel es auch immer gesagt hat.

Mischungen aus P und E funktionieren immer noch nicht überall reibungslos, dann lieber lassen.

Auch wenn es nicht überall reibungslos funktionieren sollte, funktioniert es woanders sehr gut, wieso sollte man es also lassen?