Wenn wir jetzt von aktuellen Spielen reden die meistens mit 6 bis max 8 Cores skalieren und SingleCore Leistung für sich beanspruchen, bringt es das nicht zu sagen das man die SC oder auch MC Leistung der großen Cores (fiktiv mal CPU-Z Werte gemeint) um jeweils 100 Punkte senkt um auf der anderen Seite die zusätzlichen kleinen Cores mit ein zu binden wovon die Software nicht von profitiert.

Wieso sollte die Software nicht von den kleinen Kernen profitieren? Es sind x86er Kerne, die SW kann da also drauf laufen und ob sie darauf ausgeführt wird, bzw. welcher SW Thread darauf laufen wird, entscheidet am Ende der Task Scheduler des Betriebssystems, sofern der SW Entwickler dies nicht selbst getan hat. Bei Spielen hat man ja oft einen zentralen Thread der den Ablauf koordiniert und andere die ihm zuarbeiten, aber eben normalerweise weniger CPU Last erzeugen und diese könnten dann durchaus sinnvollerweise auf den kleinen Kernen ausgeführt werden, sofern sie eben ihre Arbeit erledigt haben, bevor der Hauptthread das Ergebnis benötigt. Dies kann der Task Scheduler ja an der Auslastung erkennen, die darf auch auf den kleinen Kernen nicht bis auf 100% steigen, sonst sollte der SW Thread besser auf einem großen Kern laufen.

Meinte das der Kompromiss sein kann das die großen Cores durch die technische Eingliederung der kleinen (fiktiv) mal nur noch 12mm² statt 15mm²/Core haben, irgendeine Bandbreite beschnitten werden muss damit die anderen Cores mit angebunden werden können (Beispiel Lanes Teilung PCI-E mit 2 GPUs/USB3 etc.). Durch weniger Fläche= höherer Wärmestau=niedrigerer Takt. Durch Bandbreiten splitting= langsamerer Cache oder Austausch zwischen den Cores/Ringbus usw.

Also ich glaube eher nicht, dass Intel die Fläche der großen Kerne beschnitten hat um noch die kleinen unterbringen zu können, immerhin werden die CPU ja in 10nmSF gefertigt, womit grob doppelt so viele Transistoren auf die gleiche Fläche wie bei 14nm passen sollten und da gab es auch schon 10 Kerner. Naütrlich werden die neuen großen Kerne mehr Transistoren haben, aber 8 große und 8 kleine sollten unter den HS passen, zumal der Sockel ja wohl auch größer geworden ist.

Wo welche Bandbreite beschnitten werden könnte/sollte, sehe ich nicht mit PCIe hat das auch nichts zu tun. Wenn ein Ringbus nicht reicht, wird Intel eben einen doppelten Ringbus nehmen oder vielleicht auch Mesh, welches Intel gegenüber der ersten Anwendung in Skylake-SP sicher auch weiterentwickelt hat.

Unterm Strich bleibt die Frage (es wird keiner von uns beantworten können) ob Adler Lake ohne die little Cores bei gleichem Strombedarf in Spielen nicht mehr Performance hätte wie mit den little Cores....

Letztendes wird man es nicht 100%ig wissen, aber vermutlich kann man sich der Antwort nähren, indem man die little Cores deaktiviert, sofern das im BIOS machbar sein wird und dann mal vergleicht. Ich könnte mir aber sogar vorstellen, dass die Leistungsaufnahme in Spielen dann bei gleicher Leistung sogar höher ausfallen könnte, eben weil dann alle SW Threads auf den großen Kernen laufen müssen und ggf. ist sogar die Leistung schlchter, weil der maximale Takt des Kerns auf dem der zentrale Thread des Spiels läuft, deswegen geringer sein muss.

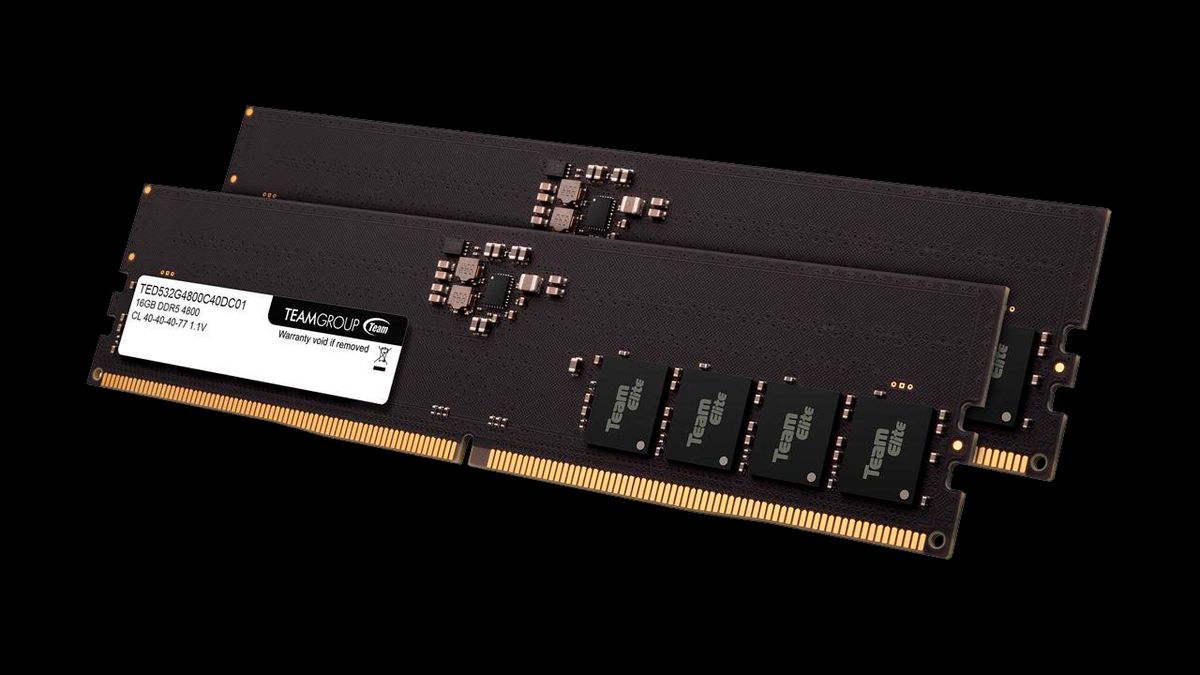

Für 32 GB DDR5-4800 sind Preise von 399$ angekündigt

Grab some RAM for next-gen platforms that aren't out yet.

www.tomshardware.com

Aber klar wird DDR5 RAM anfangs teurer sein, reche mit 50% Aufpreis der dann mit der Zeit fallen wird und auch Alderlake könnte anfangs sehr gefragt sein und wenn die Nachfrage das Angebot übersteigt, schlagen die Händler immer ordentlich was drauf, wie wir ja schon oft genug und nicht nur bei Intel CPUs gesehen haben.

Die Cores massiv verbreitern und vertiefen, die IPC dadurch um 50% steigern und Takt um ⅓ absenken.

Klar kann man mehr Transistoren aufwenden und mehr IPC zu gewinnen, muss man ja auch und für 50% mehr IPC braucht man auch mehr, meist deutlich mehr als 50% mehr Transistoren. Diese brauchen Platz und Energie, weshalb man es normalerweise mit einem Shrink der Fertigungsstruktur verbindet, sonst müsste man viel größere Sockel verwenden um den nötigen Platz zu haben oder mit weniger Kernen auskommen, was bei aktuellen Krieg der Kerne wohl weder AMD noch Intel tun werden.

Nein, 1/3 weniger Takt, wären z.B. 2 statt 3 GHz und bei 50% mehr IPC, hätte man dann wieder die Leistung wie bei 3GHz, 2*1,5 = 3!

Apple Lightning Core, TSMC N7P, 2,66GHz, 52,8 Punkte, 11 kJ

Wurden diese 11kJ wirklich in dem Benchmark gemessen in dem die 52,8 Punkte ermittelt wurden oder hat mal wieder jemand die TDP mit der tatsächlichen Leistungsaufnahme gleichgesetzt, als ob die CPUs beim Boosten nicht deutlich mehr Leistungsaufnahme haben als ihre TDP und dies mal der Zeit genommen? Man sollte da immer genau hinschauen und natürlich läuft ein Tiger Lake bei 4,8GHz in einem Bereich der weit oberhalb des Taktes mit der maximalen Effizienz liegt.