w0mbat

Enthusiast

Thread Starter

- Mitglied seit

- 12.02.2006

- Beiträge

- 7.108

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 5800X3D

- Mainboard

- MSI MAG B550M Mortar Max WIFI

- Kühler

- NZXT Kraken X63

- Speicher

- G.SKILL F4-3600C17D-32GTZR

- Grafikprozessor

- XFX Speedster QICK 319 Radeon RX 6800 BLACK

- Display

- LG 34UC79G-B

- SSD

- 2TB WD_BLACK SN850X | 2TB Samsung 970 EVO Plus

- Soundkarte

- Realtek ALC1220

- Gehäuse

- Lian Li O11 Dynamic Mini

- Netzteil

- Corsair SF750 Platinum

- Keyboard

- CM QuickFire Rapid-i

- Mouse

- Logitech G Pro X Superlight 2

- Betriebssystem

- Windows 11 Pro x64

- Webbrowser

- Firefox

- Sonstiges

- Sennheiser PC37X

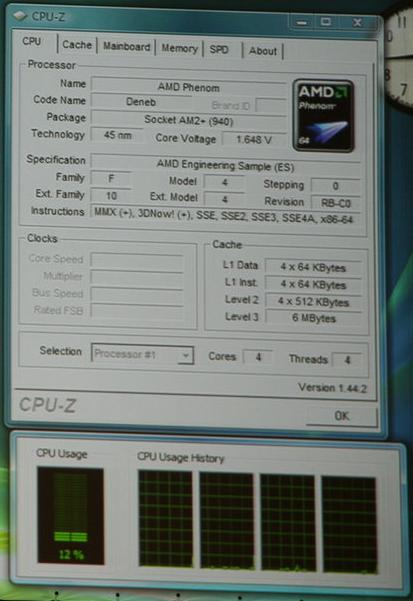

AMD 45nm K10.5 "Shanghai"-Generation

Laut AMD wurden heute die ersten Samples der in 45nm gefertigten und verbesserten K10 CPU an die Partner ausgeliefert. Die 45nm CPUs der "Shanghai"-Generation sollen im 2. Halbjahr 2008 die aktuellen CPUs der "Barcelona"-Generation ablösen. Doch die auch K10.5 genannte CPU ist kein einfacher Die-Shrink von 65nm auf 45nm, AMD hat an der K10-Architektur noch weiter gefeilt und will so eine bessere Pro-MHz-Performance, höhere Taktraten & eine geringeres TDP unter eine Haube bringen.

45nm K10.5 Die-Shot:

Die 45nm CPUs werden in verschiedenen Versionen für Server & Desktop erscheinen, basieren aber alle auf der gleichen Architektur.

Server: Shanghai - Quad-core - 6MB L3 Cache - 95W TDP - Q3-Q4 2008

Desktop:

Deneb(FX) - Quad-core - 6MB L3 Cache - 95W TDP - Q3-Q4 2008

Propus - Quad-core - kein L3 Chace - 95W TDP - Q3-Q4 2008

Heka - Triple-core - kein/6MB L3 Cache - ? TDP - Q1 2009

Regor - Dual-core - kein/6MB L3 Cache - ? TDP - Q1 2009

Anscheinend sind auch CPUs auf der Shanghaibasis mit bis zu 12 Cores in Planung: AMD: Prozessoren mit sechs und zwölf Kernen

65nm K10 -> 45nm K10.5

Am auffälligsten ist natürlich die Verkleinerung der Fertigungsgröße von 65nm auf 45nm. Dadurch wie die Die-Size kleiner und die CPU energieeffizienter - höherer Takt bei gleichem TDP oder niedrigeres TDP bei gleichem Takt. Auch hat AMD bei den Modellen die einen L3 Cache enthalten dessen Kapazität vergrößer. Waren im "Barcelona" noch 2MB L3 Cache enthalten, hält der "Shanghai" die 3x Menge, also 6MB, bereit. Es wurden auch weitere Verbesserungen und Bugfixes durchgeführt, diese sind aber bisher noch nicht bekannt - laut den ersten Performancehochrechnungen soll der K10.5 aber ganze 15-30% schneller sein als der orginal K10.

AMD hat auf der Cebit schon laufende System mit 45nm K10.5 CPUs vorgeführt, es scheint also alles nach Plan zu laufen.

Links:

Cebit 2008: AMD mit finalem 45-Nanometer-Wafer für Phenom

Cebit 2008: AMD zeigt ersten 45-Nanometer-Prozessor live

Der Thread wird von mir aktualisiert, sobald neue Infos vorhanden sind

Zuletzt bearbeitet: