Hmm, so richtig blicke ich da noch nicht durch.

Wenn das stimmt, ist doch alles klar:

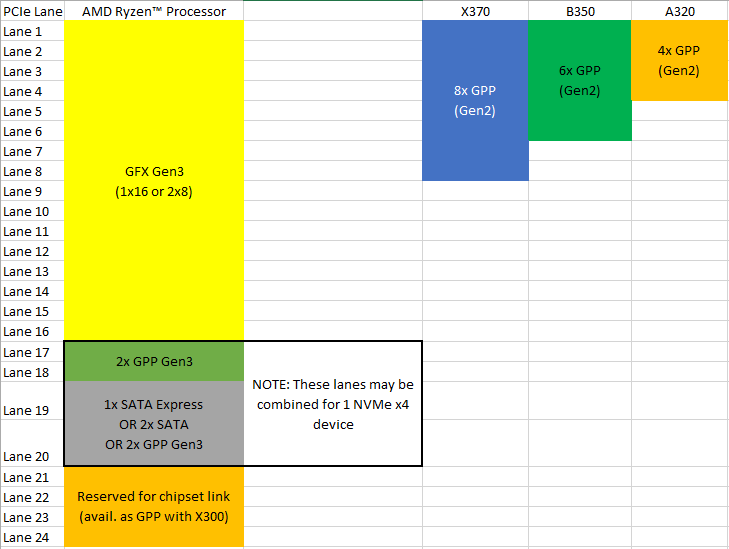

Der Chipsatz selbst hat nur PCIe 2.0 lanes, wenn man daran eine PCIe SSD hängen will, wird sie nur mit PCIe 2.0 Lanes laufen und damit werden die schnellsten PCIe SSDs wie die Samsung 960er eben zumindest Lesend deutlich, schreibend etwas eingebremst, denn mehr als so 1600 bis 1800MB/s (je nach Benchmark) gehen über PCIe 2.0 x4 oder auch PCIe 3.0 x2 netto nicht rüber.

Mein Plan war 2Stk. m.2-SSD`s im Raid direkt an die CPU anzubinden.

Meinst Du M.2 SATA oder M.2 PCIe SSDs? Zwei SATA SSD wären kein Problem, egal ob im M.2 oder im 2.5" Formfaktor, aber wenn es zwei M.2 PCIe SSDs sein sollen, wären nur je zwei PCIe 3.0 Lanes von der CPU möglich, damit also nicht die volle Leseperformance schneller PCIe SSDs und im RAID gehen PCIe SSDs bei der Plttform wohl auch nur als SW-RAID, wobei Windows dann davon nicht booten kann und Windows-SW RAIDs sind auch nicht besonderes performant. Bei Intel geht das RAID über PCIe SSDs auch nur an bestimmten PCIe Lanes der S. 1151 Chipsätze und nur mit dem Intel RST Treiber, weil man dafür einen besonderen Trick angewendet hat.

Dazu noch eine Grafikkarte. Über das Board sollten dann noch eine oder zwei SATA-SSD`s angeschlossen werden. USB 3.1, SATAe oder ne extra Soundkarte brauche ich nicht. Ist das nun über die Ryzen-Plattform realisierbar?

Das hängt vom jeweiligen Board ab, aber wenn Du M.2 PCIe SSDs meinst und keine vollständige Anbindung beider SSD (wozu überhaupt zwei und nicht lieber gleich eine große?) mit je 4 PCIe 3.0 Lanes erwartest, sollte es gehen.

Ich glaub das USB Konsortium selbst hat doch USB 3.0 in USB 3.1 Gen1 umgetauft? Bzw. als zweiten Namen eingeführt?

So hat man doch wenigstens eine große Verbreitung von USB 3.1 erreicht, denn welche wirklich massentaugliche Anwendung gibt es für USB 3.1 Gen 2 mit seinen 10Gb/s überhaupt? Für HDDs werden die 5Gb/s noch lange locker reichen, die schnellsten 3.5" Platten kommen nicht einmal auf den äußeren Spuren auf 250MB/s, auf den inneren sind es nur die Hälfte, selbst zwei HDDs im RAID 0 brauchen also kaum mehr als 5Gb/s und UASP. Mit UASP werden auch SATA SSDs nur um 50 bis maximal 100MB/s gebremst, nur ein RAID 0 aus zwei SSDs kann also wirklich von den 10Gb/s profitieren und PCIe SSDs kann man nicht über USB betreiben, dazu fehlt es schon schlicht an einem USB auf PCIe Bridgechip und da Thunderbolt sowieso viel schneller ist (TB hat 40Gb/s) und schon auf PCIe basiert, wird es so einen Chip wohl auch kaum geben.

Wie wird hier zB. die Netzwerkschnittstelle realisiert? Über den USB, oder kommt da dann einfach ein zusätzlicher Controller auf das Brett?

Das bleibt dem Boardhersteller überlassen.

Wäre es für den Boardhersteller dann auch möglich zwei der PCIe Lanes, die für USB 3.0 gedacht sind, an einem USB 3.1 Gen2 Controller zu nutzen?

Solche PCIe Lanes gibt es bei AMD nicht, aber die PCIe Lanes zur Anbindung des Chipsatzes sind ja GPP, also ebenso universell verwendbar wie die andere 4 die im Bild darüber eingezeichnet sind, wenn auch nur beim X300, sonst hängt ja der Chipsatz dran.

Ich denke mal letzteres geht nicht, bei erstem werden wohl die 4 freiwerden PCIe Lanes für Controller genutzt. Eine für GBE, eine für Audio und vlt. 2 für USB 3.1 Gen2.

Wobei sich dann die Frage stellt, ob der Boardhersteller überhaupt etwas spart wenn es die Funktionen mit einzelnen Controllern statt einem richtigen Chipsatz realisiert.

Wenn man 2 USB 3.0 Lanes zu einer 3.1 Gen2 zusammenschalten könnte wäre das natürlich optimal, aber ob das so einfach geht?

Nein, man kann keine USB Ports zusammenfassen, dies geht bei PCIe Lane oder auch bei SAS Ports, aber nicht bei USB oder SATA.

wenn Du NVMe- SSDs meinst, wären mit 16x PCIe 3.0 für die Grafikkarte, 4x für die erste NVMe- SSD und noch 4x für die zweite NVMe- SSD alle Lanes besetzt.

Wobei das bei keinem Board so verschaltet sein dürfte, denn erstens geht das nur beim X300 und zweitens hat man dann keine Lane mehr um noch irendwas anderes wie z.B. den Netzwerkchip anzubinden. Zwei SSDs mit je PCIe 3.0 x4 anzubinden ohne der Graka Lanes zu nehmen, wird bei RYZEN nicht gehen, da die PCIe Lanes der Chipsätze eben nur PCIe 2.0 Lanes sind und die Chipsätze selbst eben keine PCIe 3.0 Lanes haben, sofern die Graphik oben korrekt ist.

Wenn Du also alles gleichzeitig voll auslasten würdest, würde zum Beispiel das Netzterk, wenn es auch über den x4- Chipsatz kommunizieren muss, die Geschwindigkeit reduzieren. (Theoretisch)

Die Netzwerkchips dürften sicher nur an den PCIe Lanes des Chipsatzes hängen, aber man kann dessen Anbindung mit einer SSD dann gar nicht voll auslasten, weil die ja wohl PCIe 3.0 x4 ist und selbst der X370 nur 8 PCIe 2.0 Lanes bietet. Eine PCie 3.0 x4 SSD kann daran nicht die ganzen Bandbreite der Anbindung auslasten, sondern nur Hälfte davon und wenn man nun noch eine zweiten an die anderen 4 PCIe 2.0 Lanes hängt, wo hängt dann der Netzwerkchip dran? Da kaum eine Mainboardhersteller den Netzwerkchip über USB anbinden dürfte, hätte der andere (M.2) Slot dann wohl nur 2 PCIe 2.0 Lanes und damit ließe sich dann mit den SSD alleine die Bandbreite der Anbindung nicht auslasten.

Wobei ich aber ehrlich gesagt skeptisch bin ob der Chipsatz wirklich mit PCIe 3.0 x4 angebunden sein wird, denn auch wenn die CPU da 4 PCIe 3.0 Lanes bietet, sollte es mich wundern wenn der Chipsatz diese auch mit PCIe 3.0 Geschwindigkeit betreibt und dann selbst seine Lanes aber nur mit PCIe 2.0 Speed. Viel wahrscheinlicher dürfte es sein, dass die Lanes zu Anbindung des Chipsatzes dann nur mit 5Gb/s (PCIe 2.0) laufen, wenn da wirklich ein Chipsatz dran hängt und der ganze Chipsatz überhaupt kein PCIe 3.0 hat, auch zur Anbindung nicht. Aber das wird man sehen, wenn die gesamt Bandbreite des I/Os des Chipsatz in eine Richtung dann bei so 1600 bis 1800MB/s limitiert ist, dann lag ich mit der Vermutung richtig. Schafft er doch mehr pro Richtung, dann frage ich mich allerdings, warum dann dessen Lanes nur PCIe 2.0 Lanes sind, wenn er wirklich intern auch PCIe 3.0 hat.

Andererseits dürfte dies den allermeisten Usern total egal sein, denn die wollen eine oder maximal 2 Grakas, allenfalls eine schnelle PCIe SSD und dann noch eine oder zwei HDDs und vielleicht ein optisches Laufwerk betreiben. Dazu ein Gigabit Ethernet oder maximal 2 und ein paar USB Ports und dafür reicht das I/O der Plattform locker aus und wenn dann die PCIe SSD mit PCIe 3.0 x4 Anbindung populärer geworden sind und praktisch keinen Aufpreis gegenüber SATA SSD mehr kosten und vielleicht im nächsten Jahr PCIe 4.0 kommt, gibt es eben die AM4+ Plattform.

Trotzdem ist das Szenario eher nur in der Theorie relevant, weil erstens die aktuellen NVMe- SSDs zum schreiben nur ca. 2x brauchen

Geizhals listet 7 SSDs deren Schreibraten mit 2000MB/s und mehr angegeben sind, zumindest die Samsung 960 Pro schaffen diese Werte ohne Tricks wie Datenkompression bei den Phison auch wirklich, über 2 PCIe 3.0 Lanes gehen nur so 1600MB/s bis bestenfalls 1800MB/s. Das reicht nicht einmal um mit voller Geschwindigkeit in den Pseudo-SLC Cache einer größeren 960 Evo zu schreiben.

Beim Lesen von beiden SSDs würden 7 Gigabyte pro Sekunde anfallen - auch das müsste so schnell ja irgendwohin, und das geht aktuell nicht.

Daten werden ja nicht nur kopiert und gerade so eine schnelle CPU wie es die 8 Kerner RYZEN zu sein versprechen, sollte bei der passenden Anwendung auch schon einen größeren Datenstrom verarbeiten können, allerdings gibt es aus den oben genannten Gründen mit Sicherheit keine 7Gb/s, weil dafür einfach die 8 nötigen PCIe 3.0 Lanes fehlen, außer beim X300, aber bei dem hätte mnn sonst keine PCIe Lanes für andere Zwecke wie Netzwerk oder auch nur einen SATA Port für ein Bootlaufwerk übrig.

Ein zusätzlicher Controller ist nötig, weil die CPU leider kein Ethernet integriert hat(eigentlich verwunderlich für ein SoC, aber AMD produziert keine Netzwerkkarten)

Sag lieber ASMedia, von denen stammt die Technologie der AM4 Chipsätze ja.

SATA und NVMe sind als Protokoll über PCIe schon länger im Einsatz

SATA ist eine Schnittstelle und kein Protokoll, üblicherweise verwenden SATA HDDs und SATA SSDs AHCI als Protokoll.

Die CPU hat 16 + 4 + 4 PCIe 3.0- Lanes UND zusätzlich dazu noch 4 USB 3.0- Schnittstellen, die bereits als USB 3.0 so aus der CPU rauskommen.

Wobei aber eben 4 der PCIe Lanes für die Anbindung des Chipsatzes sind, sofern nicht die Option X300 genutzt wird.

d.h. um USB3.1 Gen2 zu realisieren, bleiben (wenn überhaupt möglich) nur die 4 Lanes, welche durch das weglassen des Chipsatzes frei werden?

Genau und mindestens eine weitere von den Lanes dürften die Boardhersteller für das Netzwerk verwenden.

Haben da die Mainboardhersteller eigentlich freie Wahl, wie die freien Lanes genutzt werden, oder wird das von AMD vorgegeben?

Ja, da es alles GPP, also General Purpose Lanes sind. Die einzige Limitierung dürfte sein, dass diese 8 Lanes nicht als x8 zusammengefasst werden können, so wie die ganze PCIe Lanes der S. 1151 Chipsätze auch maximal zu x4 kombiniert werden können und dies eben auch nicht wahlfrei, sondern nur jeweils 4 bestimmte Lanes können als x4 arbeiten.

SATA Express allerdings hätte man sich wirklich schenken können, so tot wie das ist...

Das zeigt wie alt die Chipsätze im Grunde sind, als die geplant und konzipiert wurden, war es wohl noch nicht abzusehen, wie schnell die Entwicklung hin zu PCIe 3.0 x4 Anbindung gehen würde. Aber immerhin kann man ja eine PCIe SSD mit 4 PCIe 3.0 anbinden, wen auch unter Verlust der beiden SATA Ports der CPU. Den meisten dürfte dies auch genügen.

Zudem dürfte es sehr interessant werden, wie welcher Boardhersteller welche Kombination ermöglicht oder eben nicht.

Ja, einige Board scheinen nach den ersten Informationen ja sehr viele PCIe und M.2 Slots zu bieten.

Da dürfte der AMD Interessent höllisch aufpassen, welches Line-Sharing zum Tragen kommt

Das auf jeden Fall, aber dies ist bei Intel Board spätestens seit Skylake auch nicht viel anderes. Es empfiehlt sich in jedem Fall vor dem Kauf das Handbuch des Boards zu lesen um zu sehen ob die gewünschte Kombination auch wirklich möglich ist oder die Resourcen nicht etwas geteilt werden und dann nur entweder oder geht.

AMd hat immer vollmundig von Quadchannel geschwafelt, man hat aber immer nur 2xDualChannel bekommen und so lahm war den Speicherzugriff dann auch immer.

Bei einem Server ist das nicht so kritisch, den dort müssen die viele Kerne meist auf unterschiedliche Speicherbereich zugreifen und das können sie bei mehreren unabhängigen Speichercontrollern unter Umständen besser als wenn ein einziges und dafür sehr breites Speicherinterface vorhanden ist, welches zwar jeweils mehr Daten mit einem Zugriff holt, aber wo sich alle Kerne dann ständig gegenseitig ausbremsen weil nur ein Zugriff zur Zeit möglich ist und die anderen eben warten müssen bis sie dran sind. Was besser ist, hängt aber sehr von der Nutzung ab und die ist bei Servern eben meist anderes als bei Heimanwendern.

Bulldozer lässt grüßen...

Bulldozer lässt grüßen...