unl34shed

Enthusiast

Ist er doch aber nicht.

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: this_feature_currently_requires_accessing_site_using_safari

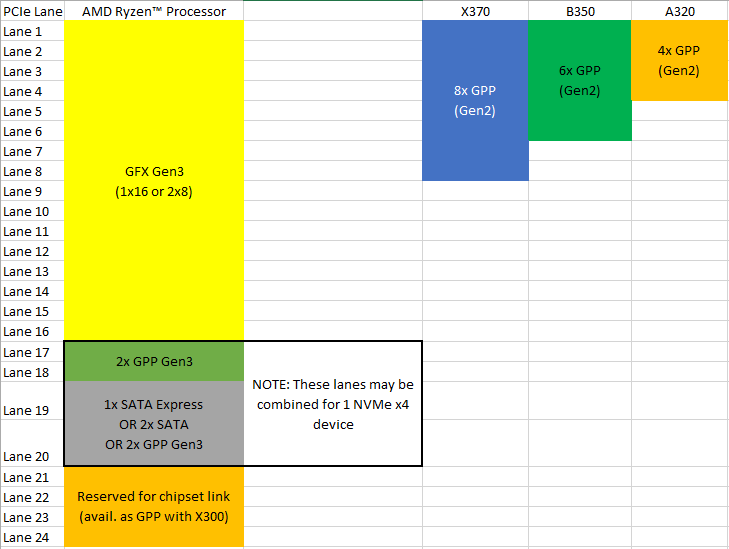

Laut der Grafik dieses Artikels, reichen die Chipsätze aber neben den 8 PCIe 2.0- Lanes auch vier PCIe 3.0 Lanes durch, wenn man auf SATAe verzichtet, was man natürlich mit zwei NVMe- SSDs in der Regel nicht bräuchte.Zwei SSDs mit je PCIe 3.0 x4 anzubinden ohne der Graka Lanes zu nehmen, wird bei RYZEN nicht gehen, da die PCIe Lanes der Chipsätze eben nur PCIe 2.0 Lanes sind und die Chipsätze selbst eben keine PCIe 3.0 Lanes haben, sofern die Graphik oben korrekt ist.

Die Grafik dieses Artikels hat ein User des Anandtech Forums aufgrund der Informationen erstellt und dabei eben offenbar unterstellt, dass die Fußnote bzw. PCIe 3.0 stimmt und die SATA Express Ports zusätzliche SATA Ports und PCIe Lanes bedeuten...

...Nur sollte sich keine zu sehr enttäusch fühlen, wenn es am Ende so ist wie ich es befürchte und der ganze Chipsatz nur mit PCIe 2.0 läuft und auch gar keine zusätzlichen PCIe 3.0 Lanes hat, sondern die SATA Express Ports eben mit den vorhandenen SATA Ports und bis zu 8 PCIe 2.0 Lanes gebildet werden...

Wobei ich aber ehrlich gesagt skeptisch bin ob der Chipsatz wirklich mit PCIe 3.0 x4 angebunden sein wird, denn auch wenn die CPU da 4 PCIe 3.0 Lanes bietet, sollte es mich wundern wenn der Chipsatz diese auch mit PCIe 3.0 Geschwindigkeit betreibt und dann selbst seine Lanes aber nur mit PCIe 2.0 Speed. Viel wahrscheinlicher dürfte es sein, dass die Lanes zu Anbindung des Chipsatzes dann nur mit 5Gb/s (PCIe 2.0) laufen, wenn da wirklich ein Chipsatz dran hängt und der ganze Chipsatz überhaupt kein PCIe 3.0 hat, auch zur Anbindung nicht.

Die Fußnote passt perfekt zu den 4 PCIe 3.0 Lanes und den beiden SATA Ports die die CPU direkt bietet, nur passt es eben nicht wirklich gut zum Chipsatz, wo es sonst nur PCIe 2.0 Lanes gibt. Das wäre nicht das erst mal, dass durch Copy&Paste ein Fehler in einer Präsentation oder auch Dokumentation landet.Dazu die Fußnote der Sata kann auch als PCIe3.0 genutzt werden -> entweder SATAe oder PCIe3.0 4x

Welche Bilder meist Du? Din um die es in der News geht, sind doch von einem User aufgrund der Dokumentation erstellt und kommen eben nicht von AMD.Und das stimmt so auch mit dem Bild mehr oder weniger überein.

Dies ist das Bild welche angeblich von AMD ist:Doch, das hier sagte AMD der Presse bzw. wurde es so Golem von AMD gegeben: https://abload.de/img/pcielanes1p6kjz.png

Das ist es doch überhaupt nicht, alle H97 und Z97er Boards mit SATA Express haben nur PCIe 2.0 Lanes und damit 10Gb/s für den SATA Express Port und auch deren M.2 Slots sind fast immer nur genau so mit 10Gb/s angebunden. Eine der ganz wenigen Ausnahmen ist mein ASRock Z97 Extreme 6, denn das hat neben einem SATA Express Port mit PCIe 2.0 x2 + SATA und einem M.2 Slot mit PCIe 2.0 x2 + SATA noch einen M.2 Slot mit 4 PCIe 3.0 Lanes der CPU (ohne SATA). PCIe 3.0 ist also überhaupt nicht nötig, auch wenn man die PCIe Anbindung mit den nur 10Gb/s von PCIe 2.0 x2 natürlich praktisch in der Pfeife rauchen kann, weil damit gerade mal so 200MB/s mehr als über SATA 6Gb/s gehen.Nur doof, dass zu SATAe zwingen PCIe3.0 Notwendig ist

Welche Folien von AMD? Die in dieser News sind nicht von AMD und das steht so auch klar in der News!UND es auch genau so auf AMDs Folien steht.

Die CPU stellt 4 PCIe 3.0 Lanes für die Anbindung des Chipsatzes, darüber sind wie uns einig, aber mein Zweifel ist eben ob der Chipsatz selbst überhaupt PCIe 3.0 beherrscht, denn erstens hat er ja selbst nur PCIe 2.0 Lanes, was unlogisch ist wenn er eigentlich intern PCIe 3.0 hat (intern sind das ja eigentlich PCIe Lanes Switches bei denen einige Controller wie Netzwerk, USB und SATA integriert sind) und zweitens hat der Techniklieferant ASMedia zwar PCIe Switches, aber keine für PCIe sondern nur für PCIe 2.0 und einzig die USB 3.1 Host Controller können wahlweise mit einer PCIe 3.0 oder zwei PCIe 2.0 Lanes angebundnen werden, selbst deren neuster SATA 6Gb/s Host Controller ASM1062(R) hat nur PCIe 2.0 x2 aber nicht die Option auf PCIe 3.0 x1.Und wie kommst du jetzt auch noch darauf, dass der Chipsatz mit PCIe 2.0 angebunden sein soll?