Hast du da eine Anleitung parat oder muss man einfach beim DDR3 Pinout alles abkleben was nicht Spannungsversorgung oder SPD ist?

Bei DDR3 kenne ich das Pinout nicht. Bei DDR1 und 2 wurde einfach alles bis auf 8 pins an einem Ende abgeklebt.

@Felix the Cat (auch als Select bekannt) hatte mal was im Eiskaltmacher dazu gepostet:

Neues Spd auf Ram flashen - SPD-Tool *HowTo*

eiskaltmacher.de

Wäre das denn eine Möglichkeit Defekte an den Chips zu umgehen und den RAM mit halber Kapazität weiterhin zu nutzen?

Ja,

aber...

Mir sind theoretisch mehrere Möglichkeiten bekannt, wie man das regeln kann:

Erstens kann man bei einem Dual Rank Riegel den oberen Rank abschalten (das klappt definitiv). Und zweitens müsste man die Kapazität pro Rank halbieren können, also pro Chip nur noch die Hälfte ansprechen (das habe ich nicht getestet, "sollte" aber klappen). Drittens lässt sich vielleicht die Zahl der Bänke im Chip reduzieren - keine Ahnung ob das klappt.

Kurze Erklärung dazu... Bei normalem unbuffered DDR Ram sind die Ranks parallel an die Daten- und Adressleitungen gehangen. und es wird eine einzelne Leitung genutzt, um quasi "umzuschalten". Konfiguriert man nun einen Dual Rank Riegel im SPD als Single Rank, dann schaltet der IMC in Chipsatz oder Cpu nicht mehr auf den zweiten Rank um. Damit wird allerdings immer der erste Rank genutzt und nie der zweite. Ist der defekte Chip also im ersten/unteren Rank, hat man keine Chance. Man kann problemlos z.B. aus einem 512mb TCCD Stick einen mit 256mb machen. Habe ich schon selbst getan.

Bei der anderen Variante muss man wissen wie die Daten innerhalb eines Chips ausgewählt werden. Vereinfacht gesagt ist Ram wie eine Exceltabelle. Man hat Zeilen (Rows) und Spalten (Columns). Um eine Menge an Speicherzellen ansprechen zu können braucht man eine gewisse Menge an Zeilen und Spalten. Da im PC alles binär ist, hat man grob (bis zu) 15 bits pro Row und Column. Ändert man das im SPD ab, also reduziert z.B. die Rows um ein Bit, dann sollte sich die Kapazität halbieren. Allerdings wird hier dann die Hälfte pro Chip genutzt, nicht die Hälfte der Chips. An der Stelle bin ich mir wie erwähnt nicht sicher bzw. habe es nicht getestet.

Eine weitere Variante (Achtung, jetzt könnte Halbwissen folgen), die mir noch in den Sinn kommt wäre das Reduzieren der Bänke (Banks, nicht Ranks) des Rams. Zwischen der Organisation via Zeilen und Spalten (Rows und Columns) gibt es pro Chip noch Bänke - um beim Excel Vergleich zu bleiben - das sind innerhalb des Excel Dokuments zusätzliche Tabellenblätter. Normalerweise sind das bei DDR1 vier Stück. Ob man die allerdings ändern kann und ob das klappt, da bin ich überfragt.

Ram ist ja "dumm" und wird komplett getaktet/gesteuert, sprich man muss dem IMC nur schmackhaft machen was man haben will und es funktioniert meist ganz gut...

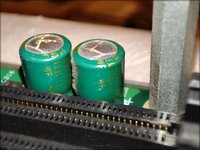

Generell hat man den Vorteil, das man das SPD auch bei einem zerflashten Stick "retten" kann, indem man alle Pins abklebt, mit einem intakten Riegel bootet und alles ist danach wieder fein. Außerdem kann man den Riegel flashen und direkt das SPD via Taiphoon Burner oder SPD Tool erneut einlesen. Meist sieht man am Ergebnis schon ob das was man getan hat grob hinkommen kann.

Und noch ein Bild dazu, gemopst aus einem wirklich guten Anandtech Artikel:

Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

www.anandtech.com

Deinen Beitrag hatte ich irgendwann mal via Google Suche gefunden und im Hinterkopf behalten, weil er extrem nützlich war.

Deinen Beitrag hatte ich irgendwann mal via Google Suche gefunden und im Hinterkopf behalten, weil er extrem nützlich war.

.

.