Operation.Void

Profi

I found 1.33V unstable in my case, and had to bring it back to 1.34V and it's been weeks without issue. I also decided I wanted to test CAS vs FCLK. I ran 3733CL18 and 3666CL17 through the Rainbow Six Siege benchmark at 360p on low settings with my 3500X and got the exact same results. I give the win to FCLK because it also helps multithreaded workloads which do not care about RAM.

Update: I have further reduced some timings! It never stops ...

I reduced tFAW from 28 to 27, tRRD_L from 6 to 5 and tRCDWR from 19 to 18.

Update 2: For further proof of stability I have ran HCI Memtest for 100% on each thread, not a long test but eh the real test is proper usage rather than wasting too much time stability testing the OC.

Update 3: I tested overnight with TM5 for 5 hours or 20 cycles with no WHEA errors!

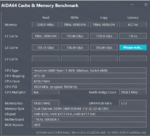

Update 4! Shrunk the previous images as far as they could go to declutter this message. I have further tightened timings, going from tRAS 39 to 36 and getting all my WRWR and RDRD (except SCL) to 1. I suppose having only 2 DIMM slots helps with this.This screenshot here is of 50 minutes of TM5 Anta777 heavy5opt, though I have done more testing on the exact timings. 20 minutes but I was using the computer and as a result TM5 decided to stop due to lack of allocated RAM and never came back, and another hour previously in which I forgot to take a screenshot. So did 18 minutes of HCI. Cumulative 2.5 hours. All with no WHEA errors either. Tested overnight for 6h38m (25 cycles) and got no errors. Raised tRFC to 584, because I don't wan to be on the edge. None of my timings go any lower, none. Technically tRAS does, but lowering it further than 36 yields no gain and trying 32 actually scored worse on AIDA64 latency test.

I also broke the 70 nanosecond barrier with this at 3955MHz on the CPU.

Update: I have further reduced some timings! It never stops ...

I reduced tFAW from 28 to 27, tRRD_L from 6 to 5 and tRCDWR from 19 to 18.

Update 2: For further proof of stability I have ran HCI Memtest for 100% on each thread, not a long test but eh the real test is proper usage rather than wasting too much time stability testing the OC.

Update 3: I tested overnight with TM5 for 5 hours or 20 cycles with no WHEA errors!

Update 4! Shrunk the previous images as far as they could go to declutter this message. I have further tightened timings, going from tRAS 39 to 36 and getting all my WRWR and RDRD (except SCL) to 1. I suppose having only 2 DIMM slots helps with this.

I also broke the 70 nanosecond barrier with this at 3955MHz on the CPU.

Zuletzt bearbeitet:

the primary timings are pretty much unresponsive to voltage

the primary timings are pretty much unresponsive to voltage