Werbung

NVIDIA nutzte die Keynote der GPU Technology Conference zur Vorstellung der Volta-Architektur. Zusammen mit der ersten Hardware, der Tesla V100, sind auch die ersten technischen Daten bekannt. Allerdings beschränken sich diese ersten Informationen auf die wichtigsten Punkte für eine GPU, gehen aber noch nicht genauer auf die Architektur selbst ein. Eben dies wollen wir nun nachholen.

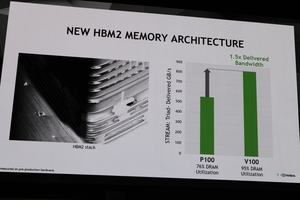

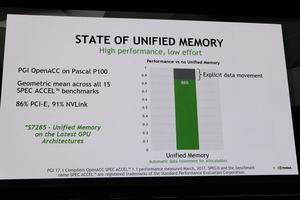

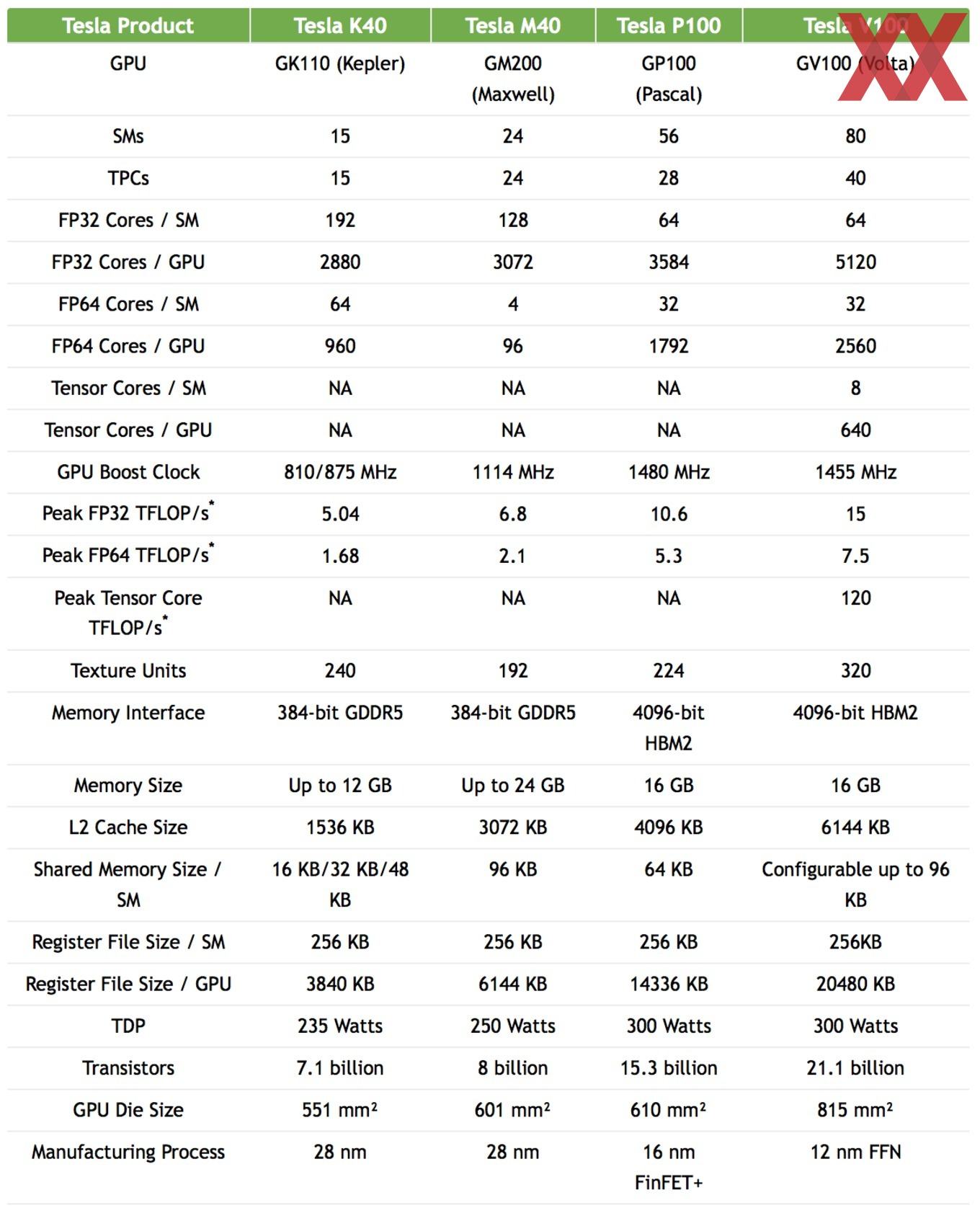

Natürlich ist die GV100-GPU die bisher leistungsstärkste und auch komplexeste GPU, die NVIDIA bisher hat fertigen lassen. Zahlen wie 21 Milliarden Transistoren, 5.120 Shader-Einheiten, 16 GB HBM2 und über 100 Milliarden Datenverbindungen in der GPU, dem Interposer und dem Speicher zeigen dies recht deutlich.

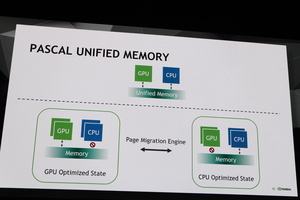

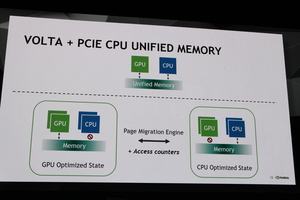

Zugleich ist die Volta-Architektur eine Weiterentwicklung in vielen Bereichen, die man zuletzt vor zwei bis vier Generationen veränderte. Mit der Volta-Architektur richtet sich NVIDIA noch einmal weiter in Richtung des HPC-Bereiches aus – Unklar ist derzeit, in welcher Form die Volta-Architektur für den Desktop erscheinen wird. HBM2 scheint noch immer recht schlecht verfügbar zu sein, so dass der Endkundenmarkt für NVIDIA womöglich keine Option ist. Mit GDDR6 will SK Hynix ab Anfang 2018 aber den bisher schnellsten DDR-Grafikspeicher liefern können – womöglich mit den dazugehörigen GPUs auf Basis der Volta-Architektur.

GV100 GPU Hardware-Architektur

Ähnlich wie viele Vorgänger-Architekturen setzt sich Volta, bzw. die GV100-GPU aus Graphics Processing Clusters (GPCs), Texture Processing Clusters (TPCs), Streaming Multiprocessors (SMs) und einem Speicher-Controller zusammen. Der Vollausbau der GV100-GPU besteht aus sechs GPCs, 84 Volta SMs, 42 TPCs (jeder mit jeweils zwei SMs) und acht 512-Bit-Speicher-Controllern (4.096 Bit ingesamt). Jeder SM hat 64 FP32 Cores, 64 INT32 Cores, 32 FP64 Cores und acht der neuen Tensor Cores. Hinzu kommen noch vier Textur-Einheiten pro SM.

Mit 84 SMs kommt der Vollausbau der GV100-GPU auf 5.376 FP32 Cores, 5.376 INT32 Cores, 2.688 FP64 Cores, 672 Tensor Cores und 336 Textur-Einheiten. An jeden Speicher-Controller angekoppelt sind 768 KB L2-Cache und jeder HBM2-DRAM-Stack wird von zwei Speicher-Controllern angesteuert. In dieser Ausbaustufe bietet die GV100.GPU insgesamt 6.144 KB L2-Cache.

Volta SM (Streaming Multiprocessor)

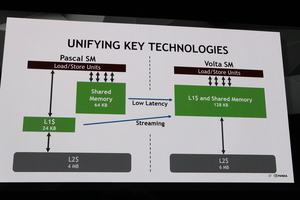

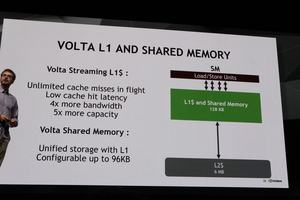

Anders als beim Wechsel von Maxwell zu Pascal gibt es dieses mal auch einige Änderungen innerhalb des Streaming Multiprocessors. Geringe Instructions- und Cache-Latenzen waren Ziel des Umbaus und wurden durch verschiedene Maßnahmen auch erreicht.

Die wichtigsten Neuerungen des Volt SM sind:

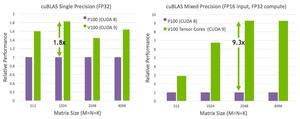

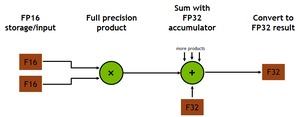

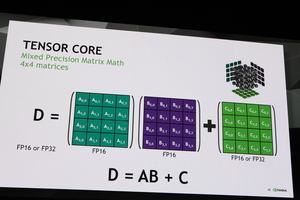

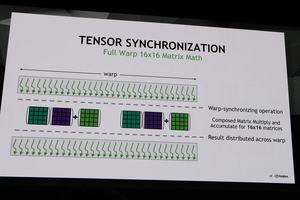

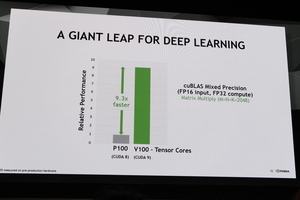

- Mixed-Precision FP16/FP32 Tensor Cores (dazu kommen wir noch einmal etwas genauer)

- verbesserter L1-Data-Cache für geringe Latenzen und höhere Bandbreite

- schlankeres Instruction-Set für ein einfacheres Decoding und reduzierte Latenzen

- höherer Takt und verbesserte Energieeffizienz

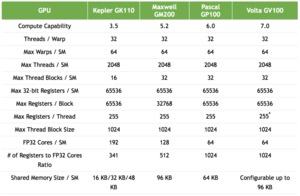

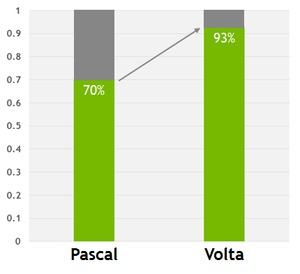

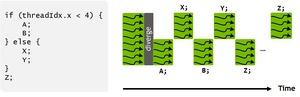

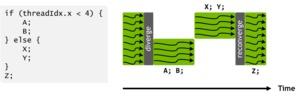

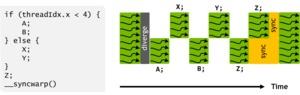

Genau wie bei der GP100-GPU befinden sich im Volta SM 64 FP32 Cores und 32 FP64 Cores. Die Volta-Architektur verwendet allerdings eine neuere Methode zur Partitionierung der zur Verfügung stehenden Cores, was die Auslastung und damit die Leistung insgesamt verbessert. Während die SMs in der GP100-GPU in zwei Processing Blocks mit jeweils 32 FP32 Cores, 16 FP64 Cores, einem Instruction Buffer, einem Warp Scheduler, zwei Dispatch Units und einem 128 KB großen Register File ausgestattet sind, hat sich der Aufbau in der Volta-Architektur etwas geändert.

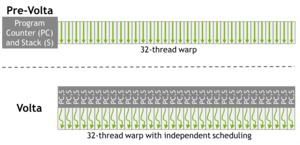

Der SM in der GV100-GPU ist ist in vier Processing Blocks aufgeteilt. Diese wiederum bestehen aus 16 FP32 Cores, 8 FP64 Cores, 16 INT32 Cores, zwei neuen Mixed-Precision Tensor Cores, einem neuen L0 Instruction Cache, einem Warp Scheduler, einer Dispatch Unit und einem 64 KB großen Register File.

Der Register File ist zwischen der Pascal- und Volta-Architektur gleich groß geblieben. Da die GV100-GPU aber über viel mehr SMs verfügt, steigt die Kapazität des gesamten Register Files. Die Größe des Shared Memory wächst auf 96 KB an, während die Pascal-Architektur hier 64 KB vorsah.

Anders als in der Pascal-Architektur, die keine gleichzeitig Ausführung von FP32- und INT32-Instruktionen ermöglichte, kann dies durch die separaten Einheiten im SM der Volta-Architektur ausgeführt werden und erhöht natürlich die Rechenleistung.