Verbesserter Shared Memory und L1-Date-Cache

Werbung

Data-Cache und Shared Memory konnten in der Pascal-Architektur nicht gemeinsam angesprochen und verwendet werden. Mit der Volta-Architektur ändert NVIDIA dies nun und ermöglicht das Zusammenlegen von bis zu 128 KB pro SM. Damit wächst die Größe des Data-Cache um den Faktor sieben im Vergleich zur Pascal-Architektur an. Programm-Code, der keinen Shared Memory verwendet, dafür aber auf einen möglichst großen Data-Cache angewiesen ist, profitiert davon natürlich am deutlichsten.

Die Textur-Einheiten verwenden ebenfalls den Data-Cache und profitieren von dessen maximaler Größe. Die Größe des zusammengelegten Speichers kann angepasst werden. So kann in den insgesamt 128 KB pro SM eine Aufteilung von 64 KB für Textur und Load/Store-Operationen sowie den übrigen 64 KB für Instruktionen vorgenommen werden.

Mit diesem neuen Konzept wollte NVIDIA das beste aus zwei Welten umsetzen. Während der Shared Memory in den Vorgänger-Architekturen zwar eine hohe Bandbreite und geringe Latenzen bot, musste er von den Entwicklern explizit angesprochen werden – inklusive der Problematik der Überprovisionierung. Dies ist mit der Volta-Architektur nicht mehr notwendig.

Über mehrere Anwendungen hinweg hat NVIDIA eigene Messungen vorgenommen und kommt zu dem Ergebnis, dass während Anwendungen unter der Pascal-Architektur bis zu 30 % an Leistung verloren haben, dies mit der Volta-Architektur auf 7 % reduziert werden konnte.

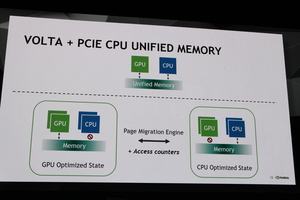

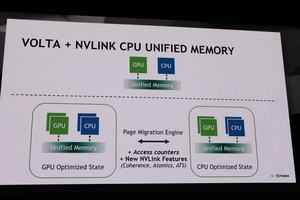

Der Unified Memory hat im Zusammenhang mit NVLink ebenfalls eine Verbesserung erfahren. Bisher war es für einen Prozessor mit PCI-Express-Interface nicht möglich, auf den Unified Memory zuzugreifen, wenn gleichzeitig die GPU darauf Zugriff nahm. Eine sogenannte Page Migration Engine achtete darauf, dass keinerlei Daten von zwei Quellen gleichzeitig bearbeitet werden konnten.

Wird die Tesla V100 mit NVLink zusammen mit einem Prozessor verwendet, der ebenfalls NVLink unterstützt, ist ein gemeinsamer Zugriff nun möglich. Auf die weiteren Verbesserungen mit NVLink 2.0 gehen wir später noch genauer ein.

Tensor Cores

Eine der wichtigsten Neuerungen in der Volta-Architektur bzw. genauer der GV100-GPU sind die Tensor Cores. Von diesen sind in der Ausbaustufe für die Tesla V100 640 Stück vorhanden. Die Implementierung dieser speziellen Recheneinheiten zeigt auch noch einmal schön, wie weit NVIDIA die Volta-Architektur auf die Bedürfnisse des Deep Learning ausgelegt hat.

Mit den Tensor Cores kann NVIDIA die Leistung in den für Deep Learning wichtigen FP32-Berechnungen auf 120 TFLOPS gesteigert. Dies entspricht Faktor 12 der Rechenleistung, die von der GP100-GPU erreicht wurde. Für das ebenfalls wichtige Inferencing spricht NVIDIA von einer um den Faktor sechs höheren Leistung.

Matrix-Multiplikationen (BLAS GEMM) sind der wichtigste Bestandteil für das Training von Deep-Learning-Netzwerken und damit auch für die Tensor Cores in der GV100-GPU. Die Tensor Cores haben innerhalb des SMs ihre eigenen Datenpfade und können per Clock Gating auch komplett abgeschaltet werden, wenn sie nicht benötigt werden.

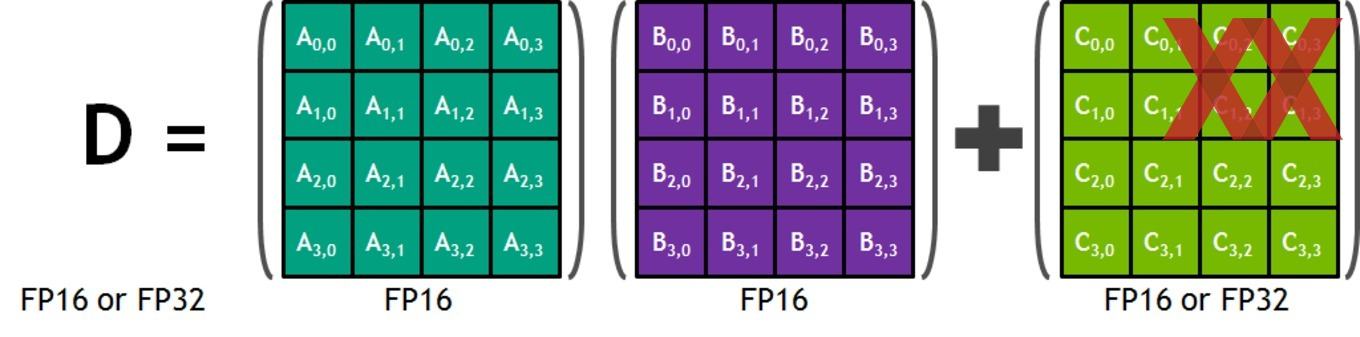

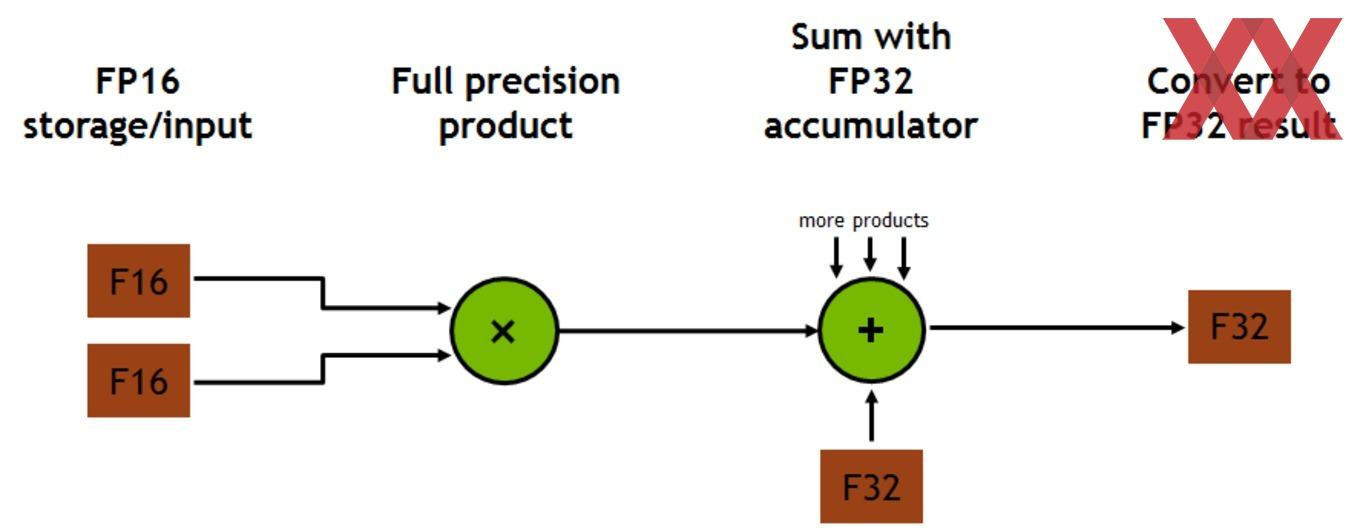

Jeder Tensor Core bietet ein Matrix-Array aus 4 x 4 x 4 Matrizen, welches in einer D = A x B + C Operation durchlaufen wird. Die Eingangs-Matrizen A und B sind dabei FP16-Einheiten, die Akkumulation kann eine FP16 oder FP32-Einheit sein.

Jeder Tensor Core führt 64 Floating Point FMA Mixed-Precision-Operationen pro Takt aus – jeweils eine Multiplikation und eine Akkumulation. Die acht Tensor Cores pro SM kommen damit auf 1.024 Floating-Point-Operationen pro Takt.

Je nach Anwendung kann die Leistung um den Faktor 1,8 bis 9,3 gesteigert werden. NVIDIA vergleicht dazu die Tesla P100 mit CUDA 8 gegen die Tesla V100 mit CUDA 9.

Multi Process Service

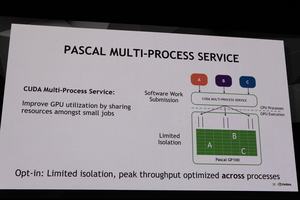

Moderne GPUs sind darauf ausgelegt, dass sie mehrere Prozesse gleichzeitig bearbeiten können. Aus diesem Umstand beziehen sie mit ihren inzwischen mehreren tauend Kernen ihren Vorteil. In der Pascal-Architektur wird den verschiedenen Prozessen eine bestimmte Ressource innerhalb der GPU zugewiesen. Per Timeslice werden die Prozesse dazu in einer bestimmte Reihenfolge gebracht, in der sie dann auch verarbeitet werden.

Der CUDA Multi Process Service soll sicherstellen, dass die Auslastung möglichst hoch ist. Im bisherigen Verfahren konnte es aber dazu kommen, dass sich einige Prozesse bestimmte Ressourcen teilen mussten. Dies kann aber auch zu Inkonsistenzen bei den Berechnungen führen, die natürlich nicht gewünscht sind.

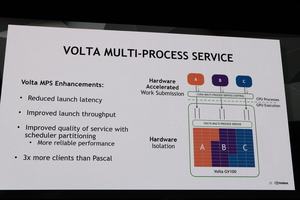

Der Multi Process Service der Volta-Architektur soll zum einen die Zuteilung weiter optimieren, sorgt aber auch für eine Isolation der zur Verfügung gestellten Ressourcen. Damit ist es möglich, dass eine Tesla V100 bis zu 163.840 Threads gleichzeitig bearbeitet – die dreifache Menge, die bei der Tesla P100 möglich war.

Fertigung am Rande des Machbaren

Noch ein paar Worte wollen wir zur Fertigung der GV100-GPU verlieren. Diese ist mit 815 mm² und 21 Milliarden Transistoren gerade so im Bereich des technischen Machbaren und dies stellt ein großes Risiko für ein Unternehmen wie NVIDIA dar. Die Entscheidung, solch einen Chip entwicklen zu wollen, fällt, bevor sicher ist, dass dieser auch in dieser Form gefertigt werden kann. Sicherlich arbeitet NVIDIA mit seinem Fertigungspartner TSMC lange im Vorfeld daran – etwas schiefgehen kann dann aber immer noch.

Aufgrund der engen Zusammenarbeit zwischen NVIDIA und TSMC ist es nicht weiter verwunderlich, dass man sich für den Auftragsfertiger aus Taiwan entschieden hat. Der hier gemeinsam optimierte 12-nm-Prozess ist der aktuell beste zur Verfügung stehende Fertigungsprozess für seinen solchen Prozessor.

Die GV100-GPU wird aber nicht nur aufgrund der hohen Anzahl an Shader-Eineiten so groß. Die Tensore Cores nehmen einen Großteil der Chipfläche ein. Genaue Zahlen wollte NVIDIA nicht nennen, die Tensor Cores sind aber derart komplex aufgebaut, dass sie eben eine nennenswerte Fläche des Chips einnehmen und diesen damit zusätzlich komplexer gestalten.

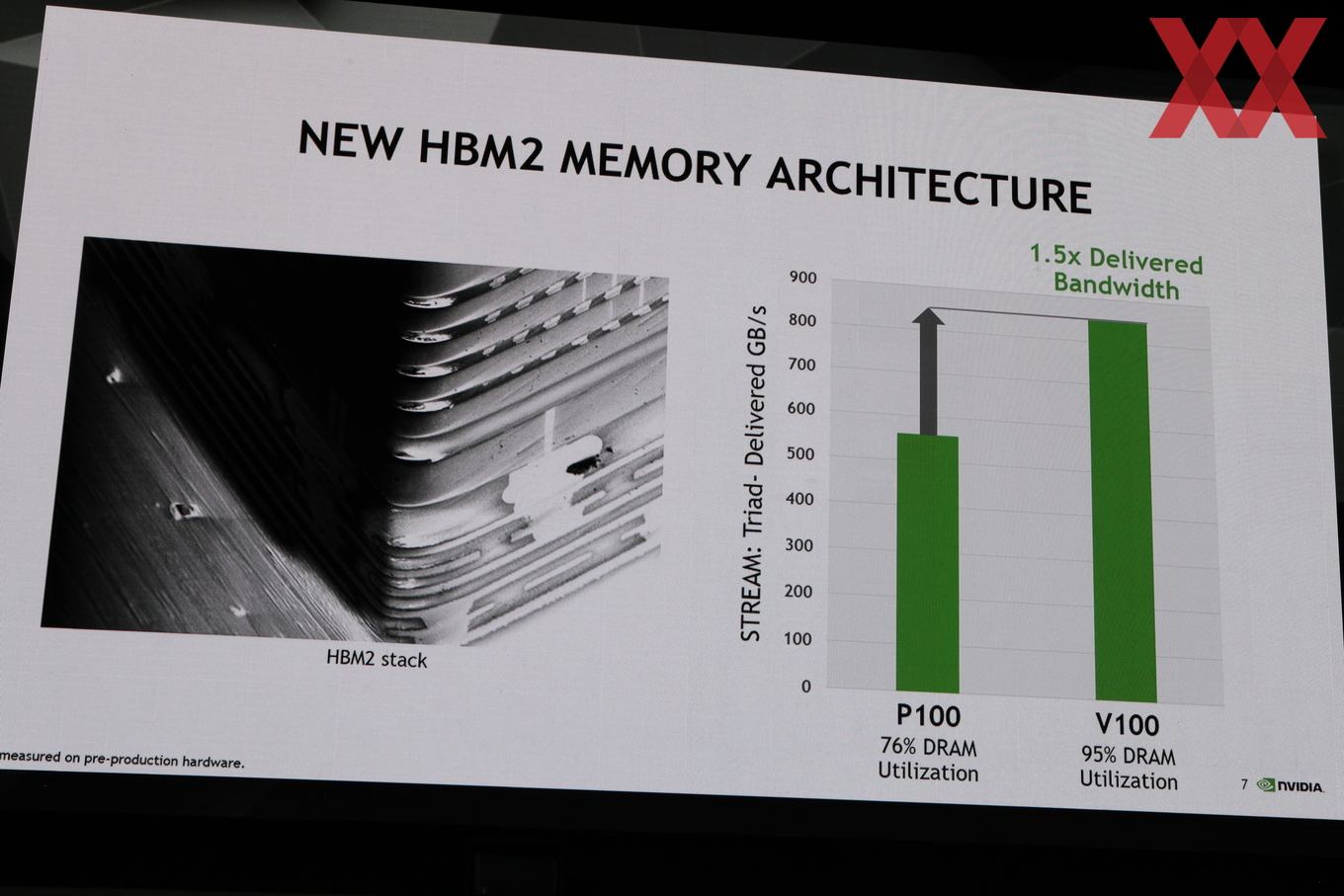

Zur komplexen Fertigung gehört aber nicht nur die GPU selbst, sondern auch Speicher und Interposer. Der Interposer nimmt bei einem solchen Package wie GV100 mit High Bandwidth Memory einen besonders wichtigen Part ein, denn über den Interposer wird die Verbindung zwischen GPU und Speicher-Chips hergestellt. Aufgrund der Größe der GPU ist die Fertigung des Interposers ebenfalls eine große Herausforderung und NVIDIA musste sich eines Tricks bedienen, um den Interposer in dieser Form fertigen zu können.

Um die zu belichtende Fläche nicht zu groß werden zu lassen, bzw. um die dazugehörige Maske möglichst klein zu halten, teilt NVIDIA, bzw. TSMC den Interposer in zwei Teile auf. Diese werden dann getrennt gefertigt und zusammengeführt.