Werbung

Der zunehmende Bedarf an 2,5- und 3D-Packaging-Technologien geht an SK Hynix nicht vorbei. Dazu hat man sich nun bei der Xperi Corporation bedient und mit dem eher unbekannten Technologie-Unternehmen ein Lizenzabkommen geschlossen, welches die DBI Ultra getaufte Interconnect-Technik umfasst. Entwickelt wurde die Technik jedoch nicht von Xperi selbst, sondern von Invensas.

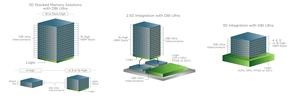

DBI Ultra soll es ermöglichen, bis zu 16 Speicherlayer übereinander zu stapeln. In dieser Form kommt die Technik vor allem für HBM zum Einsatz. In Frage kommen außerdem DRAM-Layer, die bis auf vier Ebenen gestapelt werden können.

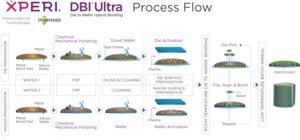

Das Problem der Stapelung solcher Speicher ist nicht die physikalische Umsetzung als solches, sondern vielmehr die Verbindung zwischen den einzelnen Layern. Wurden solche Verbindungen bisher meist über eine Art BGA aus Kupfer hergestellt, limitiert diese Technik bei 625 Verbindungen pro Qudratmillimeter. Bei den aktuellen Ryzen-Prozessoren von AMD liegt der Bumb Pitch, also der Abstand zwischen den tausenden BGAs, bei nur noch 130 µm. Dies ist für mehrere tausend Verbindungen bei den kleinen Speicherchips aber viel zu groß und ermöglicht zu wenige Verbindungen.

DBI Ultra hingegen soll 100.000 bis 1.000.000 Verbindungen pro Qudratmillimeter möglich machen. Durch die geringere Höhe der Verbindungen wird zudem die Z-Heigt, also die Höhe der Chips reduziert und macht damit erst Speicherchips mit bis zu 16 Lagen möglich. Ein Underfill ist ebenfalls nicht mehr notwendig, denn es müssen keine Zwischenräume zwischen den Kupfer-Pillars aufgefüllt werden.

Ein weiterer Vorteil von DBI Ultra soll die Tatsache sein, dass es in der Fertigung keine hohen Temperaturen benötigt. Daher soll auch die Ausbeute in der Fertigung recht hoch sein, weil zu hohe Temperaturen zu Schäden an den Speicherlayern führen können.

SK Hynix spricht noch nicht über konkrete Produkte, die DBI Ultra einsetzen werden. 3DS DRAM und HBM sind sicherlich die heißesten Kandidaten für den Einsatz der Interconnect-Technik. DBI Ultra scheint für SK Hynix ausschließlich im Zusammenspiel mit Speicherchips interessant zu sein. Damit ließen sich aber auch Chipdesigns im 2,5D-Verfahren herstellen.

Alle großen Chiphersteller und Fertiger arbeiten derzeit an aktuellen und künftigen Technologien für die Fertigung von solchen Interconnect-Verbindungen und den dazugehörigen Protokollen. Bei TSMC hören diese Entwicklungen auf die Namen Low-voltage-In-Package-Interconnect (LIPINCON) und Chip-on-Wafer-on-Substrate (CoWoS). Intel bringt mit Co-EMIB die EMIB (Embedded Multi Die Interconnect Bridge) und Foveros unter einen Hut.