Werbung

Anfang April machte Intel die Cascade-Lake-Generationen bei den Xeon-Prozessoren offiziell. Diese verwenden die Purley-Plattform auf Basis des Sockel LGA3647, die schon mit den Skylake-SP/AP-Modellen zum Einsatz gekommen ist. Doch es gibt Änderungen in der Architektur, vor allem aber im Speicher-Ökosystem, die Cascade-Lake-Xeons in zahlreichen Bereichen besser aussehen lassen sollen. Wir haben zwei Xeon Platinum 8280 gegen die direkten Vorgänger antreten lassen und dabei verschiedene Anwendungsszenarien angeschaut.

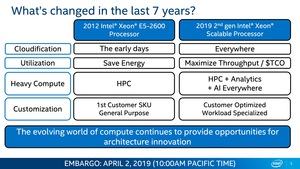

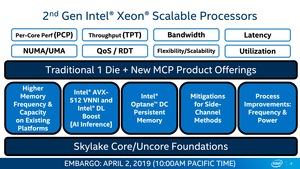

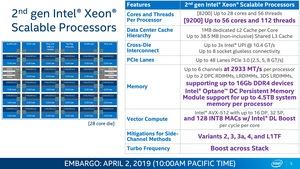

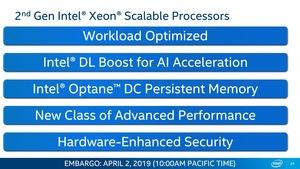

Mit den Xeon-Scalable-Prozessoren der zweiten Generation ändert Intel in gewisser Art und Weise die Marschrichtung der Xeon-Reihe. Während Skylake-SP noch klar auf die klassische Compute-Leistung ausgelegt war und die Xeon-Phi-Beschleuniger oder angehängte FPGAs die Sonderfälle abdeckten, bietet die Cascade-Lake-Architektur in vielerlei Hinsicht Änderungen, die solche Speziallösungen überflüssig machen. Die Cascade-Lake-Xeons sind deutlich breiter aufgestellt und bieten für zahlreiche Bereiche des Servereinsatzes spezielle Lösungen, die aber allesamt auf der gleichen Plattform basieren.

Die neuen Prozessoren

Alle neuen Modelle haben wir im ausführlichen Bereich zum Start der Xeon-Scalable-Prozessoren der zweiten Generation aufgeführt.

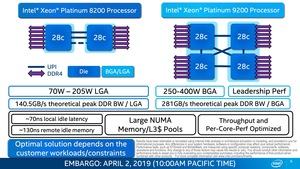

Auch wenn Cascade Lake gegenüber Skylake ein Wechsel in der Architektur und Fertigung bedeutet, so sind sich beiden Generationen im Hinblick auf die Hardware doch sehr ähnlich. Intel lässt die Cascade-Lake-SP-Prozessoren in drei Die-Größen fertigen. Der LCC-Die (Low Core Count) kommt im R1-Stepping und bietet bis zu acht Kerne. Für die größeren Modelle fertigt Intel den HCC-Die (High Core Count) mit bis zu 18 Kernen im L1-Stepping. Für bis zu 28 Kerne sieht Intel das B1-Stepping des XCC-Dies (Extreme Core Count) vor.

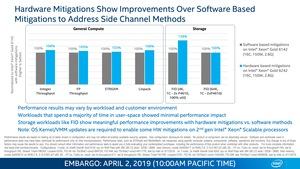

Gefertigt werden die Prozessoren weiterhin in 14 nm. Intel macht keinerlei Angaben über die Anzahl der Transistoren oder die Die-Größe. Der LCC-Die ist etwa 322 mm² groß, ein HCC-Die bringt es auf 484 mm² und ein XCC-Die auf 698 mm². Es dürfte kleinere Änderungen gegenüber der Skylake-SP-Generation im Hinblick auf die Anzahl der Transistoren und auch die Die-Größe geben, denn die Integration der VNNI-Unterstützung sowie die Hardware-Mitigationen gegen Sidechannel-Attacken zieht Änderungen auf Transistorebene nach sich.

Im Vergleich zu den Skylake-Vorgängern spricht Intel von einem Leistungsplus im Bereich von Faktor 1,6. Wenn man sich die einzelnen Modelle etwas genauer anschaut und mit den Vorgängern vergleicht, hebt Intel aber nicht nur den Takt leicht an, sondern spendiert den neuen Modellen auch mehr Kerne. Hatte der Intel Xeon 6130 derer nur 16, sind es beim Xeon 6230N nun 20. Analog lässt sich dies für einige weitere Modellvarianten feststellen. Durch die leicht verbesserte Fertigung hebt Intel den Takt um 200 bis 300 MHz an.

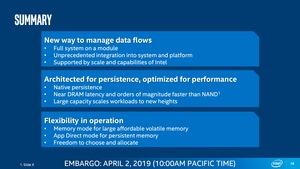

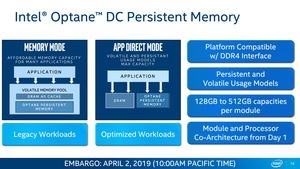

Optane DC Persistent Memory

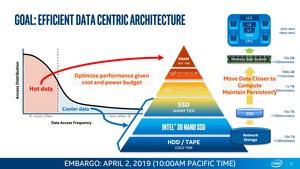

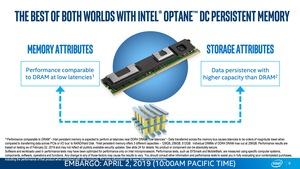

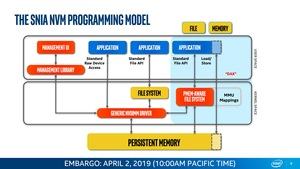

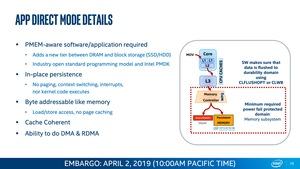

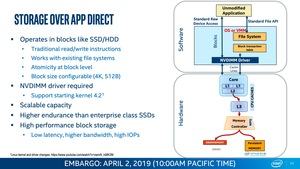

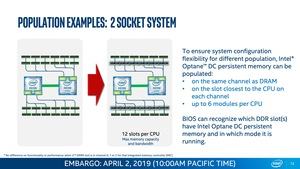

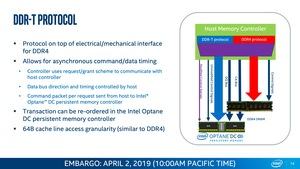

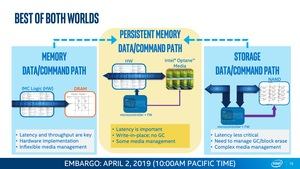

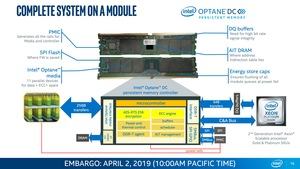

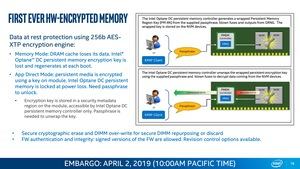

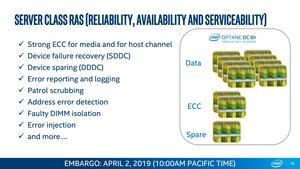

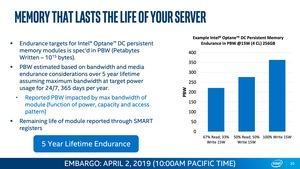

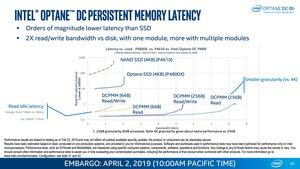

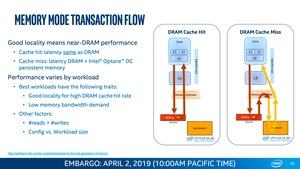

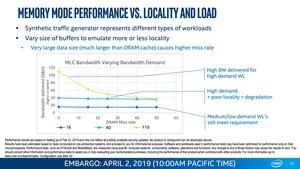

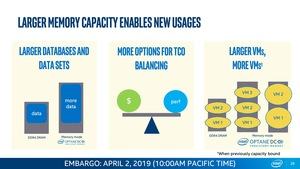

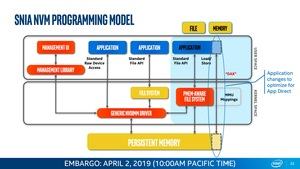

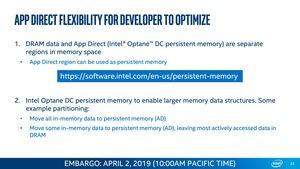

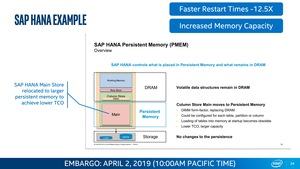

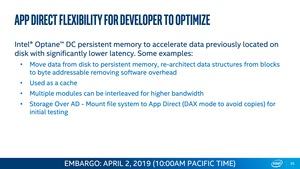

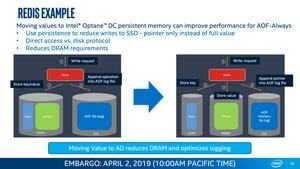

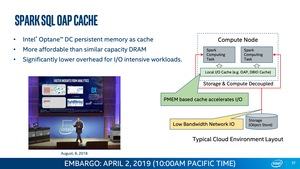

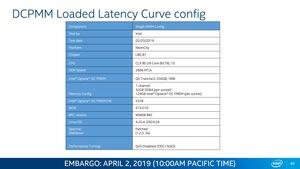

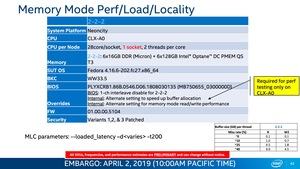

Ein wichtiger Faktor bei den Xeon-Scalable-Prozessoren der zweiten Generation ist die erstmalige Verwendung von Optane DC Persistent Memory. Bereits seit einigen Monaten macht Intel deutlich, dass die Verwendung von Optane DC Persistent Memory eine zentrale Rolle für die Cascade-Lake-Xeons spielen wird.

Die Purley-Plattform war von Beginn an darauf ausgelegt, mit diesem neuen Speicher zu arbeiten. Offenbar hatte Intel auch schon mit den Skylake-Xeons entsprechende Pläne, verwendete sie aber letztendlich nur als Entwicklungs-Plattform für den neuen Speicher. Viele Server und Mainboards verfügen bereits über die entsprechende Anzahl an DIMM-Steckplätzen, um die zusätzlichen Module für den Optane DC Persistent Memory aufzunehmen.

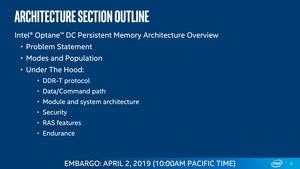

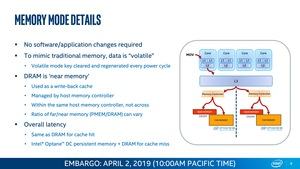

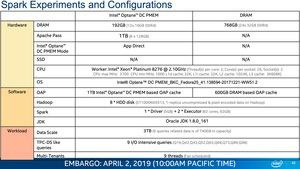

Um weitere technische Details zur Funktionsweise und dem Aufbau von Optane DC Persistent Memory zu erfahren, empfehlen wir abermals unseren Artikel zum Start der Xeon-Scalable-Prozessoren der zweiten Generation. Hier gehen wir auf die Bestückung und die Betriebsmodi von Optane DC Persistent Memory ein. Da uns aber kein solcher Speicher zur Verfügung stand, basieren unsere Erfahrungen rein auf dem Betrieb mit klassischem DRAM.

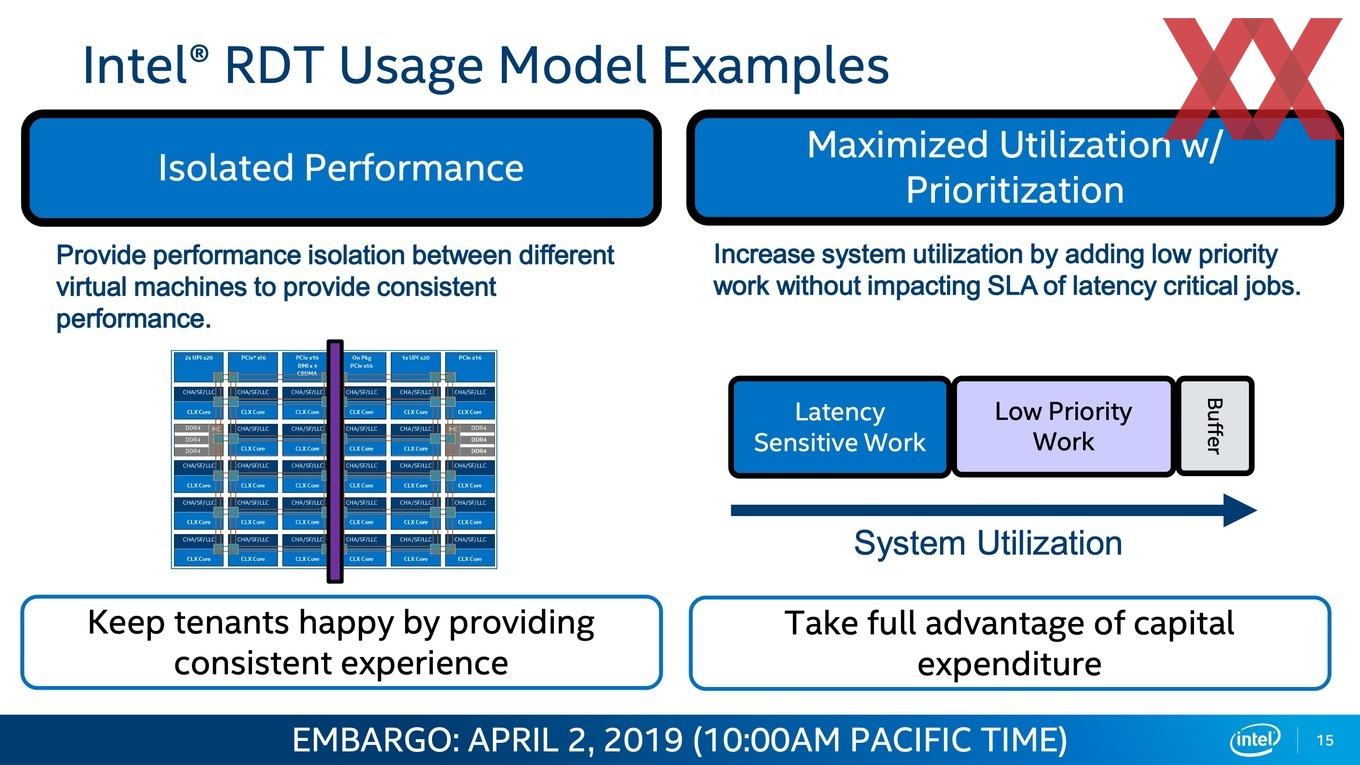

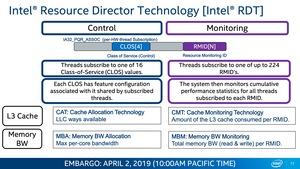

Resource Director und Speed Select

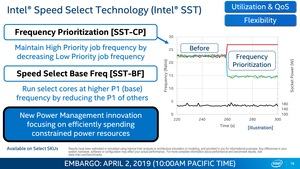

Über die Resource Director und Speed Select Technology können die Cascade-Lake-Prozessoren besser an den jeweiligen Workload angepasst werden. Diese Steuerung findet im Falle der Resource Director Technology (RDT) über die Zuweisung per Software statt. Mittels RDT macht es Intel möglich, die zur Verfügung stehenden Ressourcen besser anzupassen. Der Nutzer oder Besitzer der Hardware bzw. des Servers hat die Wahl, ob dessen Ressourcen einem bestimmten Workload exklusiv zur Verfügung stehen oder ob sich diese flexibel zuteilen lassen. Dazu werden die Caches und Speicherbandbreite ständig kontrolliert und können entsprechend zugeteilt werden.

Ziel ist es, die Hardware besser auszulasten und kosteneffektiver zu betreiben. Damit wird aber auch einen Teil der Kontrolle über die Hardware abgegeben. Für Workloads, die auf eine exklusive Leistung angewiesen sind, kann RDT natürlich nicht angewendet werden.

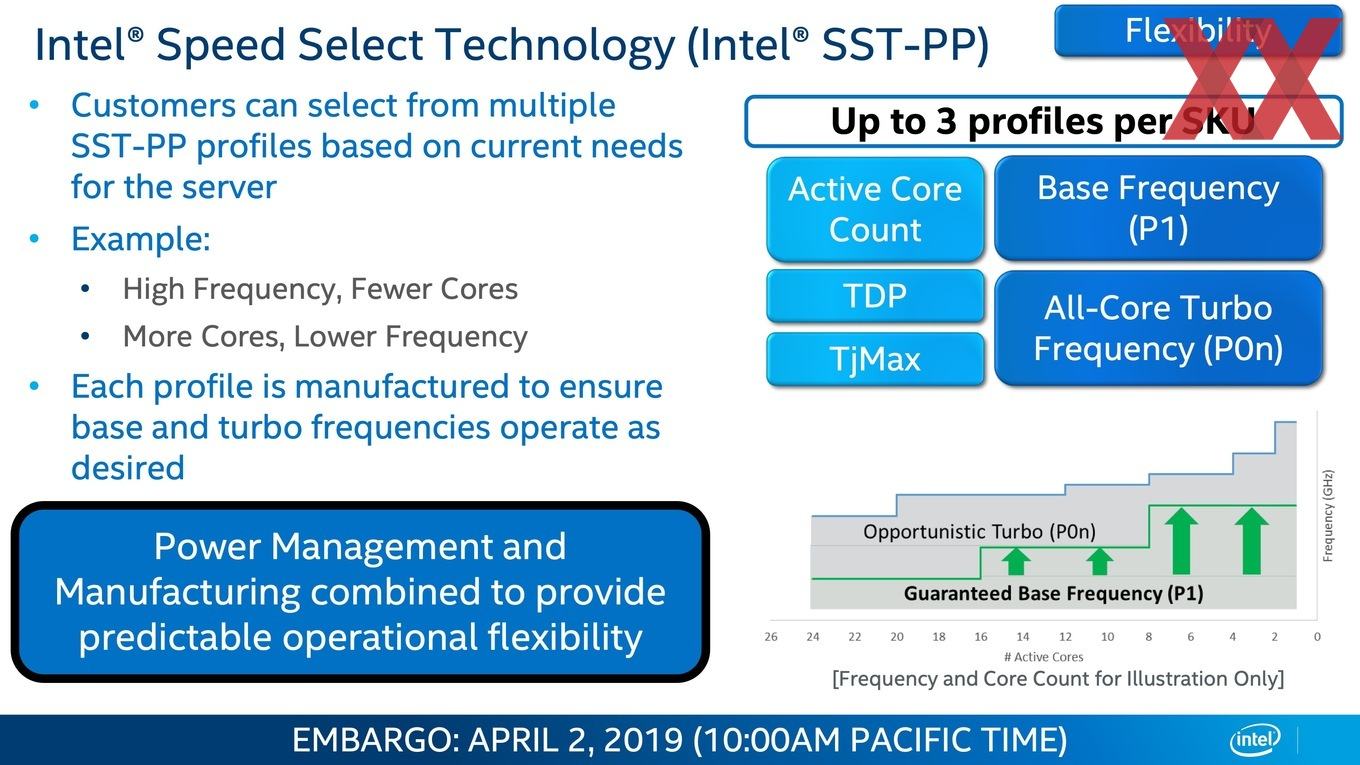

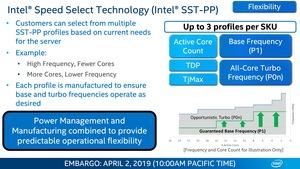

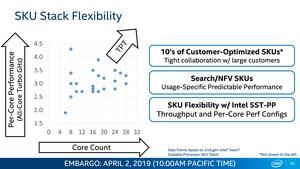

In eine ähnliche Kerbe schlägt auch die Speed Select Technology (SST). Sie erlaubt es einer bestimmten Anzahl an Kernen besonders hoch zu takten. Dafür werden andere heruntergetaktet. Zum Start sieht Intel drei Xeon-Modelle vor (Y-Modelle), die über Profile verschieden angesteuert werden können.

Es gibt aber auch bestimmte Workloads, die sich auf einen gewissen Basistakt verlassen müssen, weil die Berechnung der Leistung entsprechend ausgelegt ist. Per Speed Select Technology lässt sich die Hardware auch hier besser steuern.

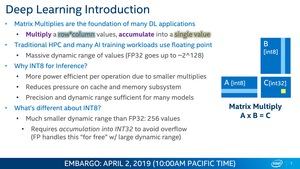

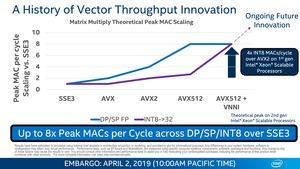

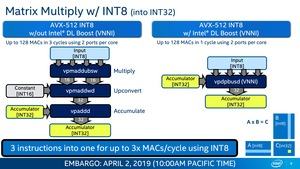

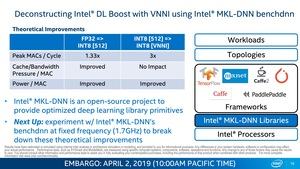

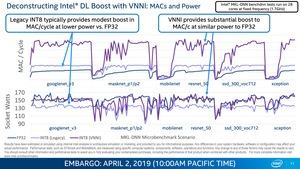

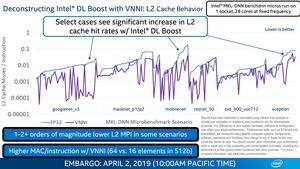

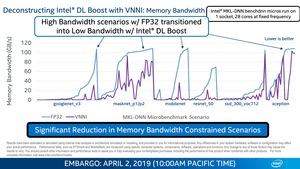

VNNI und DL-Boost

Ein Fokus dieses Artikels wird die Anwendung der neuen Befehlssätze sein. Neben den AVX-512-Instruktionen gehören die Erweiterung der Vector Neural Network Instructions (VNNI) zu den wichtigsten Spezialisierungen der aktuellen Xeon-Prozessoren. Die Rechenleistung für einfache und doppelte Genauigkeit bleibt für die AVX512-Beschleunigung im Vergleich zwischen Skylake und Cascade Lake identisch, durch die Möglichkeit 4x INT Macs/Cycle im Vergleich zu AVX2 auf Skylake-SP zu berechnen, erreichen die Cascade-Lake-Prozessoren eine theoretisch vierfach so hohe Rechenleistung für solche Berechnungen – in der Praxis sollen sie bis zu dreimal schneller sein. Dies werden wir uns anschauen.

Die Anwendung von VNNI in den Xeon-Scalable-Prozessoren macht diese flexibler für den Einsatz im Training und Inferencing von Deep-Learning-Netzwerken. Noch immer aber sind für ein reines Inferencing, also eine Auswertung eines solchen Netzwerks, spezielle Prozessoren besser geeignet. Intel will diesen Bereich mit den Agilex-FPGAs abdecken.