Werbung

Alle namhaften Halbleiterhersteller arbeiten auch an immer neuen Packaging-Kapazitäten, denn neben immer kleineren Dimensionen in der Chipfertigung rückt auch das komplexe Packaging zunehmend in den Fokus. Dies ist auch notwendig, da Multi-Chip-Designs immer schnellere Interconnects erfordern und schnellen HBM anbinden.

TSMC, Samsung, IBM, Intel – alle arbeiten an neuen 2.5D- und 3D-Packaging-Technologien. Häufig greifen diese Unternehmen auf Forschungsarbeiten des imec (Interuniversity Microelectronics Centre) zurück. In der vergangenen Woche hat das imec mit Die-to-Wafer-Hybridbonding und Cu-Interconnect vorgestellt. Diese ist grundsätzlich auch die Basis von AMDs 3D V-Cache bzw. der Technik die TSMC hier zur Anwendung bringt oder Intels Foveros. Intels Lösung kommt dabei aktuell auf einen Bondpad-Abstand von 25 µm, will mit Foveros Direct auf unter 10 µm kommen. TSMCs Technik liegt ebenfalls bei 10 µm, womöglich etwas darunter.

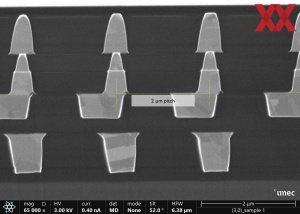

Dass nun von imec auf der ECTC 2024 (IEEE Electronic Components and Technology Conference) als Proof-of-Concept vorgestellte Die-to-Wafer-Hybridbonding soll nun einen Bondpad-Abstand von nur 2 µm erreichen können. Der Die-to-Wafer- Overlay-Fehler, also der Versatz, der eine kritische Größe in diesem Packaging-Verfahren ist, soll bei 350 nm oder weniger liegen.

Das äußerst präzise platzieren der Chips übereinander wird damit erreicht, dass unter anderem die Oberflächen ultrarein sein müssen. Dies beginnt bei der Vereinzelung der Chips, der weiteren Verarbeitung und der Bestückung. Dabei muss aber auch ein möglichst hoher Durchsatz gewährt werden.

In weiteren Schritten arbeitet imec nun in Richtung eines Bondpad-Abstands von 1 µm, bis hinunter zu 400 nm.

Wann und wo wir das neue Verfahren erstmals im Einsatz sehen werden, ist nicht bekannt. Das imec arbeitet mit vielen Halbleiterherstellern zusammen. Auf der ECTC 2024 anwesend waren auch AMD und TSMC.