Werbung

Erst Ende November präsentierte TSMC auf dem Open Innovation Platform eine Weiterentwicklung des Packaging mittels Chip-on-Wafer-on-Substrate (CoWoS). Nun verkündet Broadcom eine Weiterentwicklung seines Packaging mittels 3.5D eXtreme Dimension System in Package (3.5D XDSiP). 3.5D XDSiP verwendet dabei CoWoS von TSMC.

Das, was TSMC präsentierte, soll ab 2027 ein CoWoS-Packaging mit Chiplets, gefertigt in A16, zusammen mit zwölf HBM4-Stacks ermöglichen. Broadcoms 3.5D XDSiP integriert bis zu 6.000 mm² an Chipfläche und ebenfalls bis zu 12 HBM-Chips. Im Zusammenhang mit XDSiP neu ist, dass Broadcom hier eine Face-to-Face-Verbindung (F2F) zum Einsatz bringt. Gegenüber einem Face-to-Back-Ansatz (F2B) können die einzelnen Verbindungen zwischen den Chips dichter zusammengepackt werden, was die Leistungsaufnahme der Verbindung reduziert und den Durchsatz des Interconnects erhöht. Für die Verbindung zwischen den Chips wird ein Hybrid Copper Bonding (HCB) verwendet. Auf TSVs kann für die direkte Verbindung der Chips untereinander verzichtet werden. Diese sind allerdings noch im Back-end der Chips vorhanden, werden aber nicht mehr bis auf die oberste Metallschicht (M0) durchgebrochen.

Broadcom stellt seinen Kunden einen eigens entwickelten Design-Prozess und ein Automatisierungsmethodik zur Verfügung, die auf branchenüblichen Werkzeugen aufgebaut ist. Die notwendige IP im Package-Prozess (SerDes, HBM-Speicherinterface und die des Die-to-Die Interconnects) werden von Broadcom zur Verfügung gestellt.

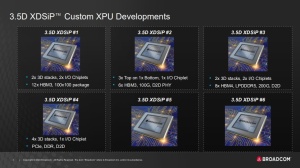

In einigen Beispielen nennt Broadcom mögliche Konstellationen für Packages mit 3.5D XDSiP. Diese sehen Packages mit einer Außenkante von bis zu 100 x 100 mm vor. Kombiniert werden können verschieden große Compute-Chiplets mit darauf gestapeltem Speicher, I/O-Chiplets, (LP)DDR-Controllern, Netzwerkcontrollern und HBM-Chips.

Bis die ersten Chips mit 3.5D-XDSiP-Technologie auf den Markt kommen werden, wird es allerdings noch mindestens zwei Jahre dauern. Vor 2026 ist damit nicht zu rechnen.