News und Artikel durchsuchen

{{#data.error.root_cause}}

{{/data.error}}

{{^data.error}}

{{#texts.summary}}

[{{{type}}}] {{{reason}}}

{{/data.error.root_cause}}{{texts.summary}} {{#options.result.rssIcon}} RSS {{/options.result.rssIcon}}

{{/texts.summary}} {{#data.hits.hits}}

{{#_source.featured}}

FEATURED

{{/_source.featured}}

{{#_source.showImage}}

{{#_source.image}}

{{/_source.image}}

{{/_source.showImage}}

{{/data.hits.hits}}

{{{_source.title}}} {{#_source.showPrice}} {{{_source.displayPrice}}} {{/_source.showPrice}}

{{#_source.showLink}} {{/_source.showLink}} {{#_source.showDate}}{{{_source.displayDate}}}

{{/_source.showDate}}{{{_source.description}}}

{{#_source.additionalInfo}}{{#_source.additionalFields}} {{#title}} {{{label}}}: {{{title}}} {{/title}} {{/_source.additionalFields}}

{{/_source.additionalInfo}}

CoWoS

-

Broadcom 3.5D XDSiP: TSMCs CoWoS als Basis für Broadcom’s 3.5D-Plattform

Erst Ende November präsentierte TSMC auf dem Open Innovation Platform eine Weiterentwicklung des Packaging mittels Chip-on-Wafer-on-Substrate (CoWoS). Nun verkündet Broadcom eine Weiterentwicklung seines Packaging mittels 3.5D eXtreme Dimension System in Package (3.5D XDSiP). 3.5D XDSiP verwendet dabei CoWoS von TSMC. Das, was TSMC präsentierte, soll ab 2027 ein CoWoS-Packaging mit Chiplets, gefertigt in A16, zusammen mit... [mehr]

Erst Ende November präsentierte TSMC auf dem Open Innovation Platform eine Weiterentwicklung des Packaging mittels Chip-on-Wafer-on-Substrate (CoWoS). Nun verkündet Broadcom eine Weiterentwicklung seines Packaging mittels 3.5D eXtreme Dimension System in Package (3.5D XDSiP). 3.5D XDSiP verwendet dabei CoWoS von TSMC. Das, was TSMC präsentierte, soll ab 2027 ein CoWoS-Packaging mit Chiplets, gefertigt in A16, zusammen mit... [mehr] -

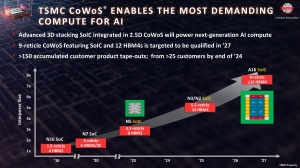

Interposer mit 12x HBM4: TSMC CoWoS soll ab 2027 riesige Packages ermöglichen

Auf dem Open Innovation Platform (OIP) Forum sprach TSMC über seine zukünftigen Pläne hinsichtlich des Packaging, genauer dem Chip-on-Wafer-on-Substrate (CoWoS) und definierte dabei die bisherigen Ziele zur Größe des verwendeten Interposer etwas genauer. Aktuell wird das CoWoS-Packaging im Bereich des dreifachen, des sogenannten Reticle-Limits limitiert, also der maximalen Größe, in der ein monolithischer Chips gefertigt werden kann. In... [mehr]

Auf dem Open Innovation Platform (OIP) Forum sprach TSMC über seine zukünftigen Pläne hinsichtlich des Packaging, genauer dem Chip-on-Wafer-on-Substrate (CoWoS) und definierte dabei die bisherigen Ziele zur Größe des verwendeten Interposer etwas genauer. Aktuell wird das CoWoS-Packaging im Bereich des dreifachen, des sogenannten Reticle-Limits limitiert, also der maximalen Größe, in der ein monolithischer Chips gefertigt werden kann. In... [mehr] -

TSMC: Aggressiver Ausbau der Advanced Packaging-Einrichtungen für KI-Chips

Einem Bericht des Taiwan Economic Daily zufolge, möchte der taiwanesische Chiphersteller TSMC seine Kapazitäten für das Advanced Packaging, in diesem Fall das CoWoS-Packaging, kurz für Chip-on-Wafer-on-Substrate, noch stärker ausbauen. Nötig machen diese Ambitionen die anhaltend hohe Nachfrage von Technologieunternehmen wie NVIDIA und AMD nach KI-Produkten. Zurzeit ist TSMC nicht in der Lage, diese angemessen zu befriedigen. Obwohl TSMC... [mehr]

Einem Bericht des Taiwan Economic Daily zufolge, möchte der taiwanesische Chiphersteller TSMC seine Kapazitäten für das Advanced Packaging, in diesem Fall das CoWoS-Packaging, kurz für Chip-on-Wafer-on-Substrate, noch stärker ausbauen. Nötig machen diese Ambitionen die anhaltend hohe Nachfrage von Technologieunternehmen wie NVIDIA und AMD nach KI-Produkten. Zurzeit ist TSMC nicht in der Lage, diese angemessen zu befriedigen. Obwohl TSMC... [mehr] -

TSMC: Erhöhte Produktion für NVIDIA macht Kapazitätsausbau notwendig

Entgegen dem Trend waren bis zuletzt in den Auftragsbüchern von TSMC kaum Auftragslücken zu finden. Das Unternehmen ist derzeit noch gut ausgelastet und der derzeitige Boom von Künstlicher Intelligenz und High-Performance-Computing lässt sogar die Kapazitäten von TSMC an ihre Grenzen kommen. Die Nachfrage nach fortschrittlichen Prozesstechnologien führender Chiphersteller – allen voran nach Grafikprozessoren wie dem A100 und dem H100 von... [mehr]

Entgegen dem Trend waren bis zuletzt in den Auftragsbüchern von TSMC kaum Auftragslücken zu finden. Das Unternehmen ist derzeit noch gut ausgelastet und der derzeitige Boom von Künstlicher Intelligenz und High-Performance-Computing lässt sogar die Kapazitäten von TSMC an ihre Grenzen kommen. Die Nachfrage nach fortschrittlichen Prozesstechnologien führender Chiphersteller – allen voran nach Grafikprozessoren wie dem A100 und dem H100 von... [mehr] -

TSMC arbeitet mit neuen Materialen und an neuen Packaging-Technologien

Neben den neusten Fertigungstechnologien hat TSMC auf dem Technology Symposium über die weitere Entwicklung und Fortschritte in der Materialforschung und dem Packaging gesprochen. Neue Materialien und eine fortschreitende Weiterentwicklung in der Integration von mehreren Chips in 2.5D- und 3D-Stapeln sollen in den kommenden Jahren die Rechenleistung weiter anwachsen lassen. Eines der Zauberworte sind in der Materialforschung die Nanosheets und... [mehr]

Neben den neusten Fertigungstechnologien hat TSMC auf dem Technology Symposium über die weitere Entwicklung und Fortschritte in der Materialforschung und dem Packaging gesprochen. Neue Materialien und eine fortschreitende Weiterentwicklung in der Integration von mehreren Chips in 2.5D- und 3D-Stapeln sollen in den kommenden Jahren die Rechenleistung weiter anwachsen lassen. Eines der Zauberworte sind in der Materialforschung die Nanosheets und... [mehr] -

CoWoS: TSMCs 1.700-mm²-Interposer nimmt 5-nm-Chips auf

TSMC hat gemeinsam mit Broadcom die eigenen Interposer- und Interconnect-Technologie CoWoS (Chip-on-Wafer-on-Substrate) in die Produktionsreife gebracht und wird in dieser Zusammenarbeit wohl bald konkrete Produkte ankündigen. Die Besonderheit in der Zusammenarbeit liegt in der Größe des gemeinsam entwickelten Interposers. Dieser kommt auf eine Fläche von 1.700 mm² und soll neben in 5 nm (N5) gefertigten Chips schnellen HBM... [mehr]

TSMC hat gemeinsam mit Broadcom die eigenen Interposer- und Interconnect-Technologie CoWoS (Chip-on-Wafer-on-Substrate) in die Produktionsreife gebracht und wird in dieser Zusammenarbeit wohl bald konkrete Produkte ankündigen. Die Besonderheit in der Zusammenarbeit liegt in der Größe des gemeinsam entwickelten Interposers. Dieser kommt auf eine Fläche von 1.700 mm² und soll neben in 5 nm (N5) gefertigten Chips schnellen HBM... [mehr] -

TSMC plant neue Packaging-Technologien und 1,4-nm-Fertigung

In den vergangenen Tagen drehte sich in Kalifornien auf der Hotchips 2019 vieles um die zukünftigen Lösungen in der Fertigung und letztendlich auch Ausführung moderner Fertigungstechnologien. Unter anderem gezeigt wurde ein riesiger Chip mit einer Fläche von 46.225 mm², der 400.000 Kerne enthalten soll. Intel zeigte seine AI-Beschleuniger NNP-I und NNP-T in allen Details und AMD hat einige weitere Fakten zu den EPYC-Prozessoren der zweiten... [mehr]

In den vergangenen Tagen drehte sich in Kalifornien auf der Hotchips 2019 vieles um die zukünftigen Lösungen in der Fertigung und letztendlich auch Ausführung moderner Fertigungstechnologien. Unter anderem gezeigt wurde ein riesiger Chip mit einer Fläche von 46.225 mm², der 400.000 Kerne enthalten soll. Intel zeigte seine AI-Beschleuniger NNP-I und NNP-T in allen Details und AMD hat einige weitere Fakten zu den EPYC-Prozessoren der zweiten... [mehr] -

TSMC zeigt riesiges Chiplet-Design mit ebenso gigantischem Interposer

TSMC reiht sich in die Reihe derjenigen ein, für die Moore's law noch lange nicht am Ende ist. Eine Kombination aus voranschreitenden Fertigungstechniken und neuen Design-Ansätzen soll dafür sorgen, dass wir noch über Jahre hinweg regelmäßige Steigerungen in der Packdichte und Rechenleistung sehen werden – so zumindest sieht dies Godfrey Cheng, Leiter des Marketing bei TSMC in einem Blogpost. Dabei gibt Cheng erstaunliche Einblicke... [mehr]

TSMC reiht sich in die Reihe derjenigen ein, für die Moore's law noch lange nicht am Ende ist. Eine Kombination aus voranschreitenden Fertigungstechniken und neuen Design-Ansätzen soll dafür sorgen, dass wir noch über Jahre hinweg regelmäßige Steigerungen in der Packdichte und Rechenleistung sehen werden – so zumindest sieht dies Godfrey Cheng, Leiter des Marketing bei TSMC in einem Blogpost. Dabei gibt Cheng erstaunliche Einblicke... [mehr] -

TSMC zeigt eigene Chiplet-Techniken für ARM-HPC-Prozessoren

Die Zukunft scheint den Chiplet-Designs zu gehören. AMD wird dazu mit den Ryzen-Prozessoren der dritten Generation und den EPYC-Prozesoren der zweiten Generation erste Produkte auf den Markt bringen und die Erfahrungen, die AMD bei den Zen-Prozessoren gemacht hat, will man in zukünftigen RDNA-Architekturen für die Grafikkarten umsetzen. Auch Intel arbeitet bei den Prozessoren in diese Richtung und das, was Intel bisher... [mehr]

Die Zukunft scheint den Chiplet-Designs zu gehören. AMD wird dazu mit den Ryzen-Prozessoren der dritten Generation und den EPYC-Prozesoren der zweiten Generation erste Produkte auf den Markt bringen und die Erfahrungen, die AMD bei den Zen-Prozessoren gemacht hat, will man in zukünftigen RDNA-Architekturen für die Grafikkarten umsetzen. Auch Intel arbeitet bei den Prozessoren in diese Richtung und das, was Intel bisher... [mehr]