Werbung

Neben der fortschreitenden Entwicklung in der Fertigung der einzelnen Chips ist TSMC in den vergangenen Jahren mindestens ebenso ambitioniert und erfolgreich, wenn es um das Packaging geht. Auf dem Technology Symposium 2025 präsentierte man einen Fahrplan für die kommenden Jahre.

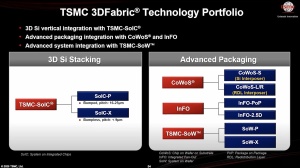

Beim Packaging steht TSMC auf zwei Grundpfeilern, die sich wiederum in weiteren Technologieblöcke aufteilen. Zum Advanced Packaging gehören CoWoS (Chip on Wafer on Substrate), InFO (Integrated Fan-Out) und TSMC-SoW (System on Wafer). Beispiele für die Anwendung von System on Wafer ist beispielsweise der Cerebras. Mit SoW-P und SoW-X soll es hier entsprechende Weiterentwicklungen geben, die analog zu den Verbesserungen in den Fertigungsschritten zu sehen sind. InFO kennen wir als direkte Verbindung zwischer Chips über eine Art Brücke. AMD nutzt dies beispielsweise bei den Instinct-Beschleunigern. Mit InFO-POP (Package on Package) und InFO-2.5D will TSMC weitere Variationen anbieten, welche im Chipdesign mehr Flexibilität bereitstellen – aber auch deutlich komplexer werden.

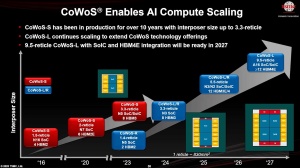

Das Brot-und-Butter-Geschäft ist und bleibt CoWoS. Ein oder mehrere Compute-Chiplets kombiniert mit aktuell bis zu acht HBM-Chips beschreiben den groben Aufbau. CoWoS-S startete 2016 einmal mit einem 1,5 Reticle-Limit (etwa 830 mm² *1,5) für die Größe des Interposers. Eine Fertigung in N16 und vier HBM-Chips waren damals das Limit. Sein aktuelles Limit erreicht CoWoS-S bei einen 3,3-fachen Reticle-Limit und acht HBM-Chips mit einer Fertigung der Compute-Chips in N5 oder N4.

CoWoS-R stellt eine Weiterentwicklung von CoWoS-S dar und bietet dabei vor allem höhere Interconnect-Bandbreiten. Mit einem Reticle-Limit von ebenfalls dem 3,3-fachen wird hier inzwischen der Einsatz von in N3 gefertigten Chips ermöglicht.

Danach soll CoWoS-L übernehmen, wenngleich je nach Notwendigkeit und Auftraggeber auch weiter ein CoWoS-R angeboten und weiterentwickelt wird. Große in N3 und N2 gefertigte Compute-Chiplets, dazu einige I/O-Chiplets und bis zu 12 HBM3E/HBM4-Chips können hier auf einem Package mit dem 5,5-fachen Reticle-Limit untergebracht werden. Diese gut 4.500 mm² großen Chips werden vor allem für KI-Beschleuniger benötigt. Das was TSMC an schematischer Darstellung aufzeichnet, erinnert nicht von ungefähr an die KI-Chips von AMD und NVIDIA. AMDs Instinct MI450X und NVIDIAs Vera Rubin wird an dieser Stelle der Weg für 2026 geebnet. 2027 ist dann CoWoS-L mit in A16 gefertigten Chips, einem 9,5-fachen Reticle-Limit und 12 oder mehr HBM-Chips vorgesehen. Vera Ultra von NVIDIA lässt grüßen!

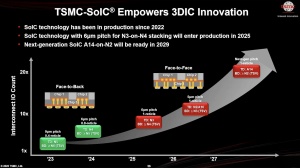

Aber nicht nur die Packages werden immer größer, sondern auch die einzelnen Chips immer komplexer – und das nicht nur aufgrund der immer feineren Fertigung. Mit dem 3D V-Cache und der Platzierung eines SRAM-Chips über und aktuell unter einem Compute-Chiplet hat TSMC gezeigt, wohin der Weg gehen wird. Chips in N5 auf N6, aktuell N4 auf N5 mit einem Bumb Pitch (Abstand der Kontakte/TSVs) von 6 µm durchlaufen aktuell die Packaging-Hallen bei TSMC. Die Chips, auf denen TSMC ein SoIC ermöglicht, wurden von 0,4 auf das 0,8-fache des Reticle-Limits immer größer.

Ab diesem Jahr will TSMC ein SoIC von N3 auf N4 starten. Die Chips können dabei eine Größe von theoretisch jeweils 830 mm² erreichen. Beschränkungen wie groß der oben aufliegende Chip sein darf, gibt es ab hier nicht mehr. Stattdessen geht TSMC 2026/27 zu N2/A16 auf N3 über und reduziert den Bump Pitch auf 5 µm. Später wird dann A14 auf N2 folgen – die zu erwartende Weiterentwicklung.