Werbung

Auch wenn HBM (High Bandwidth Memory) bei Endkundenhardware kaum mehr eine Rolle spielt, so ist dieser schnelle Speichertyp aus dem Datacenter und hier der Beschleunigerhardware kaum mehr wegzudenken. Entsprechend schritt die Entwicklung in den vergangenen 24 Monaten schnell voran. Nachdem die ersten Beschleuniger mit HBM3 in diesem Jahr ausgeliefert wurden und werden sollen, soll im kommenden Jahr bereits HBM3E zum Einsatz kommen. In der unten anstehenden Tabelle finden sich ein paar Leistungsdaten zu den HBM-Generationen.

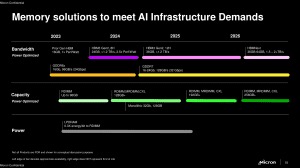

Das, was nach HBM3(E) kommen sollte, war bisher mehr oder weniger unbekannt. Zwar hatte Micron in einer Speicher-Roadmap bereits über HBM Next gesprochen und dort auch Kapazitäten von bis zu 64 GB und Bandbreiten von bis zu 2 TB/s erwähnt, darüber hinaus ist jedoch recht wenig bekannt.

In einem Editorial von SangJoon Hwang, dem EVP und Leiter des DRAM Produkt- und Technologie-Teams bei Samsung, erwähnt dieser erstmals HBM4.

Demnach erwartet man die Einführung von HBM4 bereits 2025, während die Roadmap von Micron eher von 2026 ausgeht.

| HBM-Generation | max. Kapazität | Speicherbandbreite |

| HBM1 | 1 GB | 128 GB/s |

| HBM2 | 8 GB | 256 GB/s |

| HBM2E | 16 GB | 461 GB/s |

| HBM3 | 24 GB | 819 GB/s |

| HBM3E | 24 / 32 GB | 1,2 TB/s |

| HBM4 | - | - |

Aus technischer Sicht wird HBM4 den aktuellen Weg fortsetzen. So werden mehr Speicherlagen gestapelt, um die Kapazität weiter zu steigern. Analog dazu steigt die Speicherbandbreite der einzelnen Speicherstacks – einhergehend mit moderaten Taktsteigerungen. Aber der Takt der Speicherstacks lässt sich nicht so steigern, wie dies für DRAM oder GDDR der Fall ist. Grund hierfür ist bei gestapelten Speicherlagen die Tatsache, dass die Abwärme nur noch schwer abgeführt werden kann.

Für HBM4 soll ein anderer Weg eingeschlagen werden. Von der ersten HBM-Generation bis zu HBM3E kommt ein 1.024 Bit breites Speicherinterface zum Einsatz. Nur über ein solch breites Interface sind die enormen Bandbreiten möglich. Mit HBM4 soll das Speicherinterface auf 2.048 Bit verdoppelt werden. An dieser Stelle sollte man allerdings wissen, dass die Anzahl der physikalischen Verbindungen bereits mit einem 1.024 Bit breiten Interface bei fast 4.000 Pins liegt. Die Strom- und Spannungsversorgung muss ja ebenfalls gewährleistet werden.

Der Packaging-Aufwand wird mit HBM4 also noch einmal deutlich steigen. Damit beschäftigen sich Unternehmen wie Samsung und TSMC aber sicherlich bereits.

Im kommenden Jahr erwartet uns also zunächst einmal Hardware mit HBM3E und man kann erwarten, dass daraufhin die ersten belastbaren Details zu HBM4 ans Tageslicht kommen.