Werbung

Nachdem die Standardisierungsbehörde JEDEC in der vergangenen Woche die Spezifikationen zur 2. Generation des High Bandwidth Memory veröffentlicht hat, kündigt Samsung nun den Start der Massenproduktion von HBM2 an. Neben SK Hynix ist Samsung der zweite Hersteller, der bisher als Fertiger für diesen schnellen Speicher bekannt ist. Micron, ebenfalls ein Big Player in diesem Markt, wird sich vorerst offenbar auf etablierte DRAM-Speichertechnologien konzentrieren bzw. arbeitet mit Intel auch an zukünftigen Lösungen.

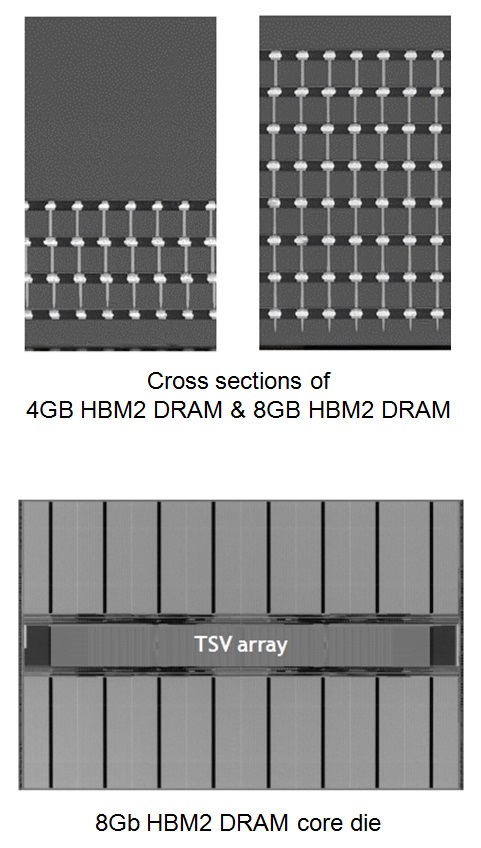

Samsung fertigt die ersten HBM2-Speicherchips in 20 nm und erreicht damit Kapazitäten von 4 GB pro HBM2-Chip. Zusammen mit dem im Oktober des vergangenen Jahres vorgestellten RDIMM mit 128 GB mit TSV-DRAM-Speicherchips sind die HBM2-Speicherchips laut Samsung derzeit die fortschrittlichste TSV-DRAM-Technologie (TSV steht für Through Silicon Via - näheres dazu im Artikel "AMD Fiji: Wie der Interposer HBM und GPU miteinander verbindet").

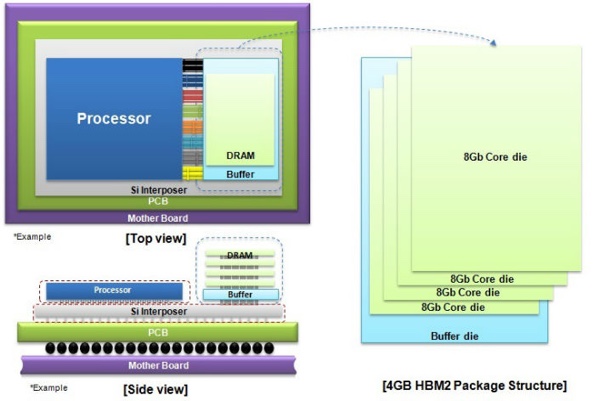

Der Aufbau eines HBM2-Speicherchips von Samsung sieht wie folgt aus: Samsung verwendet einen Buffer-Die und baut darauf vier weitere Speicherschichten mit jeweils 8 GBit auf. 4x 8 GBit ergeben die 32.768 GBit also 4 GB pro Speicherchip. Über Through Silicon Vias und Microbumbs werden die Verbindungen in den Schichten hergestellt. Eine einzige 8-GBit-Layer verfügt dabei über 5.000 TSVs. Dies entspricht der 36fachen im Vergleich zu einem 8-GBit-Chip mit TSVs bei DDR4-Speicher. Dies macht sicherlich auch die Komplexität eines HBM2-Speicherchips deutlich, der dann alleine in den vier Speicherschichten auf mehr als 20.000 TSVs kommt.

Bereits in den JEDEC-Spezifikationen zu HBM2 wurde bekannt, dass diese 2. Generation eine Speicherbandbreite von 256 GB/s pro Speicherchips aufweist. Bei meist vier verwendeten HBM2-Chips auf einem Interposer kann eine GPU somit auf eine Gesamtspeicherbandbreite von 1.024 GB/s kommen. Bei Verwendung von GDDR5-Speicher war meist bei 336,6 GB/s Schluss, mit HBM der 1. Generation waren immerhin 512 GB/s möglich. Pro Pin erreicht HBM2 eine Speicherbandbreite von 9 GB/s, was innerhalb aller DRAM-Speichertechnologien aktuell ein unerreichter Wert ist.

Noch für dieses Jahr plant Samsung die Fertigung von HBM2-Speicherchips mit einer Kapazität von 8 GB. Genaue Angaben zum Datum macht Samsung aber nicht. 4x 8 GB sieht die aktuelle JEDEC-Spezifikation für HBM2 bereits vor. Bei den Consumer-Karten werden wir zum Start der Pascal-GPUs von NVIDIA und Polaris-GPUs von AMD sicherlich zunächst einmal einen maximalen Ausbau von 8 bis 16 GB sehen. Über das Jahr hinweg will Samsung die Fertigungskapazitäten von HBM2 weiter erhöhen, um dem zu erwartenden Bedarf decken zu können.

Die HBM2-Speicherchips von Samsung verfügen außerdem um ein embedded ECC. Dazu sieht Samsung zusätzliche Anschlüsse und Speicherbereiche vor, um den Error Correction Code (ECC) anbieten zu können. Unterstützt auch die GPU, können Schreib- und Lesefehler im Speicher bereits hier erkannt und korrigiert werden. Ein ECC spielt aber nur bei speziellen Anwendungen im wissenschaftlichen Bereich eine Rolle - so zum Beispiel bei NVIDIAs Tesla- und Quadro-Karten und auch AMD bietet bei den FirePro-Modellen eine Unterstützung von ECC an.

Zusammenfassend kann festgehalten werden, dass HBM2 den Grafikkartenherstellern eine doppelt so hohe Speicherbandbreite bei bis zu achtfacher Speicherkapazität zur Verfügung stellt.