Werbung

Unter der Patentnummer "US 2020/0409859 A1" hat AMD gegenüber dem United States Patent and Trademark Office ein weiteres Patent eingereicht, welches sich mit einem Chiplet-Design für GPUs beschäftigt. Wir haben ein solches bereits mehrfach gesehen, auch schon von NVIDIA. Selbst konkrete Umsetzungen gibt es in gewissen Bereichen bereits.

Imagination stellte kürzlich seine neueste GPU-Serie vor, deren BXE-, BXM- und BXT-Serie aus bis zu vier Chiplets besteht. Intel wird in diesem Jahr seine Xe-HP-GPUs auf den Markt bringen, die es aus bis zu vier Chiplets bestehen. Auf dem Architecture Day 2020 zeigte Intel die Skalierung des Chiplet-Designs, welche für bestimmte Anwendungen nahezu linear verlief – für ein Chiplet-Design die idealen Voraussetzungen.

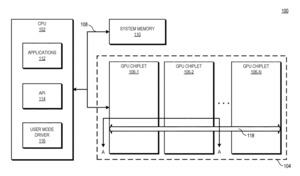

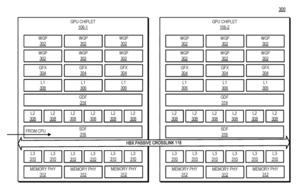

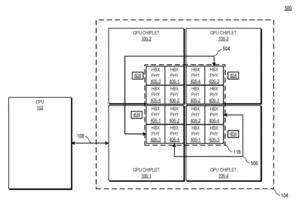

Das Patent zeigt ein typisches Chiplet-Design mit mehreren (fast) identischen Chiplets. Es gibt allerdings ein primäres Chiplet, welches die Daten vom Host-System (CPU, Systemspeicher, etc.) entgegennimmt, bzw. mit diesem kommuniziert. Zwischen den Chiplets werden die Daten über einen passiven HBX (High Bandwidth Crosslink) ausgetauscht. Die entsprechenden HBX-PHYs und HBX-Controller befinden sich innerhalb der Chiplets. Der Crosslink, bzw. die Verteilung der Daten zu und innerhalb der Chiplets sind mit der wichtigste Faktor eines solches Designs. Mit dem Infinity Fabric hat AMD jedoch bereits bewiesen, dass ein schneller Interconnect möglich ist.

Weiterhin auf den Zeichnungen zu erkennen, sind die für eine GPU typischen Komponenten. So führt AMD die mit der RDNA-Architektur eingeführten Workgroup Prozessoren (WGP) auf. Weiterhin muss eine GPU gewisse Fixed Function Units besitzen, die ebenfalls genannt werden. Natürlich gibt es auch einen, bzw. zwei Memory PHYs, also die physikalischen Interfaces für den externen Speicher der GPU.

Zur Speicher-Hierarchie gehören neben dem Grafikspeicher L1-, L2- und L3-Caches. Mit der RDNA-2-Architektur führte AMD den Infinity Cache ein, der 128 MB groß ist und Last Level Cache (LLC) fungiert. Diesen werden wir sicherlich in der RDNA-3-Architektur wiedersehen und mit Auflösungen von 4K und höher würden auch mehr als 128 MB Sinn machen.

Durch ein Einsatz eines primären Chiplets soll sich das Multi-Chip-Design dem Host-System gegenüber als ein monolithischer Chip darstellen. Dazu wird der L3-Cache als kohärenter Speicher ausgelegt. Die CPU adressiert also einen gemeinsamen Speicher. Die Verteilung der Daten überni dann die GPUs selbst. Dies macht es vor allem der Software einfacher, denn sie muss nicht für ein Multi-Chip-Design ausgelegt sein.

Die Fertigung der Chiplets erfolgt wie bei einer jeden GPU. Danach werden zwei oder mehr Chiplets auf einem Interposer aufgebracht. Ein Interconnect verbindet die Chiplets untereinander. Nach außen hin bleibt es bei den bekannten Interface-Technologien wie PCI-Express.

Noch völlig offen ist die Frage, ab wann AMD das neue (und einige weitere) Patent für ein Multi-Chip-Design einsetzen wird. Für die nächste GPU-Generation auf Basis der RDNA-3-Architektur wird dies noch nicht erwartet. Hier dürfte AMD noch auf die Fertigung eines monolithisches Designs in 5 nm setzen. Intel wird in diesem Jahr wohl der erste Hersteller sein, der einen GPU-Beschleuniger im Multi-Chip-Design vorstellen wird. Dabei wird es sich allerdings um eine Datacenter-GPU handeln. Ob auch die Xe-HPG-Architektur für die neue Gaming-GPU-Generation von Intel ein Multi-Chip-Design sein wird, ist noch nicht bekannt.